通常,我们优先解决建立时间违例。Setup slack与逻辑延迟、布线延迟、时钟歪斜和时钟不确定性有关。因此,首先要明确这几个因素中哪个因素对建立时间违例起关键作用。具体的衡量标准可由如下几个数值确定。这也是ug1292第三页的主题。

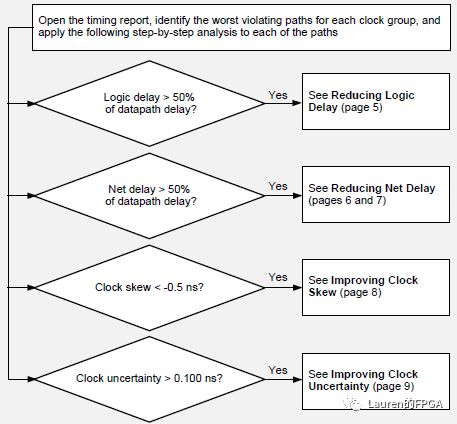

ug1292第三页也给出了建立时间违例分析流程,如下图所示。当逻辑延迟占比超过50%时,要着重降低逻辑延迟;当布线延迟占比超过50%时,要把焦点放在布线延迟上;同时,也要关注一下时钟歪斜和时钟不确定性。当时钟歪斜小于-0.5ns或时钟不确定性大于0.1ns时,两者将成为时钟违例的主要“贡献者”。

图片来源, page 3, ug1292

上述四个数值,无论是在timing report(通过report_timing_summary生成)还是design analysis report(通过report_design_analysis生成)中都有所体现。以timingreport为例,如下图所示,可清晰地显示上述四个数值。

图片来源, page 3, ug1292

注:上述数据只针对UltraScale系列芯片。

-

时钟

+关注

关注

11文章

1953浏览量

134532 -

逻辑

+关注

关注

2文章

834浏览量

30048

原文标题:深度解析ug1292(3)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片设计进阶之路—从CMOS到建立时间和保持时间

DC综合建立时间的关键路径分析的问题?

建立时间和保持时间讨论

快速建立时间的自适应锁相环

线与逻辑、锁存器、缓冲器、建立时间、缓冲时间的基本概念

时延和建立时间在ADC电路中的区别

ug1292深度解析

UG1292使用之初始设计检查使用说明

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量

UltraFast设计方法时序收敛快捷参考指南(UG1292)

深度解析ug1292建立时间违例分析流程

深度解析ug1292建立时间违例分析流程

评论