首先,从理论上讲,Hold Time违例,是因为时钟绕的太远,到达时间太晚。而且综合之后给出的时序报告都是估计值,因此综合之后可以不考虑Hold Time,只考虑Setup Time;即便此时Hold Time违例,我们也不需要去理会。在Place Design之后再去看Hold Time,如果此时Hold Time的违例比较小(比如-0.05ns),还是不需要理会的,因为工具在布线时会修复Hold,但如果Slack太大了,无法修复了,就会牺牲setup来弥补hold。

如果出现了hold的违例,我们首先要分析时序报告,看是不是clock的skew太大了,hold违例一般都是时钟的skew太大导致,如果skew太大,就要检查原因了,是不是时钟路径上有buffer导致的,或者是因为时钟跨SLR这种路径太长导致。如果时钟路径上并没有什么多余的buffer或者逻辑,那使用全局时钟网络带来的skew是最小的。

这里补充一下综合实现的步骤:

synth_design -> opt_design -> place-design -> phys_opt_design -> route_design

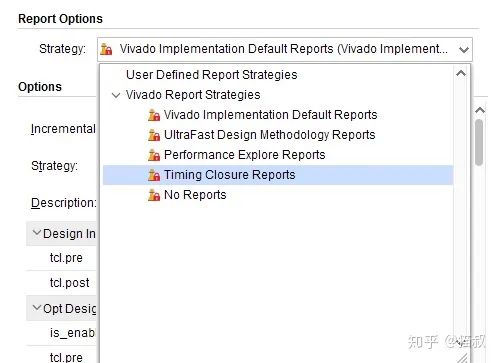

我们可以让工具在每一步执行后都会有时序报告,只需要把Report Options的策略选择为Timing Closure Reports

如果route design之后hold time还是违例,可以使用tcl指令:

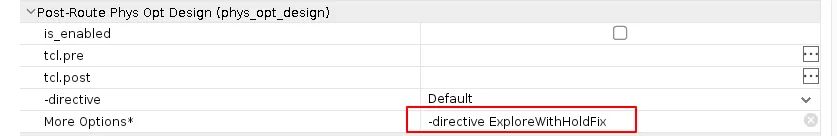

phys_opt_design -directive ExploreWithHoldFix

这个指令会尝试不同的算法来优化hold time违例(其实就是在数据路径上插入LUT增加延迟)

或者在Implementation的时候指定,是一样的效果。

Hold违例解决方法总结如下:

1. 检查违例的时钟是否是在全局时钟网络上,最好是让时钟走全局时钟网络,减小skew

2. 检查时序路径上,避免有时钟BUFFER的级联

3. 插入延迟逻辑,在数据路径上增加逻辑延迟(可以使用ExploreWithHoldFix让工具自动插入,也可以手动修改代码插入)

审核编辑:刘清

-

时钟

+关注

关注

11文章

1953浏览量

134548

原文标题:Hold Time违例,该如何解决

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Setup/Hold Time Problem

【FPGA经典试题】电路模块的setup-time和hold-time是正值还是负值

解释下setup和hold time

请问AD80370中hold up time为负值是为什么?

2018年IC设计企业笔试题01英伟达Nvidia

出现时序违例的原因及解决办法

什么是Setup和Hold时间

Timing收敛 – 如何消除Hold Timing违例

建立时间和保持时间(setup time 和 hold time)

Vivado时序案例分析之解脉冲宽度违例

怎么解决解决Hold Time违例的问题呢

怎么解决解决Hold Time违例的问题呢

评论