report_timing -variation

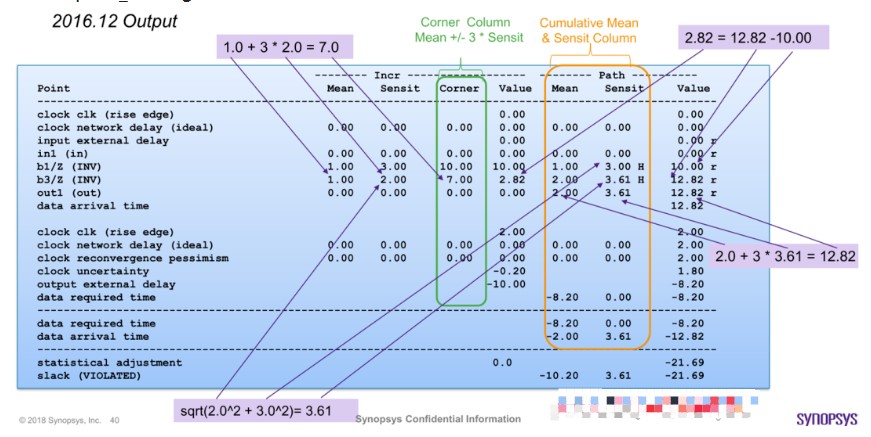

我们可以用reprot_timing -variation报POCV Timing并显示其中的Variation。和普通的Timing report一样,也分为三大列,左边是Point,右边是Incr和Path,其中Incr和Path下面会显示几列内容,这个是普通的Report所没有的,它显示的就是Variation的影响。Incr是每个Point单独增加或者说引入的Delay值;Path是Timing path上累积下来的总Delay值。

然后看下Incr下面的四列值:Mean: 平均值,也就是高斯分布中的μ值(它很关键)Sensit: 全称是sensitivity,也就是1个Sigma的值;Corner: 高斯分布3个(具体几个是可以设置的)Sigma边界的最差值,比如Setup的话就是Mean+3*Sensit,如果是Hold的话就是Mean-3*Sensit。这个值的参考意义不是特别大,不要以为它的Delay很大那么就会导致整个Path的Delay增加很多,不是这样的,后边Path的Delay不是它的累积,只有Mean值是累加下去的。Value: 需要注意它和Corner的区别,这个非常容易搞错!!!其实Value值是一个反推值,它不是直接根据上面几个值算出来的值,而是根据当前Point上Path的Delay Value减去上个Point上Path的Delay value值得到的。因此从结果上看上去,你把每个Point上Incr的Value累加起来得到的就是Path delay,但是需要注意的是它们之间的因果关系,即先有谁,后有谁,不要搞错了。这个值的参考意义比Corner更大。从上图示例其实就能看出来,b3 Cell的delay是Corner值是7ns,但是对于整个Path的贡献delay其实并没有那么大,只有2.82ns(Value值)。

接着看下Path下面的三列:先看

Value:就是从Path的开始到当前Point的累积Delay值。与普通的BCWC或者OCV的timing report不同之处在于,它不是由Incr下面的Value值累加得到的(前面其实也说了),而是根据Path下方的Mean值和Sensit值得到的。每一行的Path delay value = Path mean +/- (3 * Path sensit)对于Setup就是+,对于Hold就是-。

Mean:Path mean其实就是每个Point Incr的Mean的累加。Path mean = mean_1st_stage + mean_2nd_stage + .. + mean_previous_stage + mean_current_stage

Sensit:Path sensit是每个Point sensit的方和根(RSS, Root-Sum Square)值:Path sensit = sqrt(sensit_1st_stage^2 + sensit_2nd_stage^2 + … + sensit_previous_stage^2 + sensit_current_stage^2)。

因此有了Path的value值就可以反推得到前面所说的每一级的delay “Value”了。

Statistical adjustment(统计调整):

星球有很多人问:PT rpt 里最后的有一行statistical adjustment ,这个值是怎么来的以及有什么作用?这是由于在POCV分析中,arrival和required time都包含统计的偏差(variation),path的slack corner不会是required corner和arrival corner之间的简单的差值,而是根据mean和sigma算出的值,这两者之间会有一个差值,这个就是statistical adjustment。意义不是很大,就是让你看到它们不是required corner和arrival corner之间的简单的差值关系,和value类似,是个反推值。原因:统计量的标准差并不是简单的和,而是平方和的平方根。路径的统计调整(statistical adjustment)一方面是路径的slack corner与另一方面是required corner和arrival corner之间的差异。

审核编辑 黄昊宇

-

POCV

+关注

关注

1文章

6浏览量

12597

发布评论请先 登录

POCV Timing Report详细讲解

POCV Timing Report详细讲解

评论