毫米晶体管比 A11 仿生芯片多 70%。 另外,A12 仿生芯片是苹果首个采用 7nm 制程工艺的芯片,相比前代其速度提升最高达 15%,4 个能效核心节能最高达 50%,GPU 速度提升最高达 50%。

2018-10-05 08:48:55 3996

3996 芯片,也就是Navi系列GPU。在制程工艺上,NVIDIA这一次似乎不打算跟AMD硬拼了,图灵GPU使用的还是台积电12nm FFN工艺,今年7nm芯片能不能发还是个谜。

2019-03-01 09:48:46 1190

1190 为Ampere的Turing GPU架构的继任者将是图形行业的一项重大交易,它将在总体性能和效率上实现比预期更大的性能飞跃。该报告再次指出Ampere采用了7nm工艺节点。 NVIDIA首席

2020-01-06 01:56:00 5623

5623 8月21日,台积电在其官方博客上宣布,自2018年开始量产的7nm工艺,其所生产的芯片已经超过10亿颗。此外,台积电官网还披露了一个消息,其6nm工艺制程于8月20日开始量产。 先看7nm,台积电

2020-08-23 08:23:00 6178

6178 今年底明年初TSMC、三星的10nm工艺就会量产了,Intel的真·10nm处理器也会在明年下半年发布,而GlobalFoundries已经确定跳过10nm节点,他们下一个高性能工艺直接杀向了7nm,也不再选择三星授权,是自己研发的。

2016-11-08 11:57:17 1360

1360 日前中芯国际CEO邱慈云表态今年晚些时候会投资研发7nm工艺,不过他并没有给出国产7nm工艺问世时间,考虑到14nm工艺目标定在2018-2020年左右,估计国产的7nm工艺至少也得在2020年之后了。

2017-03-17 09:28:31 2759

2759 常听说的,诸如,台积电16nm工艺的Nvidia GPU、英特尔14nm工艺的i5,等等,这个长度的含义,具体的定义需要详细的给出晶体管的结构图才行,简单地说,在早期的时候,可以姑且认为是相当于晶体管的尺寸。

2018-01-23 08:42:49 26020

26020 芯片的7nm工艺我们经常能听到,但是7nm是否真的意味着芯片的尺寸只有7nm呢?让我们一起来看看吧!

2023-12-07 11:45:31 10554

10554

3nm工艺,外媒的报道显示,台积电是计划每平方毫米集成2.5亿个晶体管。 作为参考,采用台积电7nmEUV工艺的麒麟9905G尺寸113.31mm2,晶体管密度103亿,平均下来是0.9亿/mm2,3nm工艺晶体管密度是7nm的3.6倍。这个密度形象化比喻一下,就是将奔腾4处理器缩小到

2020-04-20 11:27:49 5155

5155 1月21日,寒武纪思元290智能芯片及加速卡、玄思1000智能加速器量产落地后首次正式亮相。思元290智能芯片是寒武纪的首颗训练芯片,采用台积电7nm先进制程工艺,集成460亿个晶体管,支持MLUv02扩展架构,全面支持AI训练、推理或混合型人工智能计算加速任务。

2021-01-22 10:34:32 3262

3262 很多晶体管组成的。芯片制程是指在芯片中,晶体管的栅极宽度。因为在整个芯片中,晶体管的栅极是整个电路中最窄的线条。如果栅极宽度为10nm,则称其为10nm制程。纳米数越小,比如从10nm到 7nm,就可以

2019-12-10 14:38:41

GPU和CPU产品依旧在使用五年前的14nm工艺或者其改进版本。新的10nm、7nm工艺虽然已经上市,但是综合频率、功耗、晶体管密度等因素来看,其表现依旧不能令人满意。进入2020年,也就是21世纪20

2020-07-07 11:38:14

7nm新工艺的加持:RX 5500 XT可轻轻松松突破2GHz

2021-06-26 07:05:34

技(Synopsys, Inc., 纳斯达克股票市场代码: SNPS)近日宣布,在设计人员的推动下,Fusion Design Platform™已实现重大7nm工艺里程碑,第一年流片数突破100,不仅

2020-10-22 09:40:08

XX nm制造工艺是什么概念?为什么说7nm是物理极限?

2021-10-20 07:15:43

(forksheet),之后过渡到 A7 及更高节点的 CFET(已在 VLSI 2025 大会上展示)。

(图片来源:Imec)

下一个主要架构——CFET——采用 n 型和 p 型晶体管的垂直堆叠,本质上

2025-06-20 10:40:07

的晶体管制程从14nm缩减到了1nm。那么,为何说7nm就是硅材料芯片的物理极限,碳纳米管复合材料又是怎么一回事呢?面对美国的技术突破,中国应该怎么做呢?XX nm制造工艺是什么概念?芯片的制造...

2021-07-28 07:55:25

调制和振荡器。晶体管可以独立封装,也可以封装在非常小的区域内,容纳1亿个或更多晶体管集成电路的一部分。(英特尔 3D 晶体管技术)严格来说,晶体管是指基于半导体材料的所有单一元件,包括由各种半导体材料

2023-02-03 09:36:05

450 万个门、包含数十亿个晶体管的时钟电路上;跟踪需要 4.5 小时,仿真总共需要 12 小时,在 250 个 CPU 上运行。总结设计 7nm 和更小工艺节点的 SoC 是一项艰巨的任务,需要专业的时钟分析知识以确保首次通过硅片成功。原作者:EETOP编译整理

2022-11-04 11:08:00

从7nm到5nm,半导体制程芯片的制造工艺常常用XXnm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工艺。所谓的XXnm指的是集成电路的MOSFET晶体管栅极

2021-07-29 07:19:33

10月7日,沉寂已久的计算技术界迎来了一个大新闻。劳伦斯伯克利国家实验室的一个团队打破了物理极限,将现有最精尖的晶体管制程从14nm缩减到了1nm。晶体管的制程大小一直是计算技术进步的硬指标。晶体管

2016-10-08 09:25:15

10nm、7nm等到底是指什么?芯片工艺从目前的7nm升级到3nm后,到底有多大提升呢?

2021-06-18 06:43:04

如今随着芯片制程的不断提升,芯片中可以有100多亿个晶体管,如此之多的晶体管,究竟是如何安上去的呢? 这是一个Top-down View 的SEM照片,可以非常清晰的看见CPU内部的层状结构

2020-07-07 11:36:10

目前的GS464V升级到LA664,因此单核性能有较大提升,达到市场上主流设计。至于未来的工艺,龙芯表示目前公司针对7nm的工艺制程对不同厂家的工艺平台做评估,不过他们没有透露什么时候跟进7nm工艺

2023-03-13 09:52:27

晶体管(transistor)

4

5纳米工艺的四核处理器已能容纳8亿个晶体管

2009-11-05 10:34:25 1669

1669 根据最新消息,IBM成功利用碳纳米材料,在单个芯片上集成了上万个9nm制程工艺的晶体管,相信大家对于著名的摩尔定律都略知一二,但是随着集成电路晶体管尺寸越来越小,CPU内存等

2012-11-08 10:28:18 4009

4009 为什么说7nm是物理极限?缩短晶体管栅极的长度可以使CPU集成更多的晶体管或者有效减少晶体管的面积和功耗,并削减CPU的硅片成本。不过这种做法也会使电子移动的距离缩短,容易导致晶体管内部电子自发通过

2016-10-10 16:49:39 6418

6418 费米架构诞生于2010年4月,以意大利著名物理学家恩利克·费米命名,是特斯拉(Tesla)架构的后继者,也是支持DX12的最老的NVIDIA GPU。它初期采用40nm工艺制造,后期部分移动版本升级到28nm工艺,最多集成30亿个晶体管。

2018-06-26 05:46:00 1660

1660 7nm节点,AMD做到了(CPU/GPU)世界首发,新一代CPU会使用Zen 2架构,此外AMD还在发布会上提到了Zen 3架构进展顺利,正在设计中,它将使用7nm+工艺,也就是7nm EUV工艺。虽然有

2018-11-27 16:35:24 4132

4132 基于7nm工艺(图中的芯片面积很小)、集成新架构GPU核心(Ampere?),同时深度学习浮点运算性能继续爆发。

2018-04-12 13:19:00 3201

3201 46届Cowen技术大会上,AMD技术总监Mark Papermaster再一次向外公布朝向7nm工艺技术的发展,他表示7nm技术将会在晶体管密度和功耗上提升巨大,他还透露称目前研发的7nm产品有三款,之后的产品都会应用7nm,下半年将会正式采样。 本文引用地址: AMD现阶段的12nm工艺

2018-07-06 10:33:00 985

985 据SemiEngineering报道,IBS的测算显示,10nm芯片的开发成本已经超过了1.7亿美元,7nm接近3亿美元,5nm超过5亿美元。如果要基于3nm开发出NVIDIA GPU那样复杂的芯片,设计成本就将高达15亿美元。

2018-06-25 15:25:00 1639

1639

VEGA GPU是全球第一个使用7nm工艺的GPU,现在已经开始样品出货,预计在今年下半年开始大规模出货。这比之前预期的时间表提前了不少,也打了Nvidia一个措手不及,让AMD以迅雷不及掩耳之势抢得了“全球第一块7nm GPU”。

2018-06-29 16:17:24 4863

4863 在说明AMD 7nm处理器和Intel 7nm处理器的分别之前,我们必须了解一点就是,由于10nm的难产,Intel在7nm工艺上远远落后于AMD,如果是在7nm制作工艺上没什么对比性,当然实际性能就不一定了,因此我们可以主要来谈谈AMD的7nm处理器有什么改变。

2018-07-23 10:04:23 20462

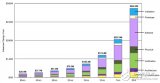

20462 与16nm FF工艺相比,台积电的7nm工艺(代号N7)将提升35%的性能,降低65%的能耗,同时晶体管密度是之前的三倍。2019年初则会推出EUV工艺的7nm+(代号N7+)工艺,晶体管密度再提升20%,功耗降低10%,不能性能没有变化。

2018-08-17 10:28:30 19290

19290 作为最前沿的手机SoC芯片,拥有全球领先的TSMC 7nm制造工艺工艺性能提升20%,能效提升40%在指甲盖大小的尺寸上塞进69亿个晶体管。

2018-09-03 14:46:17 3335

3335 作为全球首款TSMC 7nm 制程工艺的手机芯片,相比上一代产品麒麟970,它的芯片面积缩小了,晶体管密度却提升到1.6 倍,性能也相应能提升20%,能效比提升40%。麒麟980相比当年的麒麟920,晶体管密度已经提升6.8倍,性能提升2.5倍,能效则提升4.0倍。

2018-09-10 15:07:39 7036

7036 7nm Vega还是世界首个支持PCI-E 4.0技术的GPU,双向带宽64GB/s,同时借助带宽高达100GB/s的Infinity Fabric系统总线,支持四路GPU并行,而且扩展性极佳,双路性能提升99%,四路比单路提升298%,八路比单路提升664%,几乎完美。

2018-11-09 17:36:49 5434

5434 还是路线图都在按计划进行。 根据台积电提供的数据,7nm相比于目前的14/12nm可以将晶体管密度提高一倍,同等

2018-11-29 15:35:02 521

521 CES 2019展会上,AMD CEO苏姿丰博士受邀发表主题演讲,不负众望放出重磅大招:全球第一款基于7nm工艺GPU核心的游戏显卡“Radeon VII”正式亮相!

2019-01-12 11:09:12 1564

1564 AMD日前发布了全球首款采用7nm工艺核心的游戏卡Radeon VII,定位直指RTX 2080,将在2月7日解禁发售。该显卡制程工艺领先一代,晶体管密度提升100%,相同功耗下性能提升25%;同样频率下功耗降低50%。

2019-02-11 11:53:23 3541

3541 XX nm制造工艺是什么概念?芯片的制造工艺常常用90nm、65nm、40nm、28nm、22nm、14nm来表示。现在的CPU内集成了以亿为单位的晶体管,这种晶体管由源极、漏极和位于他们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流通断的作用。

2019-02-20 11:08:02 34080

34080 通过使用三星7nm EUV工艺代替台积电的7nm工艺,Nvidia可能能够获得更多供应。

2019-06-10 09:06:12 7000

7000 随着AMD发布7nm Navi架构的RX 5700系列显卡,NVIDIA今年也要面临Intel一样的竞争压力了,那就是AMD在游戏卡、数据中心市场上有抢市场的资本了。

2019-06-13 15:44:15 1129

1129 7nm工艺计划2021年推出,相比10nm工艺晶体管密度翻倍,每瓦性能提升20%,设计复杂度降低了4倍。

2019-07-19 10:49:36 3405

3405 CPU使用数十亿个微型晶体管,电子门打开和关闭以执行计算。晶体管越小,所需的功率就会越小。7nm和10nm是这些晶体管尺寸的测量尺寸。nm是纳米和微小长度的缩写,以此来判断特定CPU有多强大的有用指标。

2019-08-18 10:02:17 7884

7884 在相同的半导体工艺下,晶体管集成数量和密度是决定一款芯片性能强弱的关键指标之一,比如AMD最新发布的64个核心的第二代霄龙处理器据集成了高达320亿个晶体管。

2019-08-22 14:58:01 1703

1703 今年AMD确实大打翻身仗,7nm锐龙3000系列处理器让AMD在CPU处理器的工艺上首次超越了Intel。而当时Intel还在深耕14nm,好在最近Intel开始量产10nm工艺,而且7nm工艺也已经走上正轨。

2019-09-08 09:45:53 1222

1222 7nm+ EUV节点之后,台积电5nm工艺将更深入地应用EUV极紫外光刻技术,综合表现全面提升,官方宣称相比第一代7nm EDV工艺可以带来最多80%的晶体管密度提升,15%左右的性能提升或者30%左右的功耗降低。

2019-09-26 14:49:11 5944

5944 12nm在NVIDIA手中已经打磨有段时间了,接下来无论如何也要升级到7nm了。

2019-11-08 17:18:16 3371

3371 从16nm Pascal到12nm Turing,NVIDIA最近两代的GPU一直停留在16/12nm节点上,对最新的7nm工艺似乎没啥兴趣,反正友商从14nm到7nm工艺的显卡都打不过NVIDIA显卡,老黄确实不着急。

2019-11-09 10:06:50 2726

2726 在SC 19超算大会上,Intel正式宣布了他们为高性能计算打造的Xe架构GPU——Ponte Vecchio(维琪奥桥),同时它也会首发Intel的7nm工艺,2021年会用于Intel花了50亿美元给美国国防部建造的Aurora极光超算上。

2019-11-21 09:48:42 3851

3851 尽管AMD已经推出了7nm工艺、RDNA架构的新一代Navi家族显卡,但是NVIDIA在高端GPU市场上的地位依然无可动摇,12nm工艺的图灵Turing显卡在性能及能效上还是占据上风。

2019-12-10 10:44:13 2301

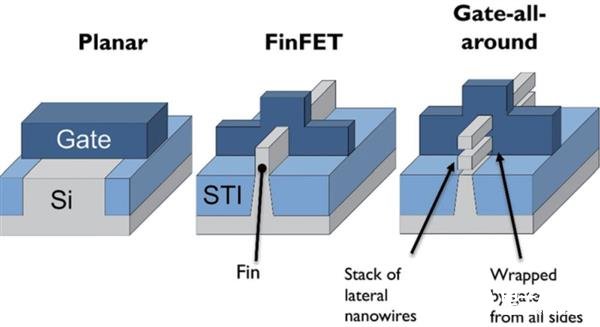

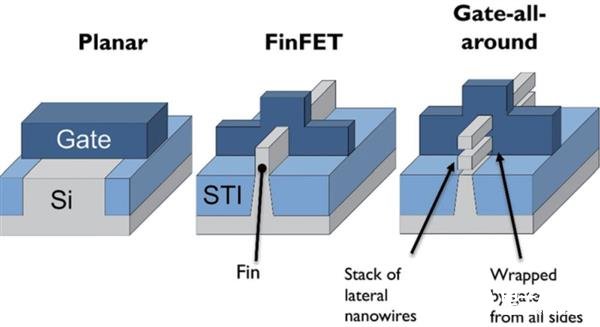

2301 目前全球最先进的半导体工艺已经进入 7nm,下一步还要进入 5nm、3nm 节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。

2019-12-10 15:40:49 7723

7723 目前全球最先进的半导体工艺已经进入7nm,下一步还要进入5nm、3nm节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。

2019-12-10 16:56:15 4082

4082 随着AMD的全新7nm制程工艺的RDNA架构推出,代表着AMD在未来的GPU市场上将有一番大作为,在过去的几代中,AMD的GPU已经利用了很久的基于GCN架构的计算单元。

2019-12-10 17:06:40 3623

3623 华为今年推出了麒麟990及麒麟990 5G处理器,后者是首款真正上市的5G SoC处理器,集成103亿个晶体管,首发7nm EUV工艺,很好很强大。不过麒麟990的CPU/GPU架构没升级,让很多花粉感觉遗憾,这个问题要等下代的麒麟1020来解决了。

2019-12-13 10:15:06 1433

1433 2020年的NVIDIA GTC大会将在3月22到26日举行,届时NVIDIA发布新一代Ampere安培架构的GPU应该没跑了,要知道GTC大会上已经有两三年没发布真正的新一代GPU了,等的黄花菜都凉了。

2020-01-04 10:13:24 3556

3556 根据消息,英伟达将在2020年3月的GTC大会期间宣布其安培显卡,目前所有证据都表明安培显卡将采用7nm工艺生产。

2020-01-13 15:01:25 2959

2959 目前最为先进的芯片制造技术为7nm+Euv工艺制程,比较出名的就是华为的麒麟990 5G芯片,内置了超过100亿个晶体管。

2020-01-16 08:48:44 2469

2469 在工艺制程方面,台积电的进度明显要快于英特尔。其实在2017年的时候,英特尔就指出台积电7nm并非真实的7nm。而且英特尔呼吁行业应该统一命名标准,防止命名混乱。英特尔更希望以晶体管密度作为衡量标准。

2020-03-01 08:13:00 3563

3563 Intel之前已经宣布在2021年推出7nm工艺,首发产品是数据中心使用的Ponte Vecchio加速卡。7nm之后的5nm工艺更加重要了,因为Intel在这个节点会放弃FinFET晶体管转向GAA晶体管。

2020-03-11 09:51:09 6773

6773

FinFET晶体管随后也成为全球主要晶圆厂的选择,一直用到现在的7nm及5nm工艺。

2020-03-12 07:48:00 2686

2686 随着GTC 2020大会事实上的取消,NVIDIA今年3月份发布下一代安培“Ampere”显卡的可能性基本没了。在这个问题上,NVIDIA倒也不着急,高级副总Jeff Fisher表示他们的GPU架构领先对手2年多。

2020-03-26 08:55:42 1028

1028 随着GTC 2020大会事实上的取消,NVIDIA今年3月份发布下一代安培“Ampere”显卡的可能性基本没了。在这个问题上,NVIDIA倒也不着急,高级副总Jeff Fisher表示他们的GPU架构领先对手2年多。

2020-03-26 14:58:13 2982

2982 近日,台积电正式披露了其最新3nm工艺的细节详情,其晶体管密度达到了破天荒的2.5亿/mm²!

2020-04-20 09:02:36 5294

5294 近日,台积电正式披露了其最新3nm工艺的细节详情,其晶体管密度达到了破天荒的2.5亿/mm²!

2020-04-20 09:09:15 4142

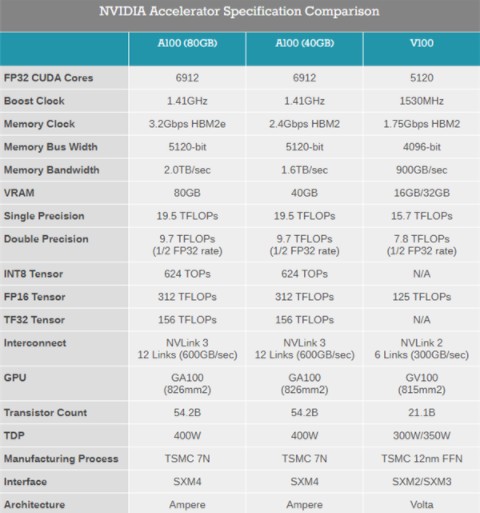

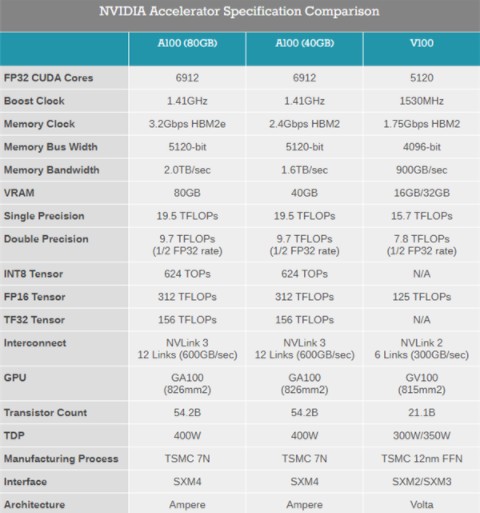

4142 据国外媒体报道,图形处理器厂商英伟达周四推出了他们首款基于安培架构的GPU英伟达A100,采用7nm工艺制造,集成超过540亿个晶体管。

2020-05-15 10:33:42 3246

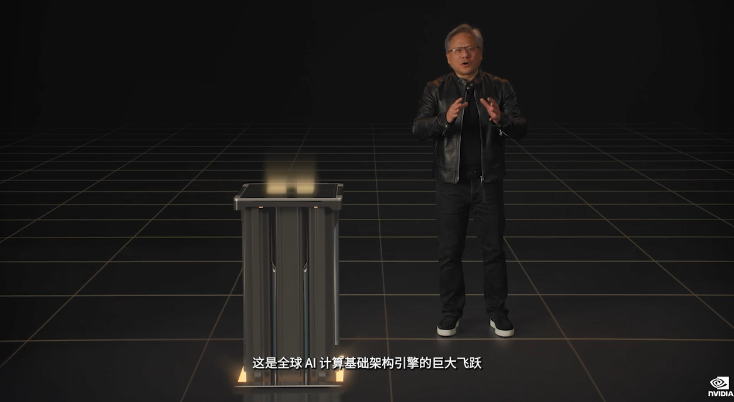

3246 突如其来的新冠肺炎大流行打乱了众多公司的产品发布计划,比如本该在今年3月英伟达(NVIDIA)GTC 2020上发布的安培(Ampere)架构曝光多次却一直未发布。今天,英伟达CEO黄仁勋发布了英伟

2020-05-15 14:48:00 9811

9811 在5月14日的GTC演讲中,NVIDIA CEO黄仁勋正式宣布了新一代GPU——Ampere安培,它使用了7nm工艺,号称性能是上代Voltra的20倍。日前NVIDIA CFO Colette Kress表示这是他们三年来的杰作,是NVDIA有史以来最强大的GPU。

2020-06-05 11:42:19 3781

3781 令人瞩目的成就。从那时起,我们已经为几十个客户的100多个产品制造了7nm芯片。它的硅足够覆盖超过13个曼哈顿街区,而且每个芯片上有超过10亿个晶体管,这是真正的Exa级,也就是超过1亿亿个7nm晶体管。

2020-08-21 15:26:25 24129

24129 在今年上半年,台积电5nm工艺所生产的芯片,尚未出货,营收排在首位的,也还是7nm工艺,在一季度和二季度,7nm分别贡献了35%和36%的营收,超过三分之一。

2020-09-02 16:52:15 3017

3017 索尼今天正式公布了PS5数字版及蓝光版的价格,新一代主机之战正式打响,后续就是要看微软、索尼两家的出货量了。 这一代的两大主机PS5、XSX依然选择了AMD的CPU、GPU架构,基本上都是7nm

2020-09-17 13:01:24 928

928 去年AMD推出了7nm Zen2架构的锐龙、霄龙处理器,这是首款7nm工艺的x86处理器。不过严格来说它是7nm+14nm混合,现在AMD要加速甩掉14nm工艺了,IO核心也有望使用台积电7nm工艺。

2020-09-24 10:12:58 2368

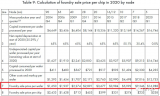

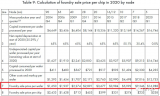

2368 与Nvidia P100 GPU(610m㎡,907亿个晶体管,强度为148.2 MTr/m㎡)相当。 从上表可以看到,5nm晶圆单片的代工销售价约是16988美元,对比7nm,涨幅超80%。而对于使用16nm或

2020-10-10 17:57:07 4645

4645

Mate 40系列来了,麒麟9000也终于来了! 这是全球第一颗、也是唯一一颗5nm工艺制造的5G SoC,集成多达153亿个晶体管,首次突破150亿大关,是目前晶体管最多、功能最完整的5G SoC

2020-10-23 09:11:10 5006

5006 Mate 40系列来了,麒麟9000也终于来了!这是全球第一颗、也是唯一一颗5nm工艺制造的5G SoC,集成多达153亿个晶体管,首次突破150亿大关,是目前晶体管最多、功能最完整的5G SoC。

2020-10-23 10:37:18 5336

5336 这几天发布Q3季度财报之后,Intel的股价跳水了10%,损失了1700多亿的市值,一方面是Q3利润下滑,一方面还是跟Intel工艺有关,10nm产能还在提升,但是7nm延期了半年到一年。

2020-10-25 10:13:53 1906

1906 使用5nm制程技术,CPU,GPU和NPU的性能遥遥领先。该芯片还集成了华为最强大的通信芯片以及最先进的ISP。由于采用了5nm工艺,麒麟9000集成了153亿个晶体管,比A14仿生晶体管多30%。麒麟9000是业界功能最强大的芯片。

2020-10-28 16:27:02 5165

5165 平方毫米,密度为1.34亿个晶体管/平方毫米。 作为对比,上代A13使用的是台积电7nm工艺,集成85亿个晶体管,内核面积94.48平方毫米,密度为8997万个晶体管/平方毫米。更早的A12也是台积电7nm工艺,集成69亿个晶体管,内核面积83.27平方毫米,密度为8286万个晶体管/平方毫米。 根据

2020-11-06 09:58:11 2359

2359 。 NVIDIA今年3月份发布了安培架构的A100加速卡(名字中没有Tesla了),升级了7nm工艺和Ampere安培架构,集成542亿晶体管,826mm2核心面积,使用了40GB HBM2显存,带宽1.6TB

2020-11-17 10:15:41 3130

3130 今晚AMD刚刚发布了7nm CDNA架构的MI100加速卡,NVIDIA这边就推出了A100 80GB加速卡。虽然AMD把性能夺回去了,但是A100 80GB的HBM2e显存也是史无前例了。

2020-11-17 10:23:53 2961

2961

3月份发布了安培架构的A100加速卡(名字中没有Tesla了),升级了7nm工艺和Ampere安培架构,集成542亿晶体管,826mm2核心面积,使用了40GB HBM2显存,带宽1.6TB/s

2020-11-17 15:38:58 2931

2931 台积电、三星在2022年就有可能将制程工艺推到2nm,AMD、苹果、高通、NVIDIA等公司也会跟着受益,现在自己生产芯片的就剩下Intel了,然而它们的7nm工艺已经延期到至少2021年了。

2020-11-18 10:02:44 2079

2079 。 原文如下: 说点题外话,大家就当看个热闹吧,既然说旧工艺的“叠加”,那咱就聊聊叠加嘛。 首先还是强调一点,现在所谓的几 nm 工艺,这个几 nm 的数字并不是指晶体管的 gate length(或沟道长度)——很多人对此是存在误解的。比如台积电的 7nm 工艺,晶体管并不存在

2021-07-02 16:39:34 6837

6837 NVIDIA发布新一代产品—NVIDIA H100,H100是一款超大的芯片,采用TSMC 4N工艺,具有800亿个晶体管,也是首款采用HBM3标准的GPU。

2022-03-23 17:21:42 3450

3450

今年五月份,IBM成功推出了2nm的测试芯片,可容纳500亿颗晶体管,IBM成功将500亿个晶圆体容纳在了指甲大小的芯片上,这标志着 IBM 在半导体设计和工艺方面实现了重大突破,对产业链企业都将有不小的帮助。

2022-06-22 09:52:38 2679

2679 全球首颗2nm芯片已经被IBM研制出来了,在这一颗指甲盖大小面积的芯片上可以容纳500亿颗晶体管,芯片制程工艺的进步必将让半导体行业的发展越来越快。接下来我们详细了解下这款2nm芯片的特性、功耗等,跟7nm芯片做个对比,看下2nm芯片与7nm芯片之间有何差距。

2022-06-22 09:52:43 7529

7529 7nm和12nm指的是晶体管间的距离。在同等cpu面积下,距离越小,能够摆放的晶体管数量也就越多。那么,对于运算速度而言,晶体管越多,运算速度提高的可能性也就越大。

2022-06-23 15:58:37 9960

9960 到2007年,当时Intel公司在旧金山举办了一场演讲,在那场演讲中,Intel CEO展示了一款32nm制程的芯片,他表示该芯片中集成了超过19亿个晶体管,Intel将会在2009年正式量产32nm制程工艺的芯片。 2010年Intel推出了Corei7≤980X,这款芯片采用了32nm制程工艺

2022-07-04 09:47:46 4648

4648 在芯片设计和制造中,纳米表示的是芯片中晶体管与晶体管之间的距离,在体积相同大小的情况下,7nm工艺的芯片容纳的晶体管的数量,几乎是14nm工艺芯片的2倍。

2022-07-06 16:53:46 28009

28009 Instinct MI300A是全球首款面向HPC、AI的APU加速器,集成多达13颗小芯片,包括nm工艺的24个Zen4 CPU核心、CDNA3 GPU核心、128GB HBM3内存,还有6nm工艺的中介层,整体晶体管数量多达1460亿个。

2023-07-07 11:31:04 1390

1390

的NMN910 5G SoC 芯片,也被称为麒麟9000。 这款芯片集成了49亿个晶体管,尺寸为 5 纳米,成为了全球首个量产的5nm 5G SoC芯片。这是一个重要的里程碑,它意味着华为已经成为了第一个推出5nm工艺技术的芯片制造商,并且在性能方面达到了全球领先的水平。 首先我们

2023-09-01 16:47:35 9729

9729 半导体芯情了解到,A100是英伟达最新推出的一款高性能计算芯片,采用了全新的Ampere架构,Ampere架构是NVIDIA于 GTC 2020发布的GPU架构,NVIDIA Ampere 由540亿晶体管组成,是7nm芯片。

2023-11-14 16:30:16 2149

2149

上次我的文章解释了所谓的7nm不是真的7nm,是在实际线宽无法大幅缩小的前提下,通过改变晶体管结构的方式缩小晶体管实际尺寸来达到等效线宽的效果那么新的问题来了:从平面晶体管结构(Planar)到立体

2023-12-19 16:29:01 1396

1396

最近网上因为光刻机的事情,网上又是一阵热闹。好多人又开始讨论起28nm/7nm的事情了有意无意之间,我也看了不少网上关于国产自主7nm工艺的文章。不过这些文章里更多是抒情和遐想,却很少有人针对技术

2024-10-08 17:12:49 1339

1339

电子发烧友App

电子发烧友App

评论