今年五月份,IBM成功推出了2nm的测试芯片,可容纳500亿颗晶体管,IBM成功将500亿个晶圆体容纳在了指甲大小的芯片上,这标志着 IBM 在半导体设计和工艺方面实现了重大突破,对产业链企业都将有不小的帮助。

据了解,2nm芯片研制工艺在未来的制造工程中极有可能会发挥关键性的作用,这项技术预计可使芯片的性能提升 45%,能耗降低 75%,极大的满足了半导体行业不断增长的需求。

IBM已经率先完成了2纳米技术的突破,2nm的实现可能性很大。2nm芯片还可以通过为处理器注入内核级创新来提升人工智能、云计算等前沿工作负载的功能,2nm技术上突破应该也还有很长的一段路要走。

值得关注的是,基于 2nm 的芯片即将在2025 年实现量产。

本文综合整理自半导体行业观察 数码密探 网易

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54422浏览量

469266 -

IBM

+关注

关注

3文章

1879浏览量

77127 -

晶体管

+关注

关注

78文章

10439浏览量

148592 -

2nm

+关注

关注

1文章

219浏览量

5174

发布评论请先 登录

相关推荐

热点推荐

马斯克:要建一座2nm芯片厂,能在里面“抽雪茄、吃汉堡”

电子发烧友网报道(文/李弯弯)在AI时代,数据量呈爆炸式增长,对计算能力的需求也与日俱增。2nm工艺的芯片能够在更小的面积上集成更多的晶体管,从而大幅提升芯片的性能和能效。然而,

台积电2nm芯片成本暴涨80%!苹果A20、高通骁龙旗舰芯片集体涨价

据外媒消息,iPhone折叠屏手机 和 iPhone 18 Pro 机型将搭载 A20 Pro 芯片,展示台积电最新的 2nm 工艺 N2,其性能提升幅度比 A19 芯片高出 15%,

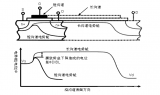

漏致势垒降低效应如何影响晶体管性能

随着智能手机、电脑等电子设备不断追求轻薄化,芯片中的晶体管尺寸已缩小至纳米级(如3nm、2nm)。但尺寸缩小的同时,一个名为“漏致势垒降低效应(DIBL)”的物理现象逐渐成为制约

三星发布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

电子发烧友网综合报道 近日,三星电子正式发布其手机芯片Exynos 2600。这款芯片意义非凡,它不仅是三星首款2nm芯片,更是全球首款采用2

三星公布首批2纳米芯片性能数据

三星公布了即将推出的首代2nm芯片性能数据;据悉,2nm工艺采用的是全栅极环绕(GAA)晶体管技术,相比第二代3nm工艺,性能提升5%,功耗

台积电2纳米制程试产成功,AI、5G、汽车芯片,谁将率先受益?

与现行的3nm工艺相比,台积电在2nm制程上首次采用了GAA(Gate-All-Around,环绕栅极)晶体管架构。这种全新的结构能够让晶体管电流控制更加精确,减少漏电问题,大幅提升

多值电场型电压选择晶体管结构

多值电场型电压选择晶体管结构

为满足多进制逻辑运算的需要,设计了一款多值电场型电压选择晶体管。控制二进制电路通断需要二进制逻辑门电路,实际上是对电压的一种选择,而传统二进制逻辑门电路通常比较复杂

发表于 09-15 15:31

全球首款2nm芯片被曝准备量产 三星Exynos 2600

据外媒韩国媒体 ETNews 在9 月 2 日发文报道称全球首款2nm芯片被曝准备量产;三星公司已确认 Exynos 2600 将成为全球首款采用 2nm 工艺的移动 SoC

晶体管架构的演变过程

芯片制程从微米级进入2纳米时代,晶体管架构经历了从 Planar FET 到 MBCFET的四次关键演变。这不仅仅是形状的变化,更是一次次对物理极限的挑战。从平面晶体管到MBCFET,

今日看点丨蔚来自研全球首颗车规5nm芯片!;沃尔沃中国区启动裁员计划

低延时,快速响应。”此外,李斌还表示,这款芯片对全行业开放,谁想用都可以找我们,还可以降本。 据悉,神玑NX9031芯片和底层软件均实现自主设计,拥有超过500亿

发表于 07-08 10:50

•2249次阅读

下一代高速芯片晶体管解制造问题解决了!

晶体管的密度,同时减少了芯片的横向面积。

相比传统的FinFET和纳米片晶体管,叉片晶体管能够显著减少nFET和pFET之间的间距,从而在相同的芯片

发表于 06-20 10:40

台积电2nm良率超 90%!苹果等巨头抢单

当行业还在热议3nm工艺量产进展时,台积电已经悄悄把2nm技术推到了关键门槛!据《经济日报》报道,台积电2nm芯片良品率已突破 90%,实现重大技术飞跃!

无结场效应晶体管详解

当代所有的集成电路芯片都是由PN结或肖特基势垒结所构成:双极结型晶体管(BJT)包含两个背靠背的PN 结,MOSFET也是如此。结型场效应晶体管(JFET) 垂直于沟道方向有一个 PN结,隧道穿透

2nm芯片问世,可容纳500亿颗晶体管

2nm芯片问世,可容纳500亿颗晶体管

评论