8月21日,台积电在其官方博客上宣布,自2018年开始量产的7nm工艺,其所生产的芯片已经超过10亿颗。此外,台积电官网还披露了一个消息,其6nm工艺制程于8月20日开始量产。 先看7nm,台积电

2020-08-23 08:23:00 6178

6178 从芯片的制造来看,7nm就是硅材料芯片的物理极限,而台积电更先进的7nm工艺也将开始进入试产阶段。

2016-10-21 10:23:23 1177

1177 从芯片的制造来看,7nm就是硅材料芯片的物理极限,到了7nm节点即使是finfet也不足以在保证性能的同时抑制漏电,所以工业界用砷化铟镓取代了单晶硅沟道来提高器件性能。

2016-10-21 14:46:30 6518

6518 日前中芯国际CEO邱慈云表态今年晚些时候会投资研发7nm工艺,不过他并没有给出国产7nm工艺问世时间,考虑到14nm工艺目标定在2018-2020年左右,估计国产的7nm工艺至少也得在2020年之后了。

2017-03-17 09:28:31 2759

2759 芯片的7nm工艺我们经常能听到,但是7nm是否真的意味着芯片的尺寸只有7nm呢?让我们一起来看看吧!

2023-12-07 11:45:31 10554

10554

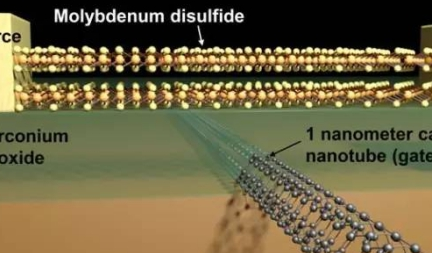

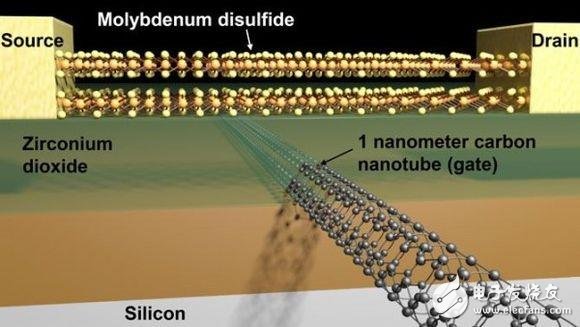

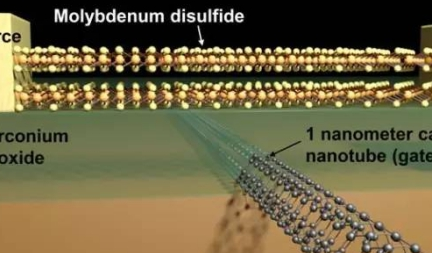

隶属美国能源部的劳伦斯伯克利国家实验室Ali Javey 团队即宣称,突破了物理极限,成功创造1 纳米晶体管。

2016-10-09 09:52:06 2065

2065

3nm工艺,外媒的报道显示,台积电是计划每平方毫米集成2.5亿个晶体管。 作为参考,采用台积电7nmEUV工艺的麒麟9905G尺寸113.31mm2,晶体管密度103亿,平均下来是0.9亿/mm2,3nm工艺晶体管密度是7nm的3.6倍。这个密度形象化比喻一下,就是将奔腾4处理器缩小到

2020-04-20 11:27:49 5155

5155 自然期刊,这对于1nm以下的半导体制程来说是一次巨大的突破。 当前主流半导体制程已经发展至3nm和5nm,乃至IBM也在近期推出了2nm,但单位面积内所能容纳的晶体管数目也已经逼近硅的物理极限,虽说制程突破受制于生产设备,却也

2021-05-18 09:00:00 6467

6467 很多晶体管组成的。芯片制程是指在芯片中,晶体管的栅极宽度。因为在整个芯片中,晶体管的栅极是整个电路中最窄的线条。如果栅极宽度为10nm,则称其为10nm制程。纳米数越小,比如从10nm到 7nm,就可以

2019-12-10 14:38:41

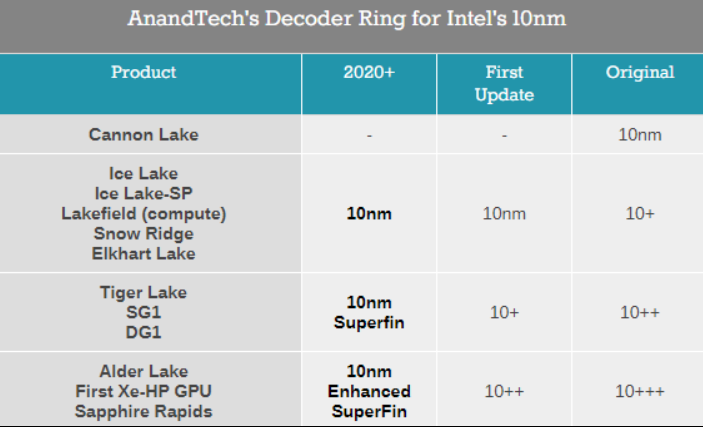

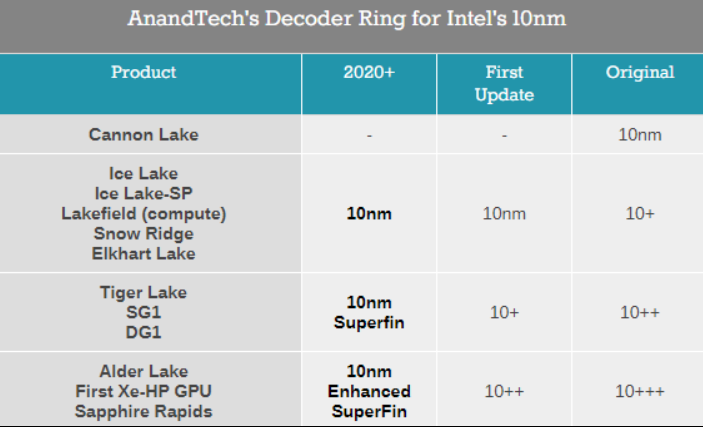

GPU和CPU产品依旧在使用五年前的14nm工艺或者其改进版本。新的10nm、7nm工艺虽然已经上市,但是综合频率、功耗、晶体管密度等因素来看,其表现依旧不能令人满意。进入2020年,也就是21世纪20

2020-07-07 11:38:14

7nm新工艺的加持:RX 5500 XT可轻轻松松突破2GHz

2021-06-26 07:05:34

国内的通富微电成为AMD 7nm芯片的封测厂商之一

2020-12-30 07:48:47

技(Synopsys, Inc., 纳斯达克股票市场代码: SNPS)近日宣布,在设计人员的推动下,Fusion Design Platform™已实现重大7nm工艺里程碑,第一年流片数突破100,不仅

2020-10-22 09:40:08

XX nm制造工艺是什么概念?为什么说7nm是物理极限?

2021-10-20 07:15:43

的晶体管制程从14nm缩减到了1nm。那么,为何说7nm就是硅材料芯片的物理极限,碳纳米管复合材料又是怎么一回事呢?面对美国的技术突破,中国应该怎么做呢?XX nm制造工艺是什么概念?芯片的制造...

2021-07-28 07:55:25

7nm 设计挑战高级节点存在许多设计挑战,例如:老化效应随着晶体管器件的开启和关闭,有两个主要的物理效应会影响可靠性:负偏压温度不稳定性 ( NBTI )热载体注入 (HCI)电路设计人员了解到

2022-11-04 11:08:00

从7nm到5nm,半导体制程芯片的制造工艺常常用XXnm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工艺。所谓的XXnm指的是集成电路的MOSFET晶体管栅极

2021-07-29 07:19:33

nm晶圆厂进入生产状态。台积电的5nm制程分为N5及N5P两个版本。N5相较于当前的7nm制程N7版本在性能方面提升了15%、功耗降低了30%,晶体管密度提升了80%。N5P版本性能较N5提升7

2020-03-09 10:13:54

、65nm、45nm、32nm、22nm、14nm、10nm、到现在的7nm(对应都是MOS管栅长),目前也有了很多实验室在进行一些更小尺寸的研究。随着MOS管的尺寸不断的变小,沟道的不断变小,出现各种

2020-12-10 06:55:40

10月7日,沉寂已久的计算技术界迎来了一个大新闻。劳伦斯伯克利国家实验室的一个团队打破了物理极限,将现有最精尖的晶体管制程从14nm缩减到了1nm。晶体管的制程大小一直是计算技术进步的硬指标。晶体管

2016-10-08 09:25:15

求一份tsmc 7nm standard cell library求一份28nm或者40nm 的数字库

2021-06-25 06:39:25

10nm、7nm等到底是指什么?芯片工艺从目前的7nm升级到3nm后,到底有多大提升呢?

2021-06-18 06:43:04

本帖最后由 eehome 于 2013-1-5 10:10 编辑

高清图详解英特尔最新22nm 3D晶体管

2012-08-05 21:48:28

目前的GS464V升级到LA664,因此单核性能有较大提升,达到市场上主流设计。至于未来的工艺,龙芯表示目前公司针对7nm的工艺制程对不同厂家的工艺平台做评估,不过他们没有透露什么时候跟进7nm工艺

2023-03-13 09:52:27

根据最新消息,IBM成功利用碳纳米材料,在单个芯片上集成了上万个9nm制程工艺的晶体管,相信大家对于著名的摩尔定律都略知一二,但是随着集成电路晶体管尺寸越来越小,CPU内存等

2012-11-08 10:28:18 4009

4009 摩尔定律是指IC上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。然而事情的发展总归会有一个权限,5nm则是硅芯片工艺的极限所在,事实上,随着10nm、7nm芯片研发消息不断报出

2016-12-22 10:23:11 43944

43944 随着智能手机的发展,半导体工艺也急速提升,从28nm、16nm、10nm到7nm这些半导体代工厂们每天争相发布最新的工艺制程,让很多吃瓜群众一脸懵逼不知道有啥用。

2018-06-10 01:38:00 49700

49700 工艺制程的进步是摩尔定律的关键一环,目前商用的最先进是10nm,下一个关键节点是7nm,后者将宣告半导体正式迈进入10nm阶段。

2017-07-25 15:13:24 1223

1223 骁龙855芯片突破制程工艺,采用7nm制程,比较前身更加节能。如果高通在2019年推出骁龙855,那么它有可能就是A13芯片,2019年的iPhone手机也会采用这个芯片。

2017-10-12 18:25:00 4086

4086 Rambus首次公布HBM3/DDR5内存技术参数,最大的关注点在于都是由7nm工艺制造。7nm工艺被认为是极限,因为到了7nm节点即使是finfet也不足以在保证性能的同时抑制漏电。所以工业界用砷化铟镓取代了单晶硅沟道来提高器件性能,7nm是一项非常复杂的技术。

2017-12-07 15:00:00 2315

2315 2018年6月6日,Computex 2018期间,AMD正式展示了代表未来的产品——7nm制程采用Zen 2架构的EPYC(霄龙)服务器处理器,以及7nm制程、32GB HBM2显存的Radeon Vega GPU,进一步加快7nm制程芯片落地的步伐。

2018-06-14 16:52:00 1121

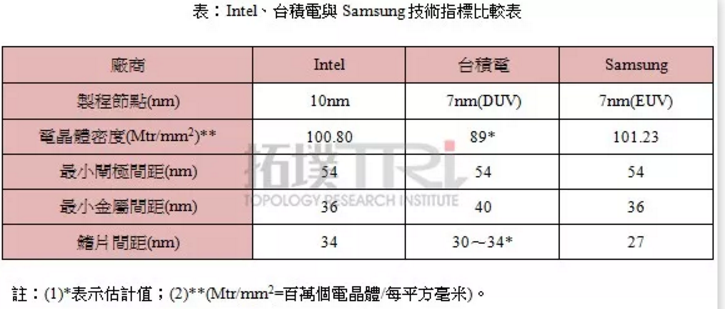

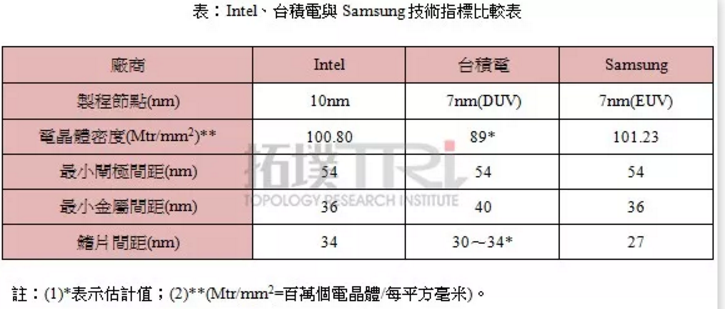

1121 由于晶体管制造的复杂性,每代晶体管制程针对不同用途的制造技术版本,不同厂商的代次间统计算法也完全不同,单纯用代次来比较并不准确。根据目前业界常用晶体管密度来衡量制程水平,英特尔最新10nm制程的晶体管密度堪比三星 EUV版本7nm制程。

2018-07-10 16:31:00 4668

4668

台积电已经在着手将其7nm制程工艺扩大到大规模生产,台积电的7nm制程工艺被称作N7,将会在今年下半年开始产能爬坡。

2018-06-12 15:14:41 4084

4084 46届Cowen技术大会上,AMD技术总监Mark Papermaster再一次向外公布朝向7nm工艺技术的发展,他表示7nm技术将会在晶体管密度和功耗上提升巨大,他还透露称目前研发的7nm产品有三款,之后的产品都会应用7nm,下半年将会正式采样。 本文引用地址: AMD现阶段的12nm工艺

2018-07-06 10:33:00 986

986 在日前举行的Computex 2018发布会上,AMD有些出人意料地进行了高规格的产品发布,公开的产品包括下一代使用7nm工艺的VEGA GPU,以及使用7nm的Zen 2处理器。目前,7nm

2018-06-29 16:17:24 4863

4863 在说明AMD 7nm处理器和Intel 7nm处理器的分别之前,我们必须了解一点就是,由于10nm的难产,Intel在7nm工艺上远远落后于AMD,如果是在7nm制作工艺上没什么对比性,当然实际性能就不一定了,因此我们可以主要来谈谈AMD的7nm处理器有什么改变。

2018-07-23 10:04:23 20462

20462 2018年下半年,芯片行业即将迎来全新7nm制程工艺,而打头阵的无疑是移动芯片,目前已知的包括苹果Apple A12/华为麒麟980以及高通骁龙855都是基于7nm工艺,制程工艺似乎成为手机芯片升级换代的一大核心点,那么7nm制程工艺好在哪,对用户来说有何价值呢?

2018-08-13 15:26:41 8284

8284 与16nm FF工艺相比,台积电的7nm工艺(代号N7)将提升35%的性能,降低65%的能耗,同时晶体管密度是之前的三倍。2019年初则会推出EUV工艺的7nm+(代号N7+)工艺,晶体管密度再提升20%,功耗降低10%,不能性能没有变化。

2018-08-17 10:28:30 19290

19290 高通宣布,即将推出新一代旗舰移动平台——骁龙855,该平台将采用7nm制程工艺。

2018-08-24 15:22:54 4677

4677 作为最前沿的手机SoC芯片,拥有全球领先的TSMC 7nm制造工艺工艺性能提升20%,能效提升40%在指甲盖大小的尺寸上塞进69亿个晶体管。

2018-09-03 14:46:17 3335

3335 作为全球首款TSMC 7nm 制程工艺的手机芯片,相比上一代产品麒麟970,它的芯片面积缩小了,晶体管密度却提升到1.6 倍,性能也相应能提升20%,能效比提升40%。麒麟980相比当年的麒麟920,晶体管密度已经提升6.8倍,性能提升2.5倍,能效则提升4.0倍。

2018-09-10 15:07:39 7036

7036 晶圆代工巨头企业台积电、三星和GF(格芯),在半导体工艺的发展上越来越迅猛,10nm制程才刚刚应用一年半,7nm制程便已经好似近在眼前。

2018-09-28 14:49:55 4996

4996 和1Xnm半导体工艺的百花齐放相比,个位数的制程就显得单调许多了,很多在10Xnm大放异彩的半导体公司都在7nm制程处遭遇到了苦头。

2018-10-26 15:40:31 17488

17488 和1Xnm半导体工艺的百花齐放相比,个位数的制程就显得单调许多了,很多在 1Xnm大放异彩的半导体公司都在7nm制程处遭遇到了苦头,随着AMD御用代工厂商GF宣布无限期延期7nm制程工艺,目前仅剩

2018-10-28 11:34:13 8116

8116 还是路线图都在按计划进行。 根据台积电提供的数据,7nm相比于目前的14/12nm可以将晶体管密度提高一倍,同等

2018-11-29 15:35:02 521

521 AMD日前发布了全球首款采用7nm工艺核心的游戏卡Radeon VII,定位直指RTX 2080,将在2月7日解禁发售。该显卡制程工艺领先一代,晶体管密度提升100%,相同功耗下性能提升25%;同样频率下功耗降低50%。

2019-02-11 11:53:23 3541

3541 XX nm制造工艺是什么概念?芯片的制造工艺常常用90nm、65nm、40nm、28nm、22nm、14nm来表示。现在的CPU内集成了以亿为单位的晶体管,这种晶体管由源极、漏极和位于他们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流通断的作用。

2019-02-20 11:08:02 34080

34080 台积电计划在明年第一季度开始量产5nm芯片,5nm较7nm晶体数量将增加1.8倍,性能提升15%。不过在今年,2019款iPhone还是继续采用7nm工艺制程的芯片,性能较上代的A12有所提升。而高通下一代旗舰芯片骁龙865将由三星代工,也是7nm EUV工艺制造。

2019-06-17 10:36:28 1404

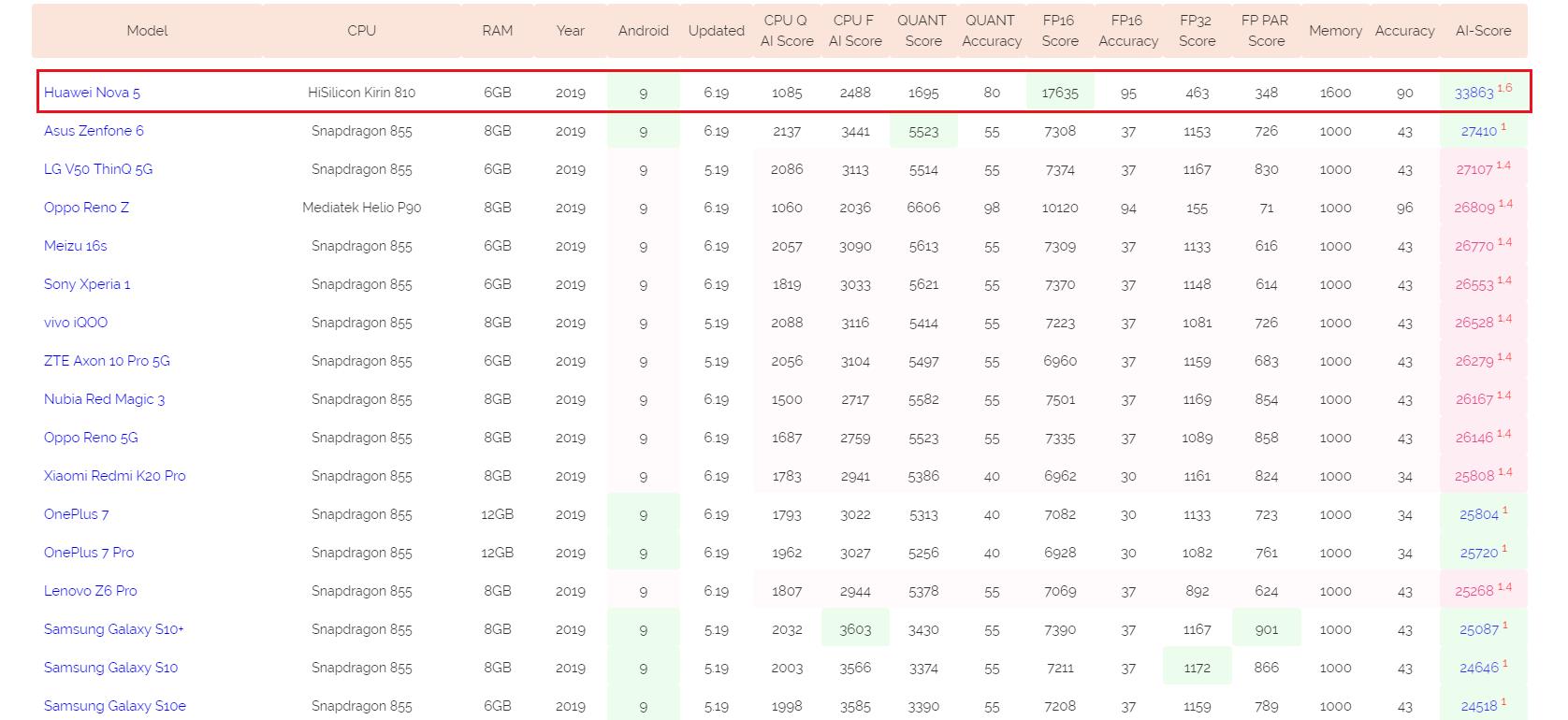

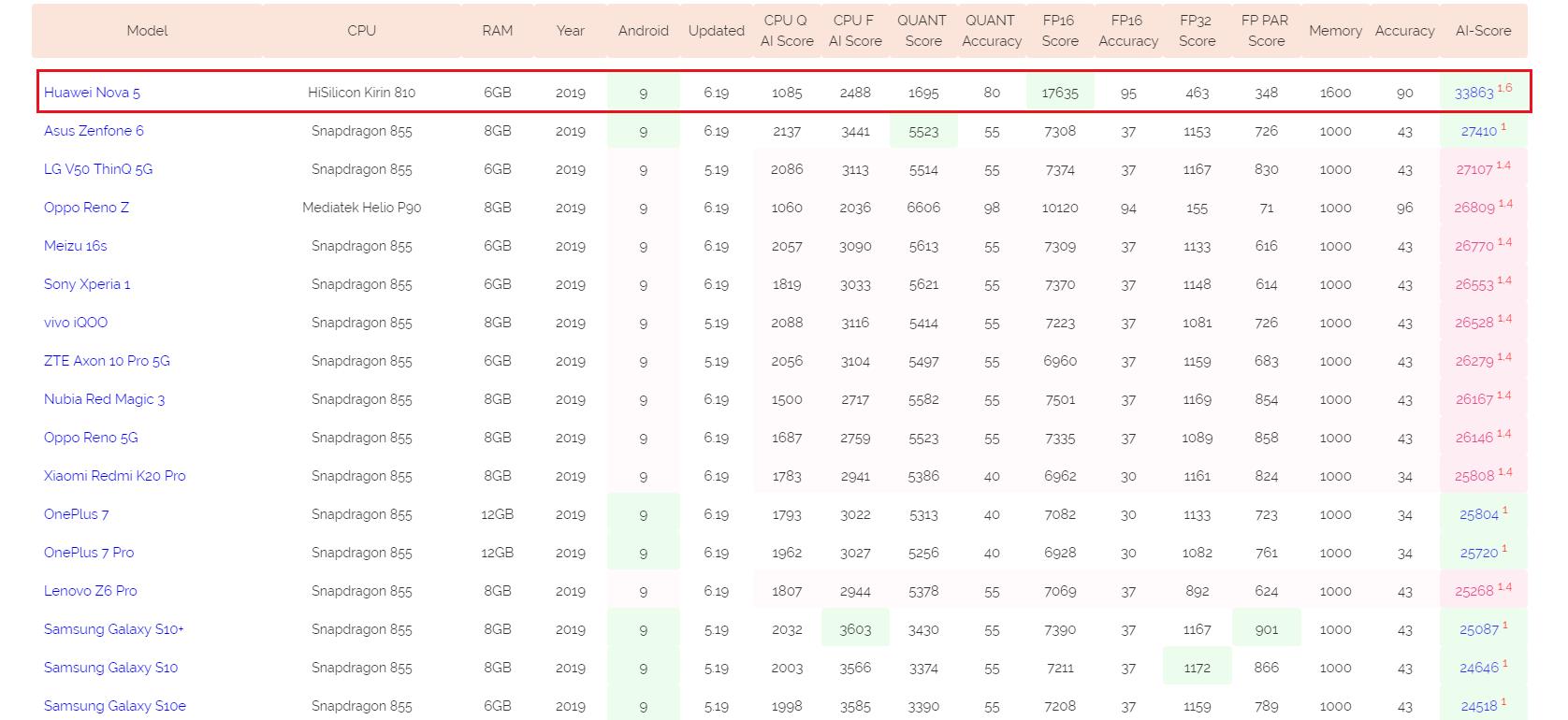

1404 nova 5搭载了华为最新推出的麒麟810。810和980一样采用了7nm制程工艺。目前,全球采用7nm制程工艺的SOC芯片只有四款:苹果A12,高通骁龙855,华为麒麟980和麒麟810,四占其二,华为是目前唯一拥有两款7nm制程SOC的公司。

2019-06-21 22:02:30 10631

10631

目前,台积电7nm制程工艺主要被AMD第三代锐龙平台使用,并且帮助锐龙处理器在主频上追上了英特尔。

2019-06-26 09:39:42 6461

6461

7nm工艺计划2021年推出,相比10nm工艺晶体管密度翻倍,每瓦性能提升20%,设计复杂度降低了4倍。

2019-07-19 10:49:36 3405

3405 CPU使用数十亿个微型晶体管,电子门打开和关闭以执行计算。晶体管越小,所需的功率就会越小。7nm和10nm是这些晶体管尺寸的测量尺寸。nm是纳米和微小长度的缩写,以此来判断特定CPU有多强大的有用指标。

2019-08-18 10:02:17 7884

7884 今年AMD确实大打翻身仗,7nm锐龙3000系列处理器让AMD在CPU处理器的工艺上首次超越了Intel。而当时Intel还在深耕14nm,好在最近Intel开始量产10nm工艺,而且7nm工艺也已经走上正轨。

2019-09-08 09:45:53 1222

1222 7nm+ EUV节点之后,台积电5nm工艺将更深入地应用EUV极紫外光刻技术,综合表现全面提升,官方宣称相比第一代7nm EDV工艺可以带来最多80%的晶体管密度提升,15%左右的性能提升或者30%左右的功耗降低。

2019-09-26 14:49:11 5945

5945 7nm是Intel下一代工艺的重要节点,而且是高性能工艺,其地位堪比现在的14nm工艺,而且它还是Intel首次使用EUV光刻的制程工艺,意义重大。

2019-10-12 14:44:54 3267

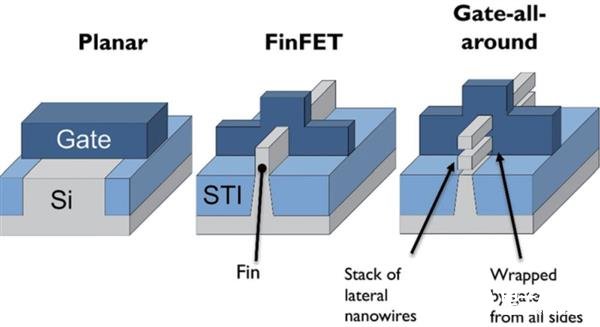

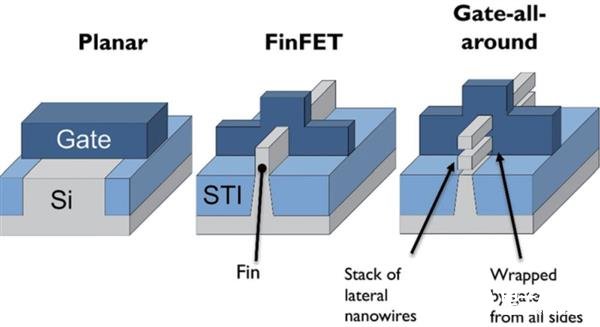

3267 目前全球最先进的半导体工艺已经进入 7nm,下一步还要进入 5nm、3nm 节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。

2019-12-10 15:40:49 7723

7723 目前全球最先进的半导体工艺已经进入7nm,下一步还要进入5nm、3nm节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。

2019-12-10 16:56:15 4082

4082 目前最为先进的芯片制造技术为7nm+Euv工艺制程,比较出名的就是华为的麒麟990 5G芯片,内置了超过100亿个晶体管。

2020-01-16 08:48:44 2469

2469 在工艺制程方面,台积电的进度明显要快于英特尔。其实在2017年的时候,英特尔就指出台积电7nm并非真实的7nm。而且英特尔呼吁行业应该统一命名标准,防止命名混乱。英特尔更希望以晶体管密度作为衡量标准。

2020-03-01 08:13:00 3563

3563 Intel之前已经宣布在2021年推出7nm工艺,首发产品是数据中心使用的Ponte Vecchio加速卡。7nm之后的5nm工艺更加重要了,因为Intel在这个节点会放弃FinFET晶体管转向GAA晶体管。

2020-03-11 09:51:09 6774

6774

FinFET晶体管随后也成为全球主要晶圆厂的选择,一直用到现在的7nm及5nm工艺。

2020-03-12 07:48:00 2686

2686 台积电5nm制造工艺基于ULV,也就是紫外线光刻技术实现,之前的7nm EUV工艺同样也是基于这项技术。那么制程的缩小又意味着什么?相比于7nm工艺,5nm工艺可以进一步提升芯片的晶体管密度,提升性能并降低功耗,可广泛用于PC、智能手机等设备的元器件中。

2020-03-12 14:10:44 3184

3184 我们经常看到报道上说芯片制程达到了14nm、7nm、5nm,最近中芯国际在没有ASML的EUV光刻机的情况下,实现了7nm的制程,有很多人对此感到很兴奋。

2020-04-19 11:40:05 27018

27018 据国外媒体报道,图形处理器厂商英伟达周四推出了他们首款基于安培架构的GPU英伟达A100,采用7nm工艺制造,集成超过540亿个晶体管。

2020-05-15 10:33:42 3246

3246 在近日的GTC上,Nvidia发布了最新的安培架构,以及基于安培架构的A100 GPU。A100 GPU使用台积电7nm工艺实现,包含了542亿个晶体管,据官方消息可以实现比起上一代V100高7倍的性能。

2020-05-20 10:17:50 3122

3122 去年AMD推出了7nm Zen2架构的锐龙、霄龙处理器,这是首款7nm工艺的x86处理器。不过严格来说它是7nm+14nm混合,现在AMD要加速甩掉14nm工艺了,IO核心也有望使用台积电7nm工艺。

2020-09-24 10:12:58 2368

2368 关于芯片工艺,Intel前几天还回应称友商的7nm工艺是数字游戏,Intel被大家误会了。不过今年Intel推出了新一代的10nm工艺,命名为10nm SuperFin工艺,简称10nm SF,号称是有史以来节点内工艺性能提升最大的一次,没换代就提升15%性能,比其他家的7nm还要强。

2020-09-27 10:35:06 4358

4358

台积电、三星在2022年就有可能将制程工艺推到2nm,AMD、苹果、高通、NVIDIA等公司也会跟着受益,现在自己生产芯片的就剩下Intel了,然而它们的7nm工艺已经延期到至少2021年了。

2020-11-18 10:02:44 2079

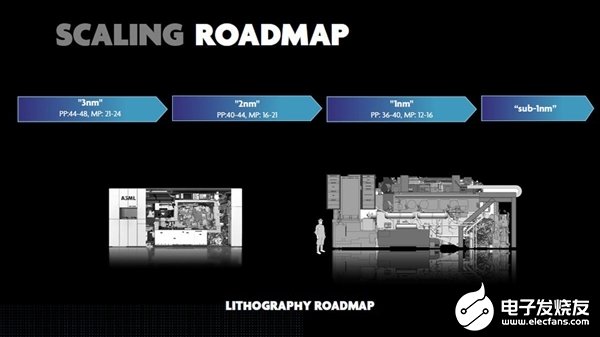

2079 如今5nm才刚刚起步,台积电的技术储备就已经紧张到了2nm,并朝着1nm迈进。根据最新报道,台积电已经在2nm工艺上取得一项重大的内部突破,虽未披露细节,但是据此乐观预计,2nm工艺有望在2023

2020-11-26 10:48:09 3409

3409

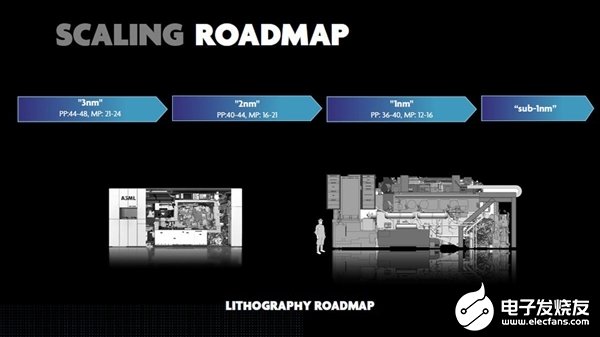

、1.5nm、1nm甚至Sub 1nm都做了清晰的路线规划,且1nm时代的光刻机体积将增大不少。 据称在当前台积电、三星的7nm、5nm制造中已经引入了NA=0.33的EUV曝光设备,2nm之后需要

2020-11-30 15:47:40 3167

3167 1 月 15 日消息,据国外媒体报道,在苹果转向 5nm,华为无法继续采用台积电的先进工艺代工芯片之后,台积电 7nm 的产能,也就有了给予其他厂商更多的可能,去年下半年 AMD 获得的产能

2021-01-15 11:27:28 3373

3373 则是早早的用上了台积电7nm工艺,晶体管集成度提高,性能和能耗比也有大幅提升。 近期,据驱动之家报道,半导体业内人士称,Intel将其南桥芯片组的生产外包给了三星,GPU芯片则委托给台积电代工生产,将使用台积电的4nm工艺。 这几年Intel销量占比持续下降,为了提高市场占

2021-01-25 17:58:53 2224

2224 ,3nm工艺是今年下半年试产,2022年正式量产。 与三星在3nm节点激进选择GAA环绕栅极晶体管工艺不同,台积电的第一代3nm工艺比较保守,依然使用FinFET晶体管。 与5nm工艺相比,台积电3nm工艺的晶体管密度提升70%,速度提升11%,或者功耗降低27%。 不论是5nm还是3nm工

2021-02-19 15:13:40 2778

2778 。 原文如下: 说点题外话,大家就当看个热闹吧,既然说旧工艺的“叠加”,那咱就聊聊叠加嘛。 首先还是强调一点,现在所谓的几 nm 工艺,这个几 nm 的数字并不是指晶体管的 gate length(或沟道长度)——很多人对此是存在误解的。比如台积电的 7nm 工艺,晶体管并不存在

2021-07-02 16:39:34 6837

6837 半导体制程已经进展到了3nm,今年开始试产,明年就将实现量产,之后就将向2nm和1nm进发。相对于2nm,目前的1nm工艺技术完全处于研发探索阶段,还没有落地的技术和产能规划,也正是因为如此,使得1nm技术具有更多的想象和拓展空间,全球的产学研各界都在进行着相关工艺和材料的研究。

2021-12-17 15:18:06 12951

12951 1nm芯片是什么意思?目前芯片的代工工艺制程工艺已经进入3nm节点,在1nm芯片制造技术节点迎来技术突破。芯片的发展一直都很快,有消息称IBM与三星联手将实现1nm及以下芯片制程工艺。

2021-12-17 14:34:43 34377

34377 制程3,首次将5G Modem集成到SoC上,方寸之地集成了约103亿晶体管4,如发丝作画,非奇迹而不为。承袭并进化麒麟优秀基因,融合巴龙卓越5G能力,以硬核技术与超前智慧,决胜千里。麒麟990处理器的硬件参数。麒麟990处理器是采用了7nm制程工艺打造的八核处理器,CPU部分采用三丛集的设计,

2021-12-22 19:11:40 15

15 全球首颗2nm芯片已经被IBM研制出来了,在这一颗指甲盖大小面积的芯片上可以容纳500亿颗晶体管,芯片制程工艺的进步必将让半导体行业的发展越来越快。接下来我们详细了解下这款2nm芯片的特性、功耗等,跟7nm芯片做个对比,看下2nm芯片与7nm芯片之间有何差距。

2022-06-22 09:52:43 7529

7529 7nm和12nm指的是晶体管间的距离。在同等cpu面积下,距离越小,能够摆放的晶体管数量也就越多。那么,对于运算速度而言,晶体管越多,运算速度提高的可能性也就越大。

2022-06-23 15:58:37 9960

9960 我们在文中常说的7nm和12nm其实是工艺制程,也就是处理器的蚀刻尺寸,就是我们八一个单位的电晶体刻在多大尺寸的一块芯片上。

2022-06-24 09:58:19 4374

4374 的重要性,我国目前最先进的制程7nm还正在研发当中,那么2nm芯片与7nm芯片的差距有多大呢? 拿台积电的7nm举例子,台积电最初用DUV光刻机来完成7nm工艺,当时台积电7nm工艺要比上一代16nm工艺密度高3.3倍,性能提升达到了35%以上,同样性能下功耗减少了65%,在当时

2022-06-24 10:31:30 5966

5966 目前手机处理器的工艺制程是7nm,台积电也即将量产5nm芯片,未来还有2nm甚至1nm芯片的出现。台积电的研发负责人曾在谈论半导体工艺极限的问题时,认为到2050年,晶体管可达0.1nm的氢原子尺度。

2022-06-24 16:10:03 26799

26799 已经进入了试产阶段,并且也从华为那边收取到了麒麟710A的订单,中芯国际表示过其12nm制程能够实现晶体管尺寸的缩减,相较于14nm制程,中芯国际的12nm制程将减少20%功耗和增加10%性能。 而相较于7nm芯片,12nm芯片在各方面就已经就难以追赶了,以麒麟980和麒

2022-06-27 11:19:34 6692

6692 最先进的制程工艺便是三星的3nm工艺,并且这也是全球首次采用GAA晶体管的芯片,三星表示采用了GAA晶体管的3nm芯片将应用在高性能低功耗的计算领域,并且未来将要运用到移动端。 目前三星3nm工艺芯片的首位顾客被爆料是一家来自中国的矿机芯片公司,随

2022-06-30 16:36:27 2953

2953 1 众所周知,芯片制程工艺越小,芯片的性能就会越好,功耗也会更低,而随着技术的发展,芯片制程工艺迎来了重要的7nm,而关于中芯国际12nm芯片的事又闹得沸沸扬扬,那么12nm芯片和7nm芯片哪个费电

2022-07-01 09:43:27 4693

4693 有多大呢?是2nm吗? 其实芯片前面的数字代表的是这款芯片所采用的制程工艺,2nm即为2nm制程工艺,而制程工艺又特指芯片内部晶体管的栅极最小长度,栅极是晶体管内用于控制电流的结构,因此2nm即代表着芯片内部晶体管最小栅极长度为2nm,并不是代表整

2022-07-04 09:15:36 5743

5743 到2007年,当时Intel公司在旧金山举办了一场演讲,在那场演讲中,Intel CEO展示了一款32nm制程的芯片,他表示该芯片中集成了超过19亿个晶体管,Intel将会在2009年正式量产32nm制程工艺的芯片。 2010年Intel推出了Corei7≤980X,这款芯片采用了32nm制程工艺

2022-07-04 09:47:46 4648

4648 在芯片设计和制造中,纳米表示的是芯片中晶体管与晶体管之间的距离,在体积相同大小的情况下,7nm工艺的芯片容纳的晶体管的数量,几乎是14nm工艺芯片的2倍。

2022-07-06 16:53:46 28009

28009 三星3nm采用的晶体管架构是GAAFET,也被称为Nanosheet,而1nm制程对晶体管架构提出了更高的要求。

2022-09-05 15:03:57 5987

5987 及三星这三大芯片厂商也在冲刺,其中三星首个宣布2027年量产1.4nm工艺,台积电没说时间点,预计也是在2027年左右。 1.4nm之后就是1nm工艺了,这个节点曾经被认为是摩尔定律的物理极限,是无法实现的,但是现在芯片厂商也已经在攻关中。 台积电已经启动了先导计划,传闻中的1nm晶圆

2022-10-31 11:06:30 2457

2457

在 VLSI 2021 上,imec 推出了 forksheet 器件架构,以将纳米片晶体管系列的可扩展性扩展到 1nm 甚至更领先的逻辑节点。

2022-11-01 10:50:42 4281

4281

然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

2023-05-30 14:24:48 2131

2131

然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

2023-05-31 15:45:29 2196

2196

制程的小尺寸可以实现更高的晶体管密度,让芯片在相同尺寸内集成更多的晶体管,从而提供更好的性能和速度。然而,制程的大小并不是唯一衡量芯片性能的因素。三星的5nm,也未必就一定比英特尔的7nm强。

2023-09-12 15:34:33 26031

26031 上次我的文章解释了所谓的7nm不是真的7nm,是在实际线宽无法大幅缩小的前提下,通过改变晶体管结构的方式缩小晶体管实际尺寸来达到等效线宽的效果那么新的问题来了:从平面晶体管结构(Planar)到立体

2023-12-19 16:29:01 1396

1396

最近网上因为光刻机的事情,网上又是一阵热闹。好多人又开始讨论起28nm/7nm的事情了有意无意之间,我也看了不少网上关于国产自主7nm工艺的文章。不过这些文章里更多是抒情和遐想,却很少有人针对技术

2024-10-08 17:12:49 1339

1339

电子发烧友App

电子发烧友App

评论