PAM4(4-Level Pulse Amplitude Modulation) 的全称是四电平脉冲....

AMD Alveo 加速卡使用有两种流程,AMD Vitis Software Platform f....

欢迎参加本次网络研讨会,我们将深入探讨 AMD Alveo V80 计算加速器如何帮助您处理高性能计....

AMD 第二代 AMD Versal AI Edge 和 Versal Prime 系列助力 AI ....

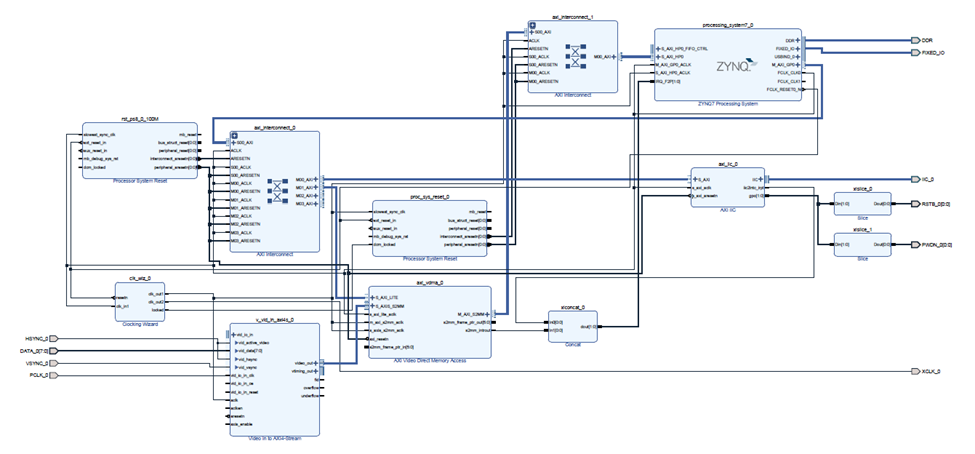

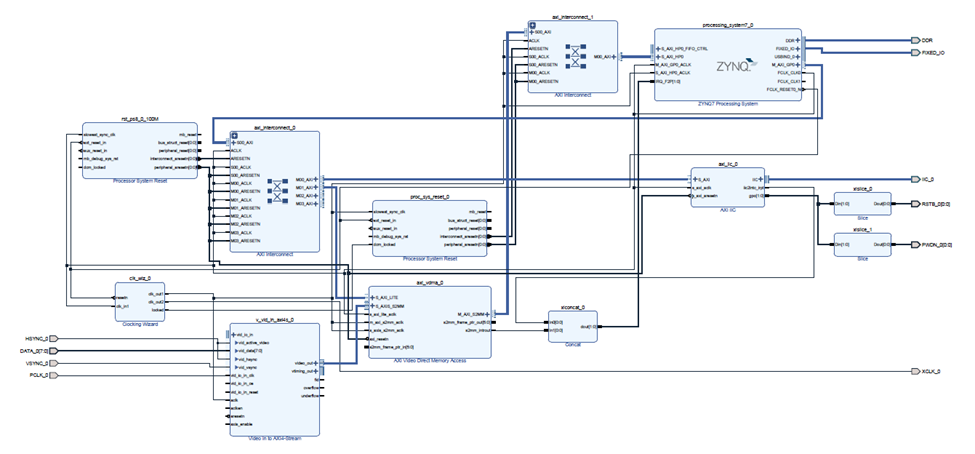

本文参考设计基于 AMD ZYNQ 7000 Device, 使用 VDMA 做原始图像采集系统,在....

本文将从硬件设计和驱动使用两个方面介绍基于 CPM5 QDMA 的 AMD Versal 自适应 S....

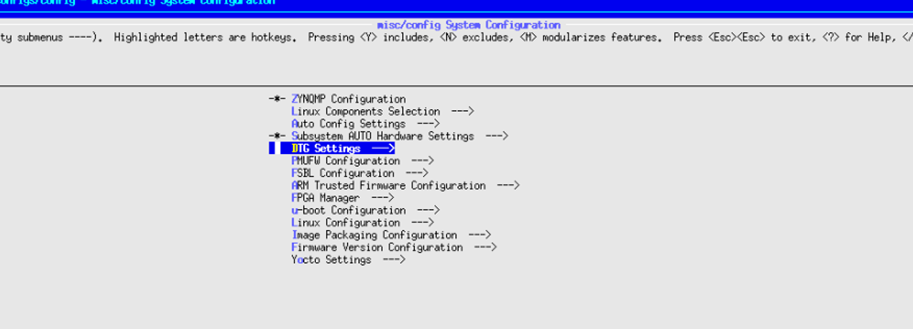

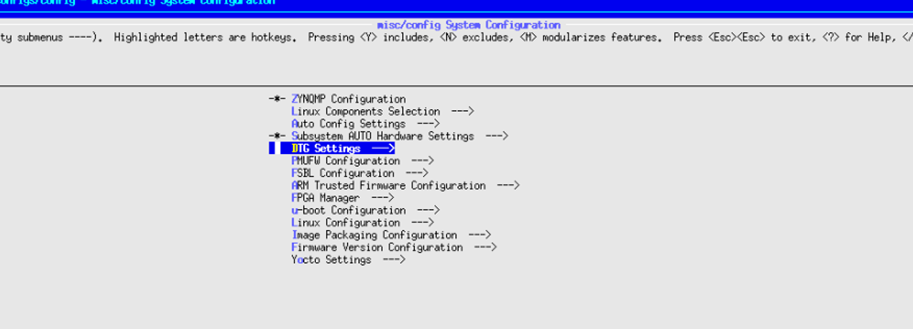

设置好 2022.2 Petalinux 环境。使用 2022.2 ZCU06 BSP,创建 Pet....

本篇文章介绍了在 ZCU106 上创建 Video Multi-Scaler IP 的 AMD Vi....

AMD Vitis™ 2023.2 设计工具是 Vitis 设计工具变化较大的一个版本,设计流程和界....

本文可让开发者们看懂 AMD Vivado Design Tool 2023.2 中的“AMD Ve....

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使....

注释:默认 DCMAC 设计示例不包含 NoC DDRMC

本文介绍了在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程以及需要....

系统看门狗定时器(System WatchDog Timer)通常用于嵌入式系统,可以有效的防止软件....

随着嵌入式 AI、视频和控制应用取得爆发式增长,在严格的占板面积和功耗限制下,对于借助异构处理能力加....

Vitis Embedded 是一款独立的嵌入式软件开发套件,主要用于为 AMD 自适应 SoC 和....

在 AMD Versal™ 器件中, SEM 功能的实现发生了很大变化,整个解决方案基于 libra....

在构建嵌入式应用的过程中,硬件设计人员长期以来面临着艰难的取舍,为推动产品快速上市,他们必须在成本、....

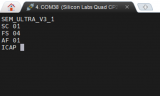

IP 在初始化阶段就卡住了。从 Uart 口的 log 看 ‘ICAP’ 后续无字符输出,这是典型的....

在硬件调试时,经常需要用 ILA 采集一些 FPGA 内部或者对外的初始化信号,然而在下载完 Bit....

最后我们需要生成能够在 AMD Kria KR260 上运行的固件。

在上一篇文章中 开发者分享|AMD Kria KR260 DPU 配置教程 1 我们导出了 plat....

这篇文章我们将为 AMD Kria KR260 在 AMD Vitis 上创建硬件加速平台。 我们将....

Vitis Vision 库是一组 90 多个内核,基于 OpenCV 计算机视觉库,针对 AMD ....

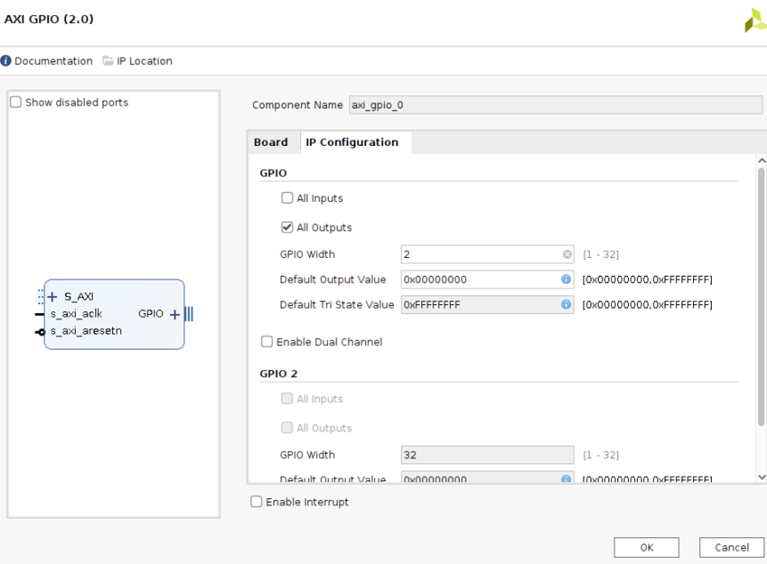

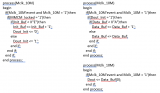

在 AMD SoC 器件(AMD Zynq 7000 SoC,AMD Zynq UltraScal....

由于市场环境日益复杂、产品竞争日趋激烈,为了加快推出新型自适应 SoC 和 FPGA 设计,硬件设计....

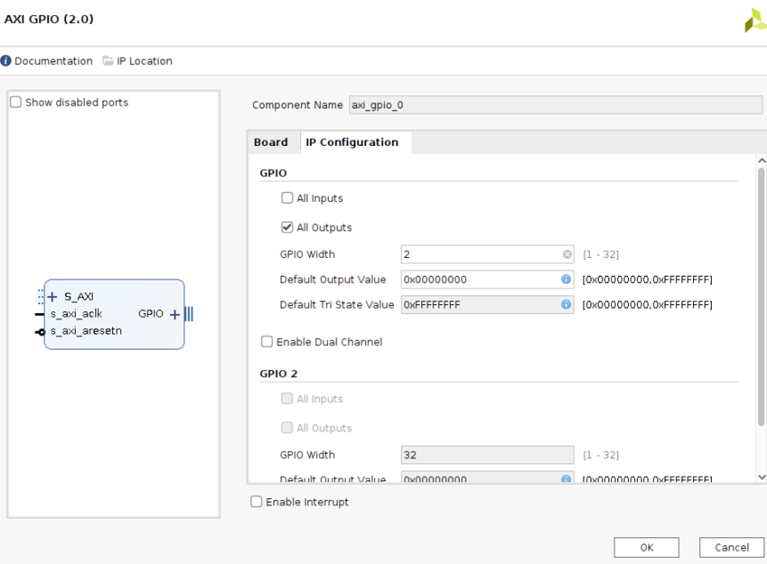

AMD ZYNQ 7000 的 S_AXI 端口提供了外设访问 PS 内部外设控制器的接口,这其中包....

使用可编程逻辑器件进行设计时,最关键的步骤之一就是为应用选择最佳的器件。

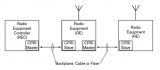

CPRI 是无线通信里的一个标准协议,连接 REC 和 RE 的通信。AMD 有提供 CPRI IP....

目前 AMD 的以太网 IP 核,如软核 10G/25G,40G/50G 或者硬核 CMAC,MRM....