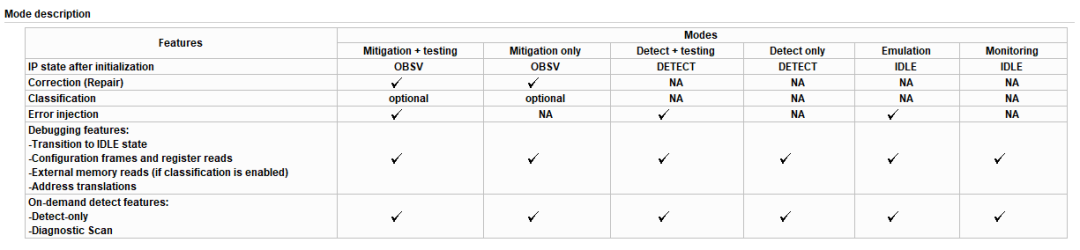

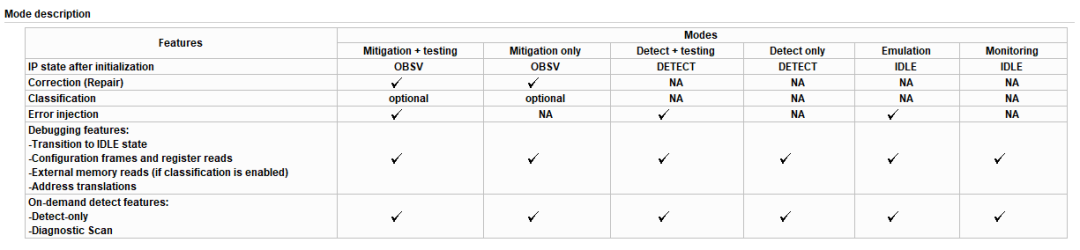

UltraScale / UlraScale+系列的SEM IP一共有6种工作模式

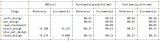

影响编译时间的因素有很多,包括工具流程、工具设置选项、RTL 设计、约束编辑、目标器件以及设计实现期....

在设计周期中,您可保留多个版本的工程,这些工程使用相同的 IP 和相同的配置。重新运行整个工程会导致....

这篇博文介绍了多种自动生成报告的有效途径,以便您在尝试对设计中特定阶段所耗用的编译时间进行调试时使用....

增量综合的工作方式与增量实现流程相似,但仅适用于综合阶段,并且不会对紧随其后的实现阶段给予引导。

PDM 已经与其它 AMD FPGA 和自适应 SoC 工具一起集成到统一的安装程序中。这是一款独立....

增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。

自从 Vitis 的发布,AMD 在 Github 上也开源了很多资源,方便开发者进行自己的设计,减....

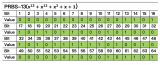

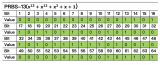

目前对于 Vivado 2023.1 版本的 IBERT GUI 界面暂时不支持 QPRBS13 的....

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可....

需要手工在 C++ 代码里明确指定可并行执行的任务(用 task,添加头文件 hls_task.h)....

在 Vitis 流程中,编译的目标分为软件仿真(software emultion),硬件仿真(ha....

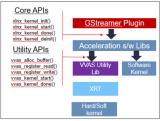

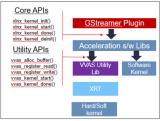

本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS ....

Vitis 视频分析 SDK 是在 AMD 平台上构建 AI 驱动的智能视频分析解决方案的完整软件栈....

在本篇博文中,我们来聊聊“RQS_CLOCK-12”时钟设置建议以及它如何帮助达成时序收敛。

Report QoR Suggestions (RQS) 可识别设计问题,并提供工具开关和可影响工具....

Vitis AI 平台是为 AMD 器件、板卡及 Alveo 数据中心加速卡提供的一款综合 AI 推....

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF)....

这篇博客展示了在 AMD Zynq 设计中,如何用 Vitis Vision Library 中的函....

标准协议的规范中一般都对眼图模板都有详细的规定,使用 IBERT 完成眼图扫描后,通过设置一些参数,....

MicroBlaze CPU 是可修改的拖入式预设 32 位/64 位 RISC 微处理器配置系列。

本文介绍如何使能 Linux 网络协议栈中的 RFS(receive flow steering)功....

要为 Versal 的多个 Quad 创建收发器设置,建议从 Transceiver Bridge ....

当使用第三方综合器比如 Synopsys Synplify Pro 或 Mentor Graphic....

Versal HBM 栈可通过内部 HSM0 参考时钟来进行时钟设置,此参考时钟是由 CIPS 或外....

Vitis Model Composer 是一个基于模型的设计工具,不仅可在 MathWorks M....

在 Vivado 内,以 Versal 器件为目标创建一个示例,此示例将以 VCK190 开发板为目....

在上述两种情况下,用户始终都能使用 “Refresh Project Models”(刷新工程模型)....

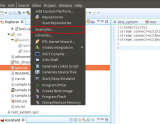

在本快速入门演示中,将探讨如何在 Vitis 中使用 Git 集成以及如何使用团队操作来共享 Vit....

Versal 系列的 DMA axi bridge 模式可以在 PL 的 QDMA IP 或者在 C....