本篇文章将介绍针对 NoC DDRMC LPDDR4 的 DCMAC 设计示例的硬件测试。

注释:默认 DCMAC 设计示例不包含 NoC DDRMC:

接下来的步骤:

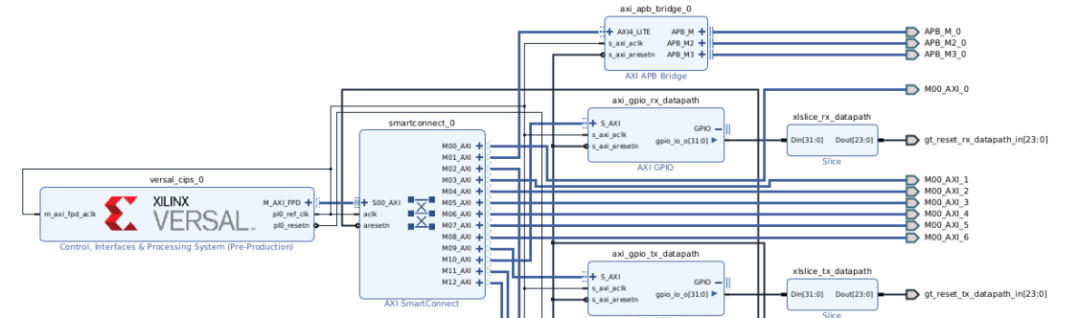

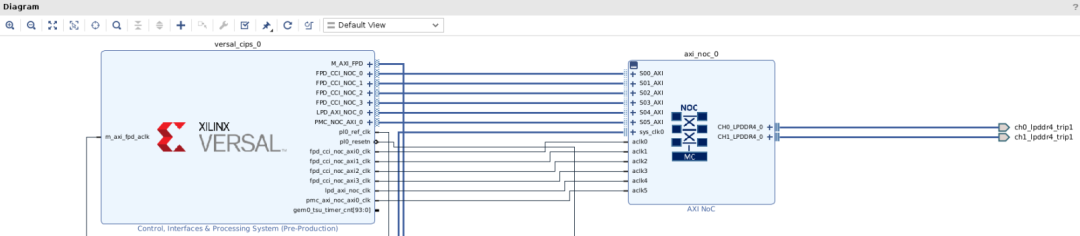

按下图所示,配置 NOC DDRMC 并连接到 CIPS。

在 XDC 文件中为所选器件/开发板编写约束。此处目标开发板是 VPK120 评估板。

单击 Generate Device Image。从“Synthesis” 开始操作,经过“Implementation”,然后生成镜像 (.pdi)。

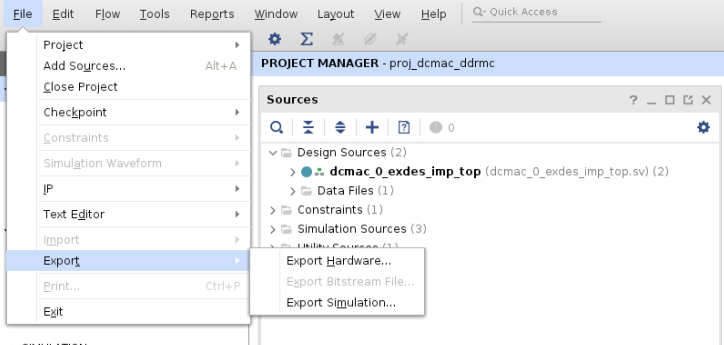

生成镜像后,请导航到“File → Export → Export Hardware”以导出硬件用于创建应用。

导航到.xsa文件所在路径并单击 Finish 以生成该文件。选择 Tools → Launch AMD Vitis IDE,以使用 VitisIDE 创建应用。

提供工作空间路径以创建应用。设置完成后就会启动 Vitis 窗口。

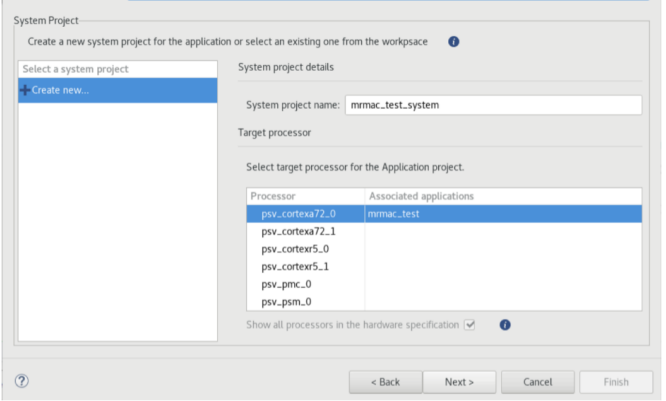

选择 Create Application Project。

浏览导出的硬件文件 (.xsa) 路径。

输入应用工程名称(例如,dcmac_lpddr4),然后单击“Next”。

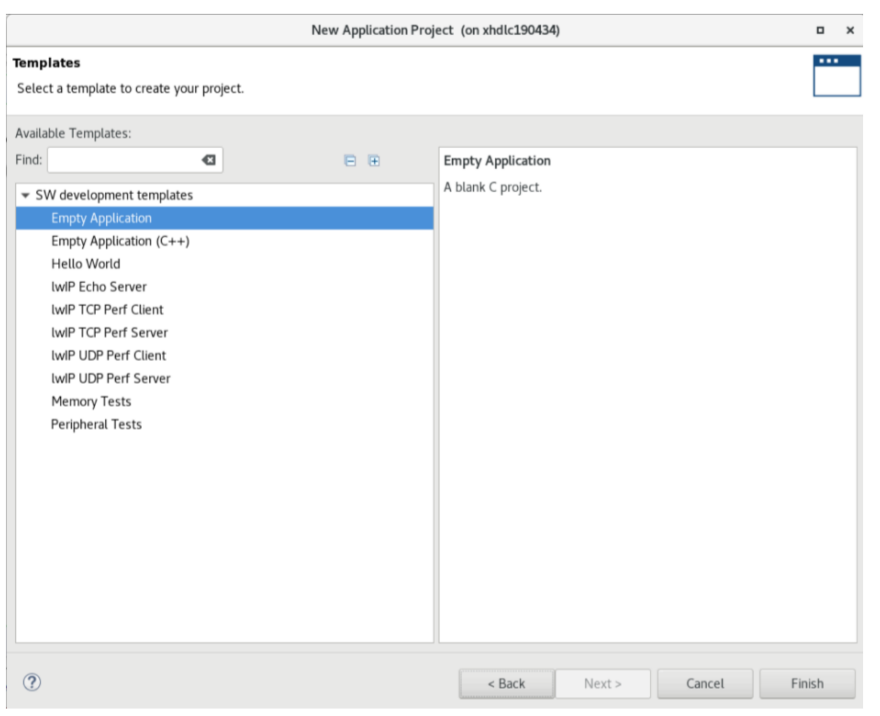

选择 Empty Application,然后单击“Finish”。

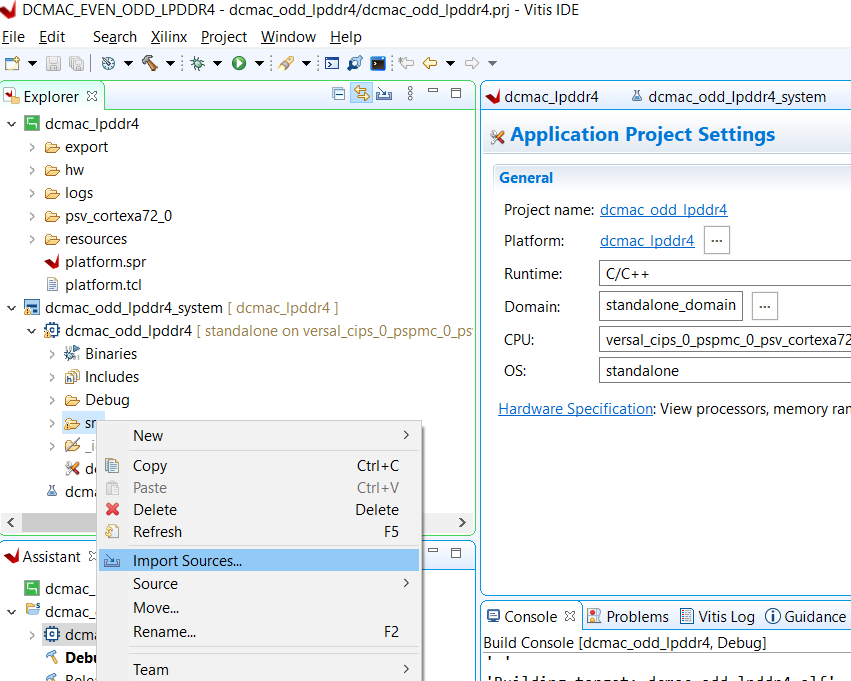

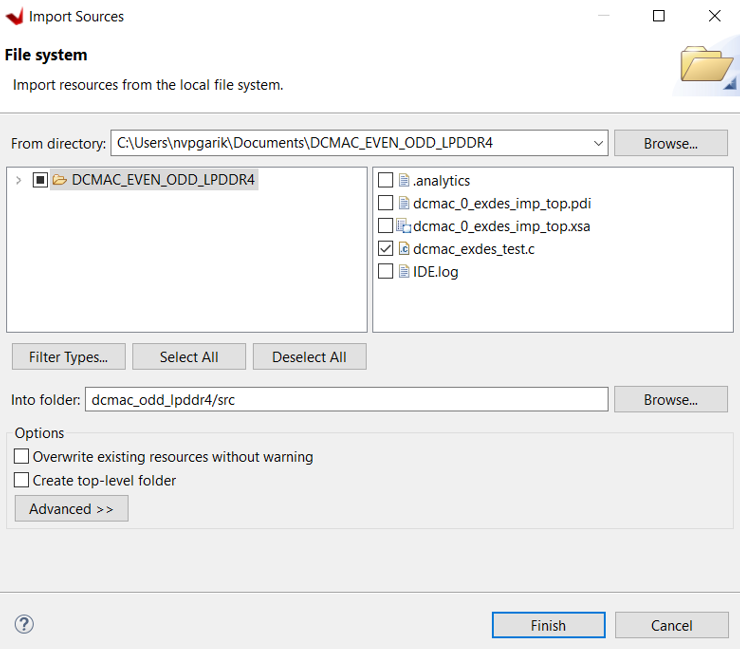

将 C 语言文件添加到应用中。右键单击“Source”,然后选择“Import Sources”。

指定“Import Sources”窗口浏览路径:

./dcmac_0_ex/ dcmac_0_ex.gen/sources_1/bd/dcmac_0_core_support/ip/ dcmac_0_core_support_dcmac_0_core_0/sample_c_files/,

选中 dcmac_0_exdes_test.c,然后单击“Finish”。

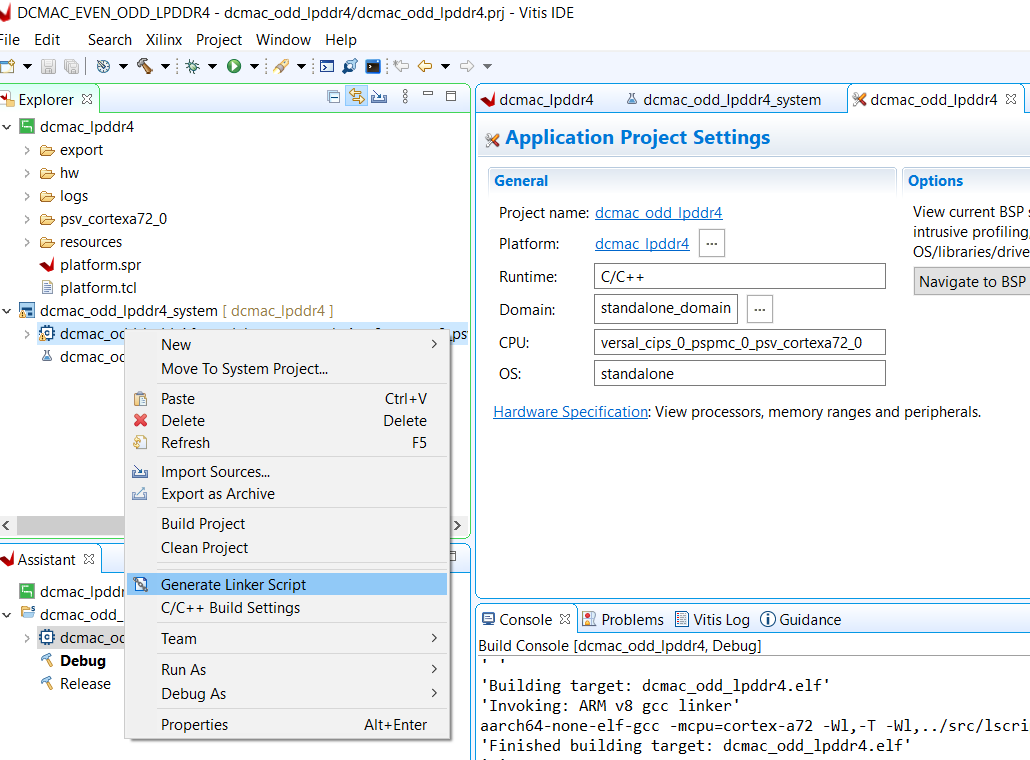

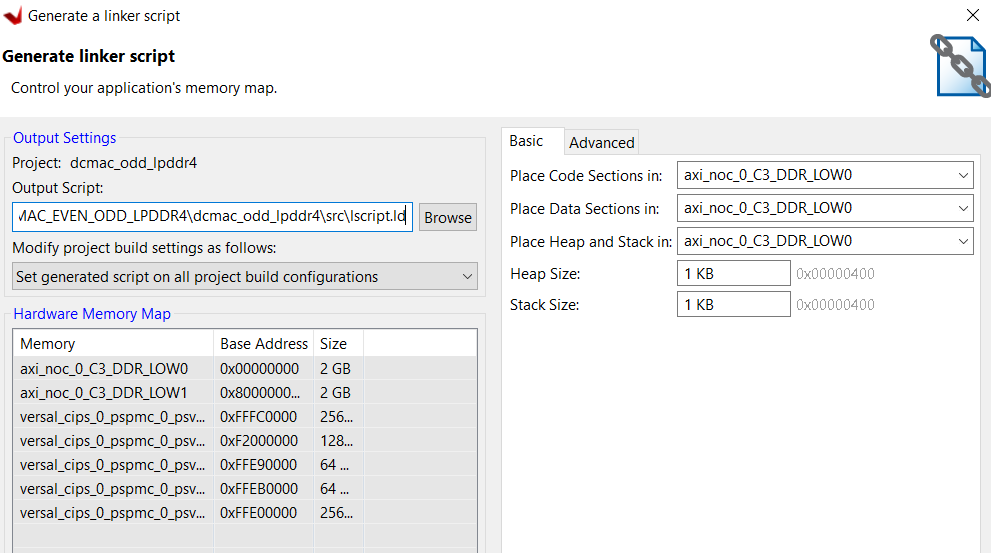

请确保在连接器脚本中选中 LPDDR4(axi_nox_ddr)。

连接器脚本:

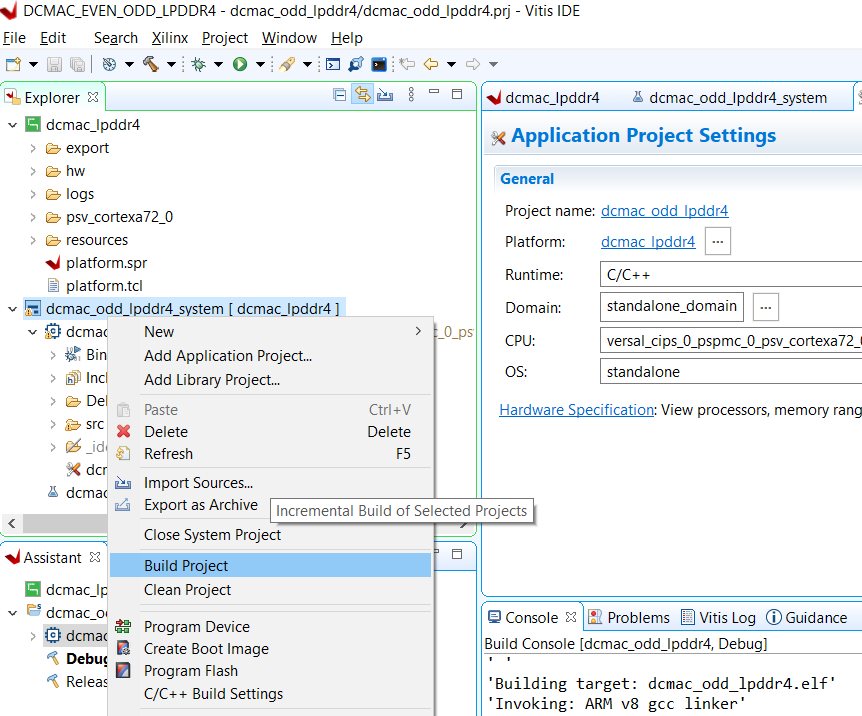

构建工程。此操作会使“Debug”文件夹内生成 .elf 文件。

在 VPK120 评估板上确认设计:

当比特流 (.pdi) 文件和应用文件 (.elf) 全部就绪后,给 AMD VersalAdaptive SoC 开发板上电。

在转储 MRMAC 镜像前,请使用 BEAM 工具按所需参考频率来配置器件。

BEAM 工具步骤:

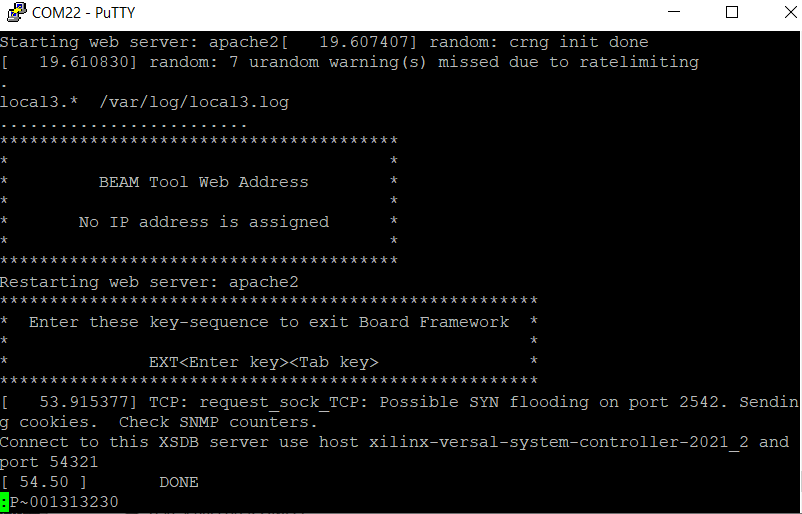

给 AMD Versal Device 上电,并连接到 Console(此处是 VPK120 评估板)。

输入 EXT,随后按 Enter 回车键和 Tab 跳格键。

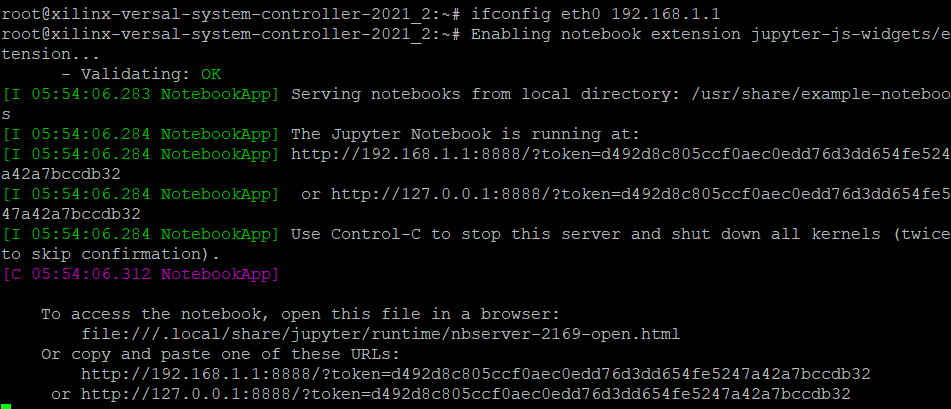

输入 if config eth0 192.168.1.1

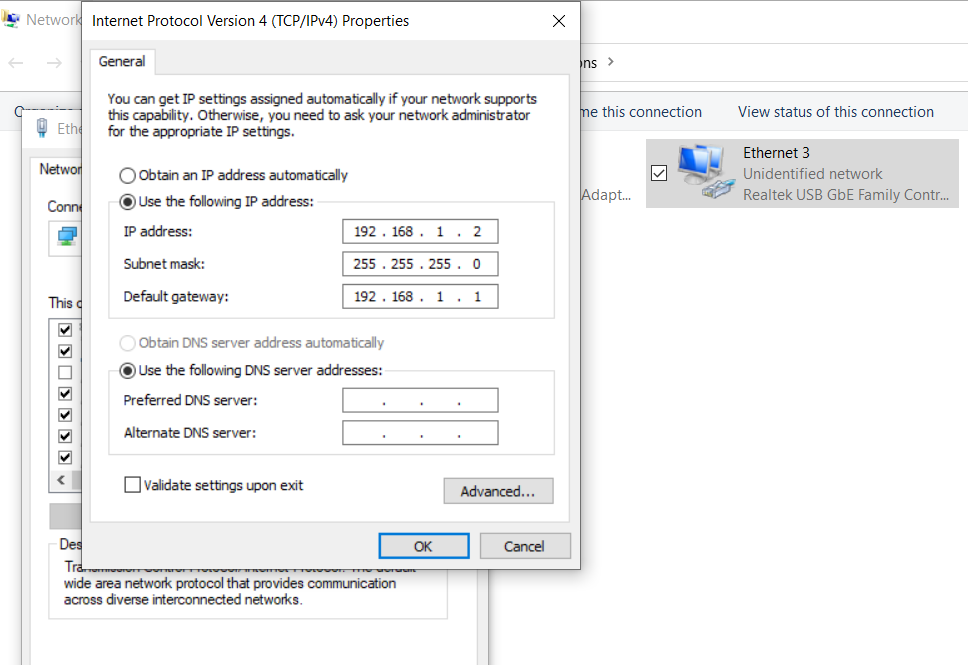

将本地计算机配置为 192.168.1.2。

用以太网线缆从本地计算机连接到 VPK120 评估板,并检查以太网链接的连接情况。

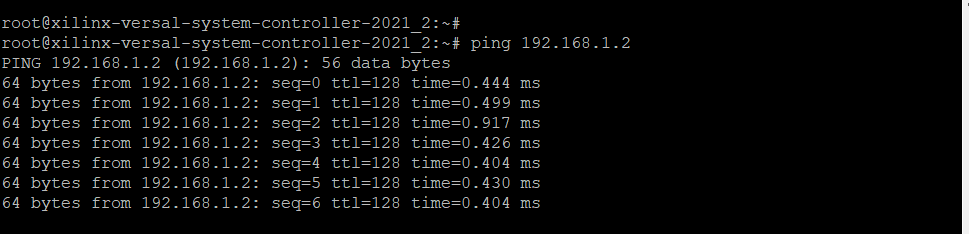

ping 192.168.1.2

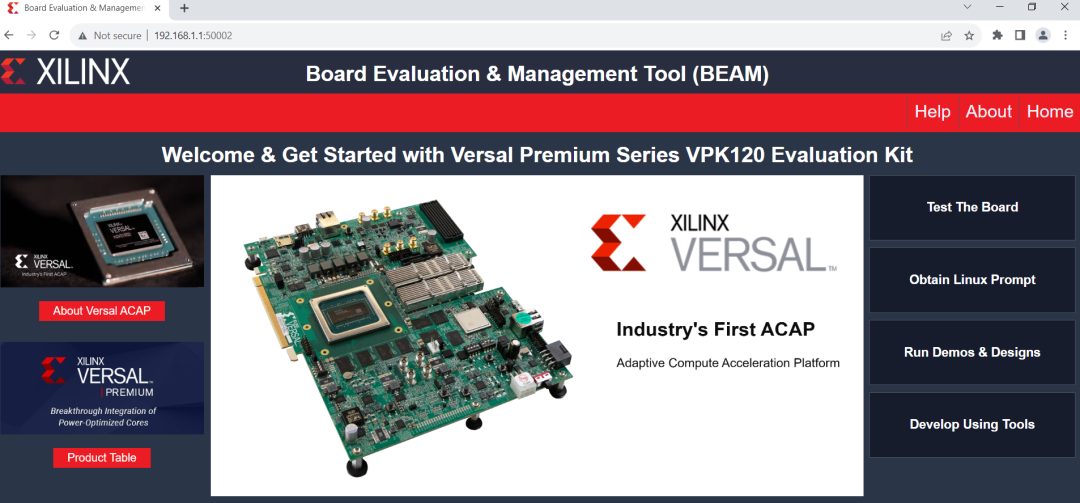

在本地计算机浏览器中,输入 192.168.1.1:50002

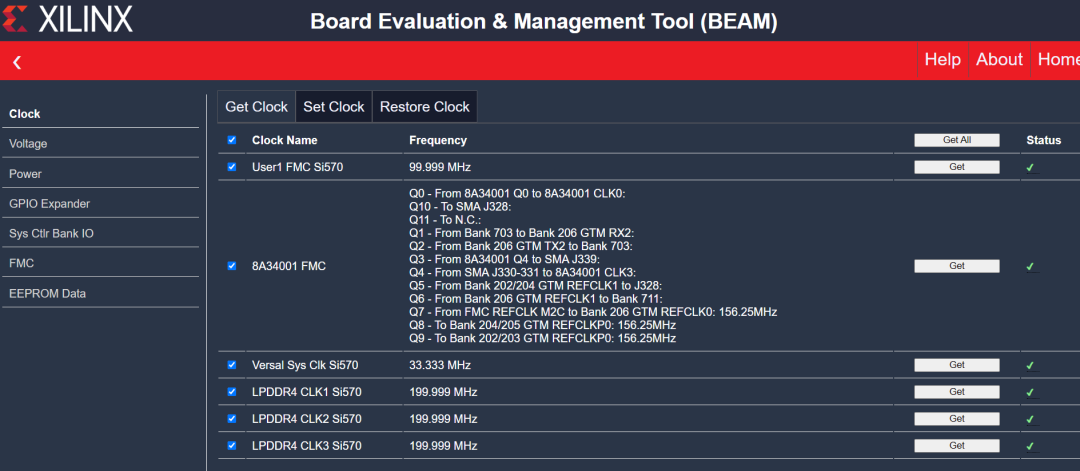

单击“Test The Board”(测试开发板),并设置时钟。

DCMAC GTM REFCLK:156.25 MHz(与 DCMAC IP GUI 配置相匹配)

NoC DDRMC LPDDR4:200MHz(与 NoC DDRMC IP GUI 配置相匹配)

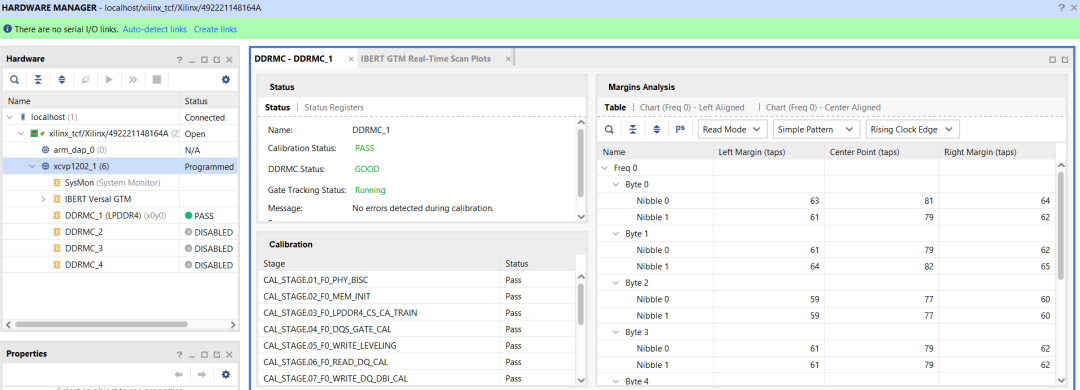

存储器状态:

打开硬件管理器并对生成 PDI 进行编程。

检查校准状态是否是 PASS。

如果校准状态为 FAIL,则请务必复查 NOC DDRMC 配置、时钟设置、复位,然后执行存储器接口调试。

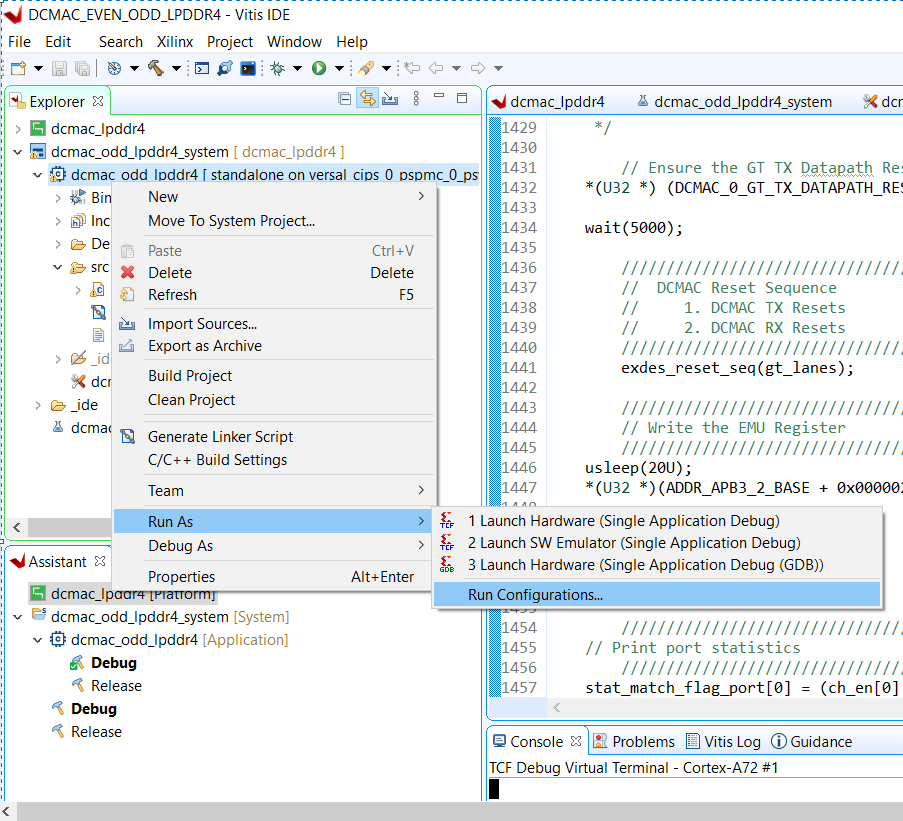

DCMAC 设计示例运行:

返回 AMD Vitis Platform 并运行配置。

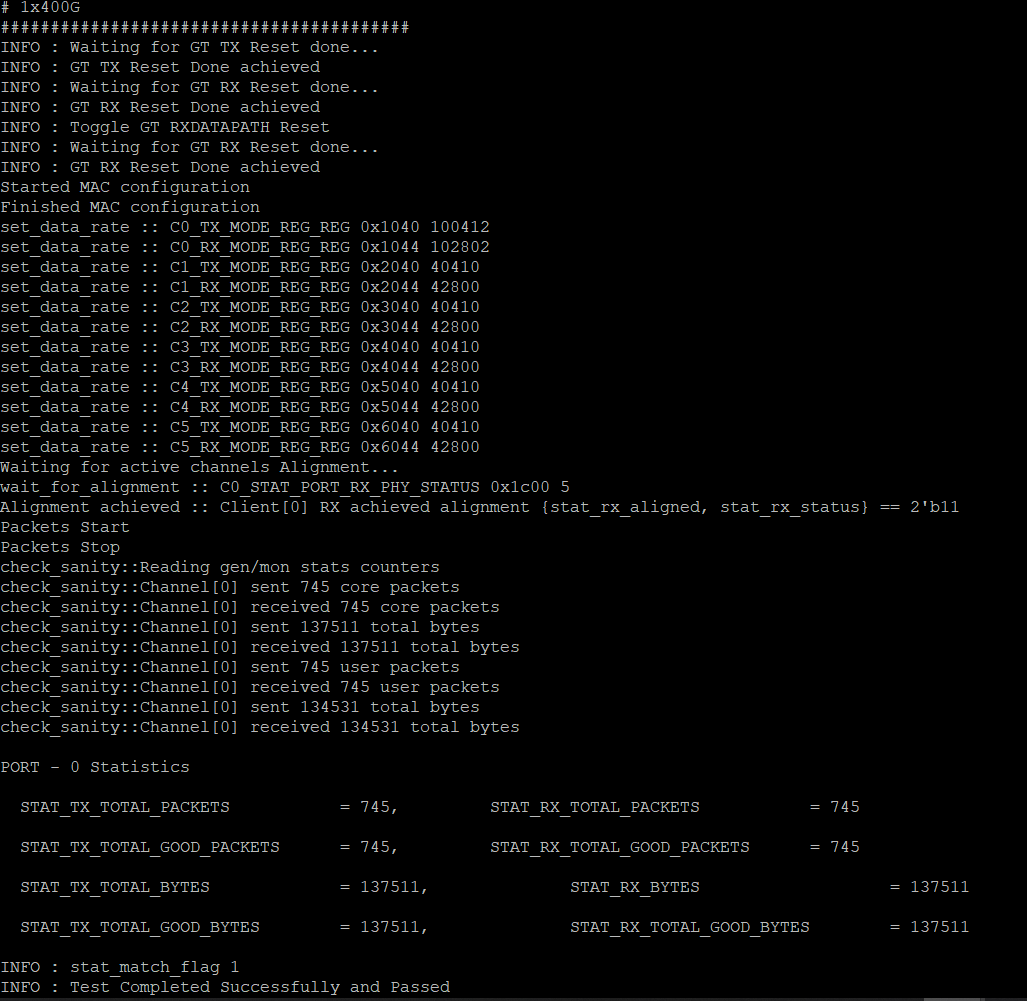

在控制台/Tera Term 中复查结果。

总结:

当 DCMAC IP 示例设计配置为“Even Active Lanes”时,通道 0 和通道 2 处于活动状态;当 DCMAC IP 示例设计配置“Odd Active Lanes”时,通道 1 和通道 3 处于活动状态。

注释:除“Transceiver Config Protocol”中的“Advanced Receiver”设置外,建议不要手动更改配置。但这会导致 write_bd_tcl运行失败。

-

以太网

+关注

关注

41文章

5924浏览量

179541 -

连接器

+关注

关注

102文章

15922浏览量

145421 -

计算机

+关注

关注

19文章

7764浏览量

92688 -

SoC芯片

+关注

关注

2文章

662浏览量

36837 -

UART接口

+关注

关注

0文章

124浏览量

16307

原文标题:开发者分享|NoC DDRMC LPDDR4 上运行 AMD Versal™ Adaptive SoC DCMAC 设计示例

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

AMD 7nm Versal系列器件NoC的使用及注意事项

论手机运行内存 LPDDR 4X在LPDDR4的基础上有哪些提升

lpddr4频率无法修改怎么解决?

DDR4/LPDDR4硬核控制器I/O plannin的设计和实现

使用用户为 LPDDR4 和 x8 或 x16 DDR4 组件接口指定的 DQS 字节交换生成管脚分配时,其中可能包含错误且需更改

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部参考时钟设计指南

AMD Versal系列FPGA NoC介绍及实战

LPDDR4是什么意思?LPDDR4X内存是什么意思?

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

NoC DDRMC LPDDR4上运行AMD Versal™ Adaptive SoC DCMAC设计示例

NoC DDRMC LPDDR4上运行AMD Versal™ Adaptive SoC DCMAC设计示例

评论