在硬件调试时,经常需要用 ILA 采集一些 FPGA 内部或者对外的初始化信号,然而在下载完 Bitstream 后立即采集这些变化稍纵即逝的信号,比如在 1uS 内手动触发 ILA 采集信号,以普通人的手速显然是无能为力的。有的变通方法比如在程序中加入一定的延时量或者外部按键做触发 ILA 采集也可以实现。但是某些应用场景下,初始化必须在上电后的一定时间范围内完成。本文将介绍一种可适用于上述场景的方法,即在下载 Bitstream 后自动触发 ILA 采集,为硬件调试提供更多便利。

调试方法:

1. 设备信息

操作系统:Win10

硬件平台:Xilinx VCU118开发板

软件版本:AMD Vivado2022.1

2. 代码分析

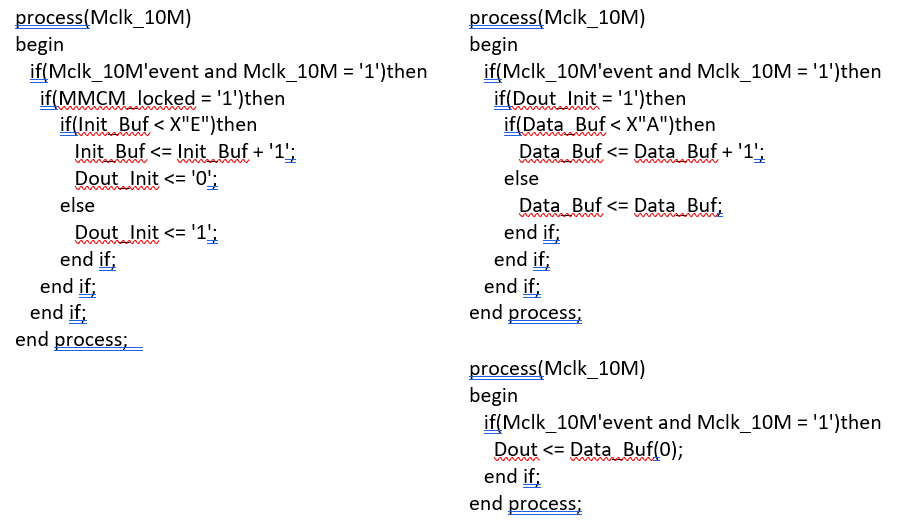

当 MMCM 初始化完成,Locked 信号置1后,Init_Buf 开始计数,当 Init_Buf 等于 0x0E 时,Dout_Init 置1触发 Data_Buf 开始计数,最终控制 Dout 输出5个脉冲。整个过程大约在 1uS 内结束,普通人的手速是无法在如此短的时间内采集到这组信号。

3. Vivado 操作步骤

打开 Vivado,新建工程按照常规流程完成 synthesis 后,点击 Setup Debug,将 Data_Buf, Dout, MMCM_locked, Dout_Init, Init_Buf 这些信号加入到 ILA 中,设置 100MHz 的时钟作为 ILA 的采集时钟。

Implementation 后 Generate Bitstream 并且下载到 FPGA。

此时可以看到之前连接到 ILA 的信号都已经显示,设置 ILA 的触发条件,本工程设置为当 Dout_Init =1 时触发 ILA 采集。

运行

cdc:/ILA_Startup/ILA_Startup.runs/impl_1/

粗体部分可设置为任意的工程路径,这样便于在生成 bit 以后找到对应的文件。

在 Tcl Console 窗口输入:

run_hw_ila -file ila_trig.tas [get_hw_ilas hw_ila_1] -force

Open implementation design,在Tcl窗口输入:apply_hw_ila_trigger ila_trig.tas

在Tcl窗口输入:

write_bitstreamc:/ILA_Startup/ILA_Startup.runs/impl_1/trig_at_startup.bit -force

粗体部分可设置为任意的工程路径。

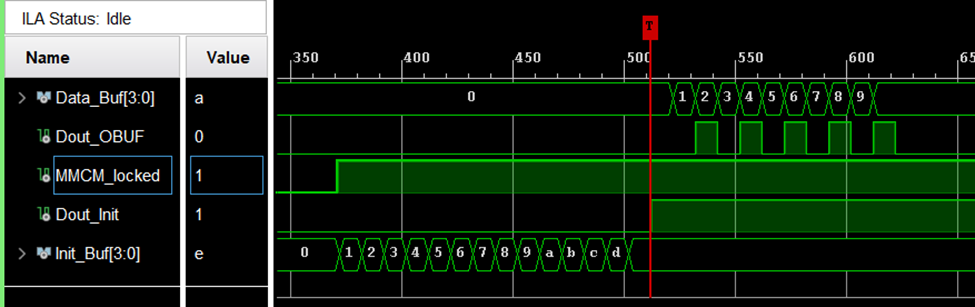

把新生成的 trig_at_startup.bit 通过 JTAG 下载到器件,下载完成后可以看到 ILA 将自动触发采集信号,如下图所示:

注意事项:

改变 ILA 的触发条件后,需要重复上面 Step4- Step7 的步骤。

改变 ILA 的信号连接后,需要重复上面 Step2- Step7 的步骤。

审核编辑:汤梓红

-

FPGA

+关注

关注

1603文章

21328浏览量

593251 -

操作系统

+关注

关注

37文章

6289浏览量

121897 -

开发板

+关注

关注

25文章

4436浏览量

94053 -

ILA

+关注

关注

0文章

5浏览量

3506

原文标题:开发者分享|AMD Vivado Hardware Debug 技巧-如何在下载 Bitstream 后自动触发 ILA 采集

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何实现ILA Cross Trigger

请问怎么在Vivado中保存Bitstream文件?

如何在下载flash图像时从IAR编程选项字节

如何使用AXI配置的ILA调试PCIe AXI接口?

为什么在ILA中找不到信号?

LabVIEW如何控制工业相机软触发采集图像

Vivado在线调试方法-Vivado内嵌逻辑分析仪器的使用

什么是D-ILA投影技术

Vivado中关于ILA的详解

Vivado之ILA详解

如何在Vivado下设置BITSTREAM配置信息

ILA工作原理 ILA使用方法与注意

如何在下载Bitstream后自动触发ILA采集

如何在下载Bitstream后自动触发ILA采集

评论