本文将从硬件设计和驱动使用两个方面介绍基于 CPM5 QDMA 的 AMD Versal 自适应 SoC 的 Tandem 设计和启动流程。

Versal QDMA 的两个 PCIe 控制器都支持不同方式的 Tandem (Tandem PROM • Tandem PCIe)。和其他系列的 Tandem 选项一样,Tandem PROM 是 Tandem 配置的简化模式,只是其中两个阶段都包含在同一个 pdi 里面,用户可以把这个 pdi 文件存到 PROM 中,系统会先配置 CPM 然后再去配置其他部分这样就能比较容易的满足120ms 启动时间的要求。

而 Tandem PCIe 则更为复杂,它第二部分的加载基于 PCIe 链路,在 BD 设计中必须包含从 CPM MASTER 到 PMC Slave 的路径。而在 PMC 中需要使用特定的加载到的接口 Slave Boot Interface(SBI),其位于 AMD Versal设备地址 0x102100000。

Tandem PCIe 的软硬件流程

首先在 CPM 生成界面选择 DMA,把 Tandem mode 选择为 Tandem PCIE。第二页选择 QDMA,其他都可以用默认选项。

CIPS 的 PCIE Reset 复位选择和板上一致。

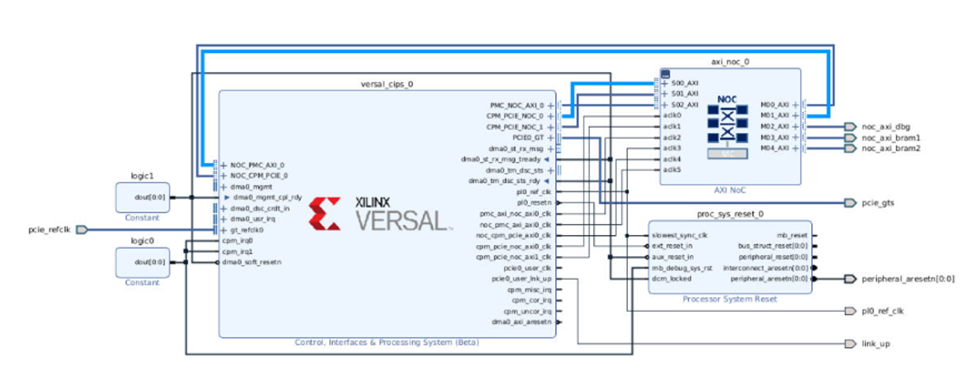

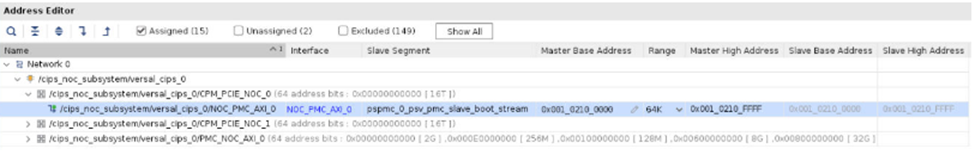

按照下图连接 BD,需要连上复位 sys_reset ,连接 NOC, 并且把 CPM 的 Master 和 PMC 的 Slave 连上, 按照下图把地址分配到 0x102100000 (slave boot stream), 这样 QDMA 的传输目标地址就设置为从 0x102100000 开始。NOC 另一侧可以连接 BRAM 和其他需要的用户侧 PL 逻辑。

由于工具并不会自动拉低 PL 的复位管脚所以用户必须写 XSDB (0xF1260330) 地址来拉低复位或者把 PL Reset 管脚从 CDO 中直接拉低并且重新生成 PDI。 如果 PL 的复位在 CIPS 外面,需要自己去控制这个复位保证加载完 pdi2 后 PL 可以工作。

生成 pdi 文件后,开始清除原来的驱动和加载新的驱动,以下为步骤。

首先可以通过 JTAG 或者 RPOM 的方式,把第一阶段的pdi 文件下载进去 并且重启主机。这个时候可以通过 lspci 看到 AMD Xilinx 的 bdf。然后准备好驱动和应用程序并运行以下程序。

获取最新的驱动程序, 驱动可以从网站下载:

https://github.com/Xilinx/dma_ip_drivers/tree/master/QDMA

从内核中删除旧模块(仅在必要时)。 $> rmmod qdma-pf

编译驱动程序和应用程序。 $> make -DTANDEM_BOOT_SUPPORTED

安装(复制)驱动程序和应用程序到标准位置。$> make install

载入内核模块。#> modprobe qdma-pf

产生 H2C 的队列。 $> dma-ctl qdma10000 q add idx 0 dir h2c mode mm

启动一个队列, aperture size 是4k $> dma-ctl qdma10000 q start idx 0 dir h2c aperture_size 4096

传输 pdi2,这里的大小和名字需要按照实际情况修改:

$> dma-ctl qdma10000_MM_0-f design_wrapper.pdi -s 1384992 -a 0x102100000

卸载驱动冲 i 性能加载驱动重复2-5。

用 xsdb 去写 o 0xF1260330,如果 pl_reset 连到了stag2 的逻辑上, 如果没有这步可以省略。

完成其他测试 ,比如 BD design 后面连了 ddr 或者 bram,可以用 dma_to_device 来测试 PL 是否能正确接收数据。

-

amd

+关注

关注

25文章

5703浏览量

140386 -

控制器

+关注

关注

114文章

17860浏览量

195017 -

soc

+关注

关注

40文章

4619浏览量

230080 -

硬件

+关注

关注

12文章

3626浏览量

69160 -

PCIe

+关注

关注

16文章

1474浏览量

88895

原文标题:开发者分享|AMD Versal™ 自适应 SoC CPM5 QDMA 的 Tandem PCIe 启动流程介绍

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

AMD Versal自适应SoC内置自校准的工作原理

Versal CPM AXI Bridge模式的地址转换

AMD率先推出符合DisplayPort™ 2.1 8K视频标准的FPGA和自适应SoC

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

利用AMD VERSAL自适应SoC的设计基线策略

AMD Versal CPM5 QDMA Gen4x8 ST Only Performance Design CED示例

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

评论