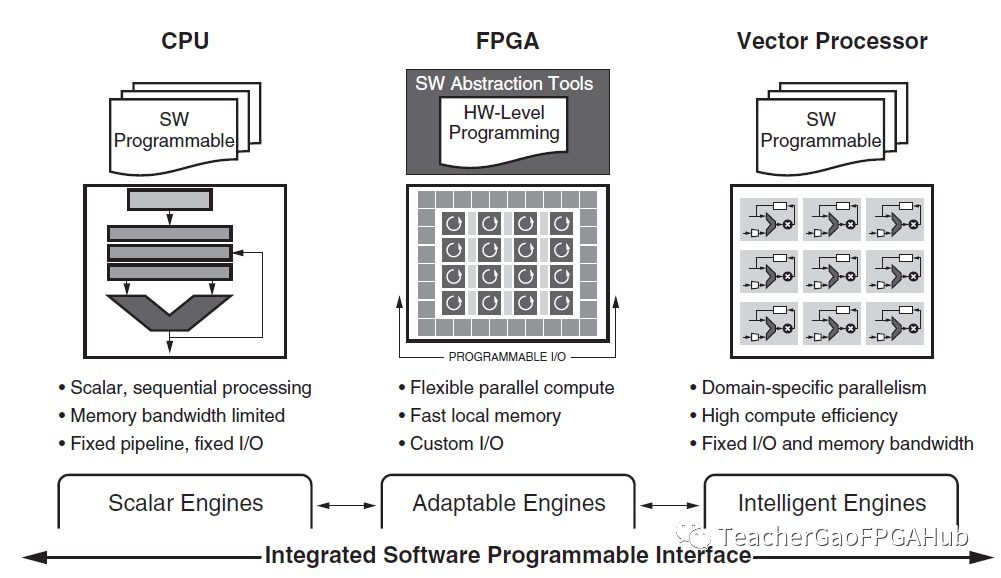

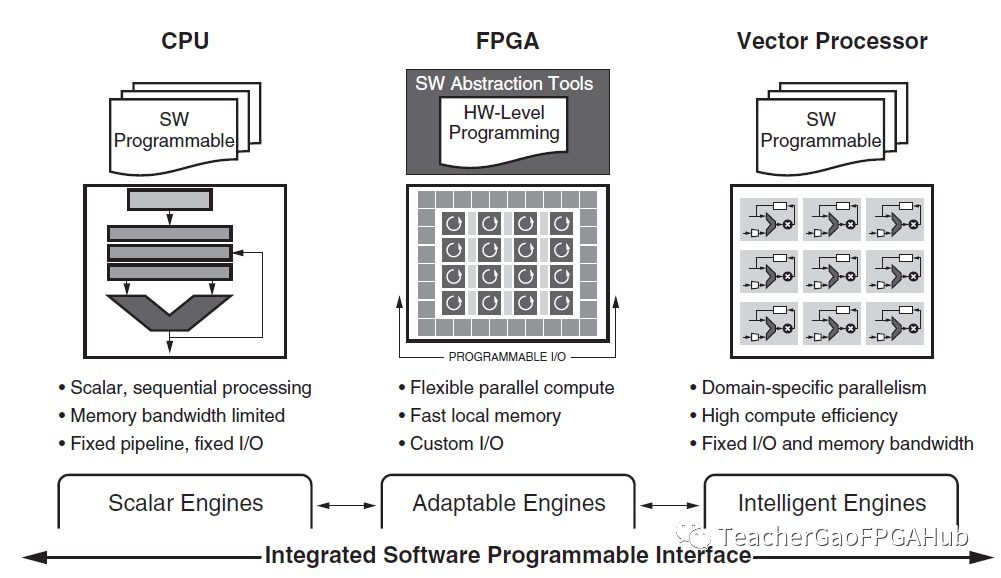

Versal中的三个引擎Versal芯片是业界第一款自适应加速计算平台(ACAP:Adaptive ....

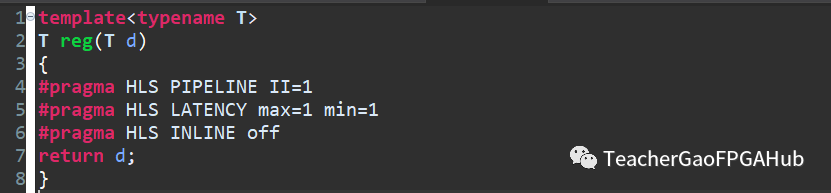

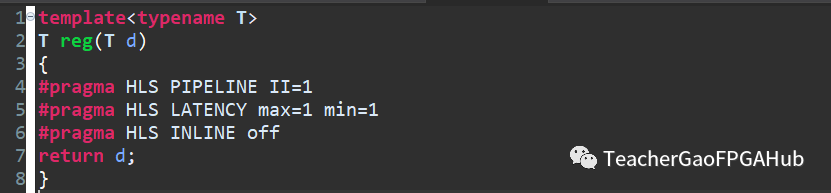

对于逻辑级数较高的路径,常用的方法之一是在其中插入流水寄存器,将路径打断,从而降低逻辑延迟,这在HD....

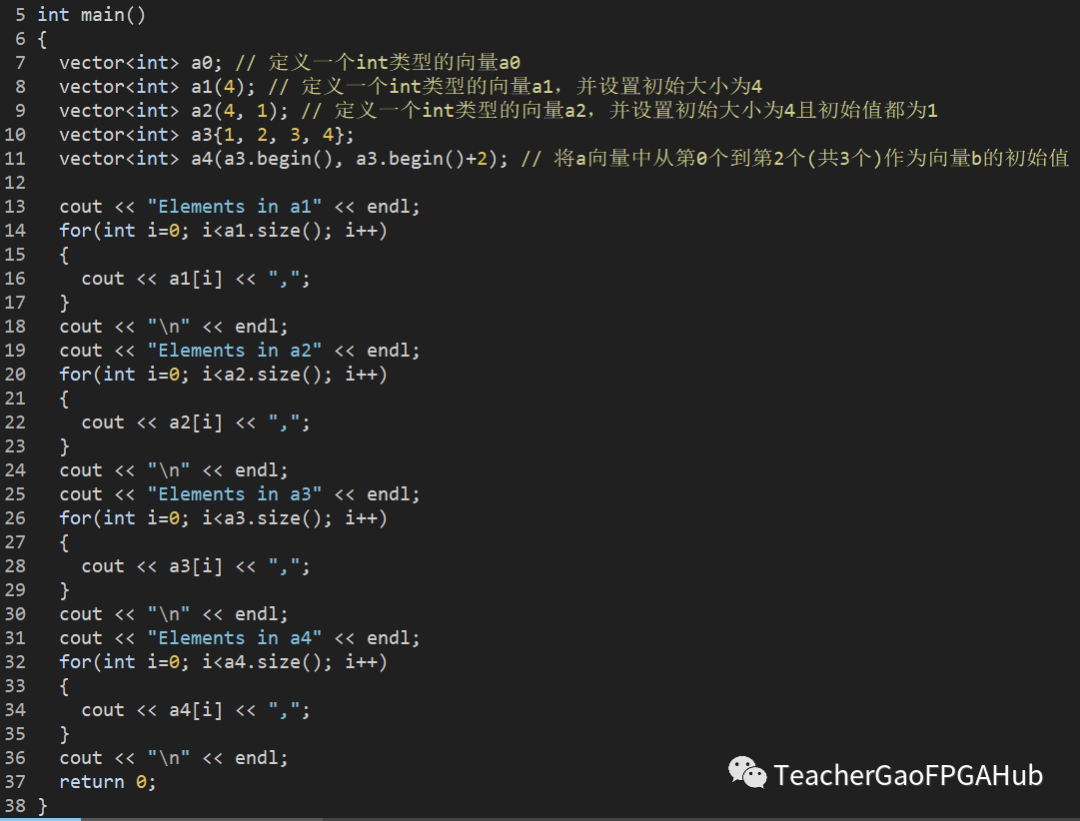

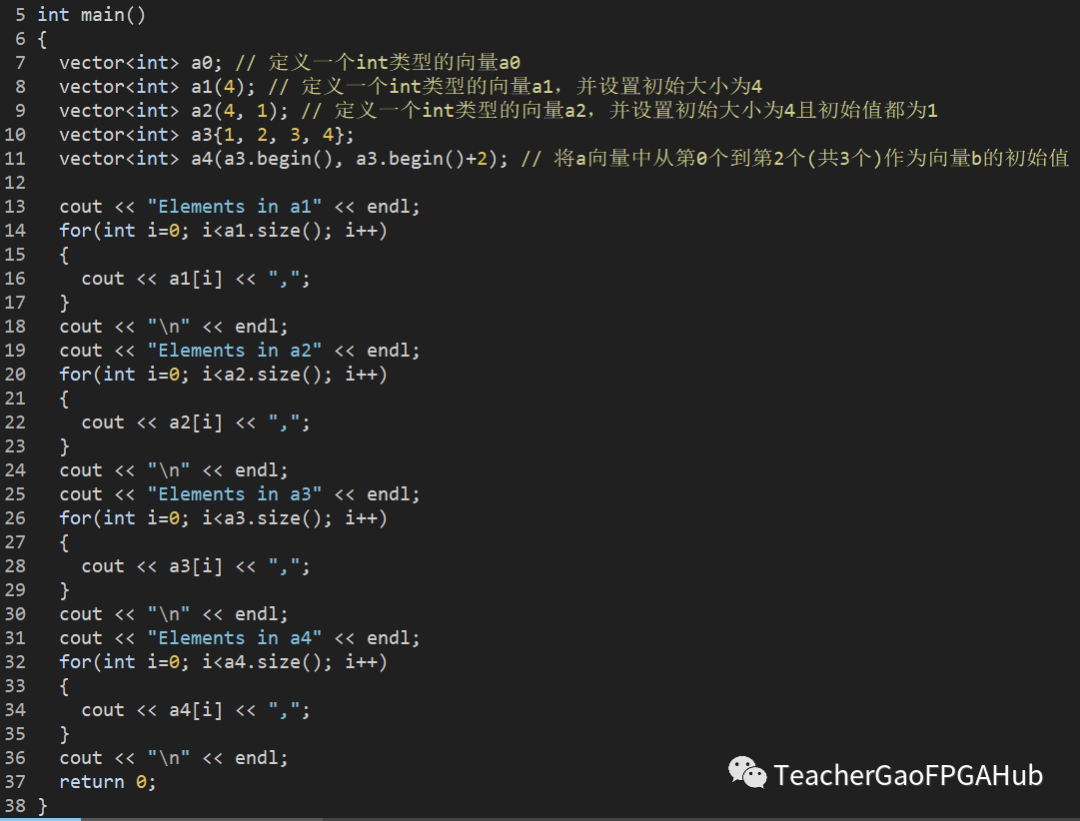

C++中的vector vector(向量)是一种序列式容器,类似于数组,但比数组更优越。一般来说数....

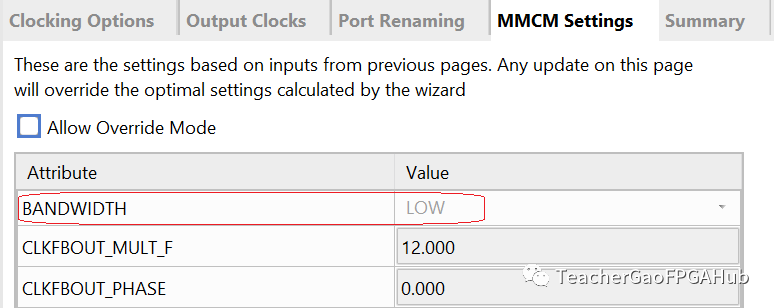

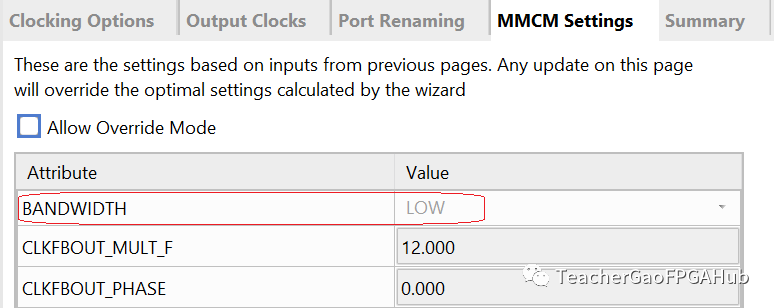

MMCM的一个重要功能就是过滤抖动,更准确地说是改善抖动。使用MMCM时,建议直接调用IP Core....

在ISE中,可以很方便地生成RTL模块的实例化模板,Vivado其实也有这个功能,只是要通过Tc....

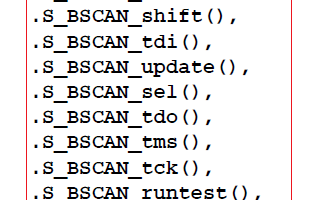

问题1:对于DFX(Dynamic FunctioneXchange)设计,如果出现如下Error信....

Vivado提出了UFDM(UltraFast Design Methodology)设计方法学,其....

设置芯片型号,设置源文件位置,设置生成文件位置,添加设计源文件,流程命令,生成网表文件,设计分析,生....

打开一个Block Design,就像打开一个空白画布一样,根据需要添加相应的IP:在“画布”的空白....

在这里有两个个重要的参数type和factor,其中type有三个可选值,分别为block、cycl....

在FPGA设计与开发中,Device视图和Package视图发挥着重要的作用。在Device视图下:....

Vivado HLS 2020.1将是Vivado HLS的最后一个版本,取而代之的是VitisHL....

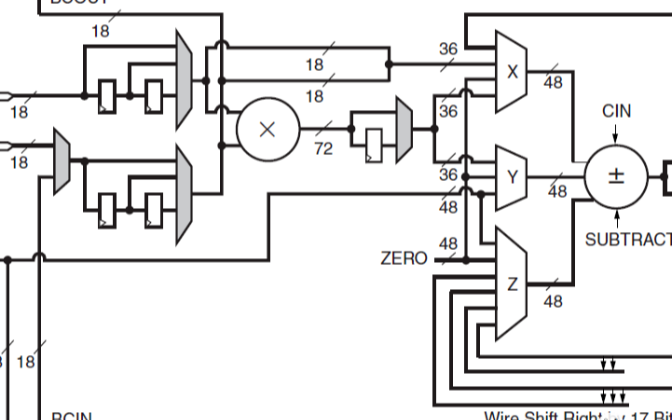

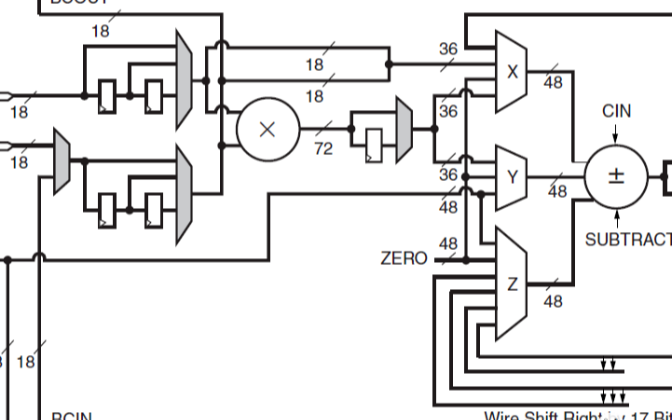

DSP48最早出现在XilinxVirtex-4 FPGA中,但就乘法器而言,Virtex-II和V....

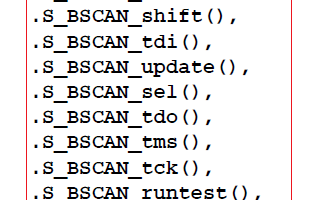

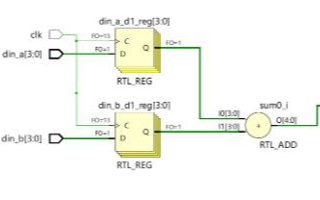

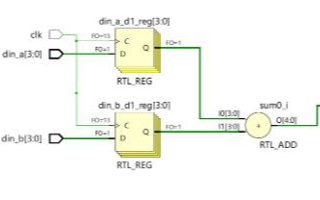

此电路对应的RTL代码如下图所示,这里我们使用了SystemVerilog来描述。输入a和b均为4个....

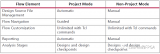

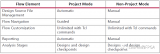

Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助Vi....

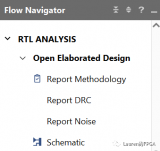

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属....

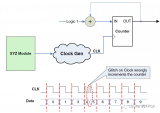

组合逻辑生成的时钟,在FPGA设计中应该避免,尤其是该时钟扇出很大或者时钟频率较高,即便是该时钟通过....

采用RTL代码描述位宽相同的两个数相加或相减,无论是有符号数还是无符号数,Vivado综合后的结果是....

采用HDL代码描述加法运算只需要用操作符+即可,这看似很简单,这里我们以两个4-bit数相加为例,对....

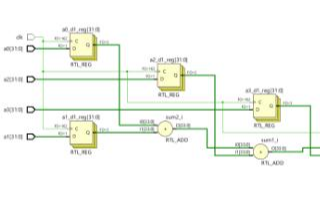

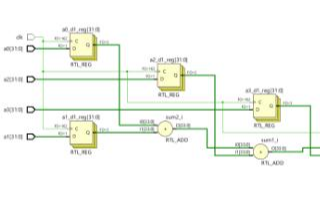

两个数相加,三个数相加有什么不同 接下来,我们考虑4个32-bit有符号数相加该如何实现,其中目标时....

同步时钟是指发送时钟和接收时钟是由同一个MMCM或PLL生成,两者之间有明确的相位关系。

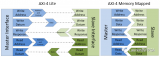

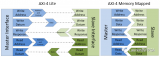

AXI全称Advanced eXtensibleInterface,是Xilinx从6系列的FPGA....

AXI-4 Memory Mapped也被称之为AXI-4 Full,它是AXI4接口协议的基础,其....

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,从下面的示例图中就可见一....

方法1:采用[set var]的方式,如下图所示。代码第6行中括号中的set命令只跟随一个参数$va....

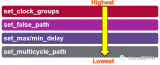

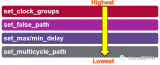

XDC描述的时序约束是有优先级的,尤其是涉及到时序例外的约束,如set_clock_groups、s....

更为具体的时序报告信息如何从中获取,或者如何根据时序报告发现导致时序违例的潜在原因呢?

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Desi....

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Desi....

关于Vivado Dashboard的功能可阅读这篇文章(Vivado 2018.3这个Gadget....