跨时钟域电路设计:单周期脉冲信号如何跨时钟域

参数REG_OUTPUT用于确定是否对最终输出信号寄存;参数RST_USED用于确定是否使用复位信号....

单位宽信号如何跨时钟域

单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可....

FPGA设计中的反馈路径可以怎么优化呢?

在FPGA设计中,我们可能会碰到这样的路径,如下图所示。图中两个输入数据为64位,寄存一拍后给到二选....

基于20nm工艺制程的FPGA—UltraScale介绍

UltraScale是基于20nm工艺制程的FPGA,而UltraScale+则是基于16nm工艺制....

基于28nm工艺制程的7系列FPGA

7系列FPGA是基于28nm工艺制程。在7系列FPGA中,每个输入/输出区域(I/O Bank)包含....

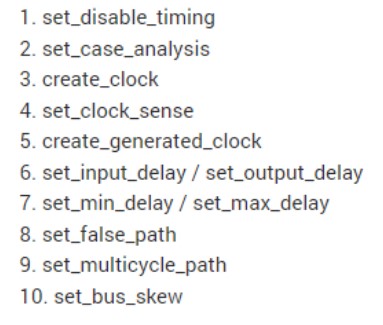

缩短Vivado编译时间之审视时序约束描述

在描述时序约束时,一个重要的原则是确保约束简洁高效。简洁高效意味着约束只针对指定的对象,即约束对应的....

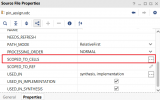

Vivado里如何手动调整编译顺序

通常情况下,一旦创建好Vivado工程,添加了相应的RTL文件,Vivado会自动找到设计的顶层文件....

关于Vivado Non-project,我们应知道的一些问题

Vivado支持Project模式也支持Non-Project模式。两者既可以支持图形界面也支持Tc....

理解Vitis HLS默认行为

相比于VivadoHLS,Vitis HLS更加智能化,这体现在Vitis HLS可以自动探测C/C....

Vivado里如何使用模糊性的位置约束?

提到位置约束,我们会想到手工布局的方式,即画Pblock,将指定模块放入相应Pblock内,这既是面....

如何理解HLS Block-level输入输出信号之间的时序关系

默认情况下,VitisHLS会对待综合的C函数使用ap_ctrl_hs接口,这其实是一种握手方式。在....

用HLS实现PID控制器

PID控制器(比例-积分-微分控制器),由比例单元(Proportional)、积分单元(Integ....

Xilinx推出了新一代功耗评估工具:PDM

PDM支持两种使用流程:手工流程和导入流程。手工流程要求工程师手动输入各种参数,如时钟频率、翻转率、....

AIE支持哪两种类型的RTP

AIE Kernel有时需要由外部提供参数更新kernel行为,此时就要用到RTP(Run-Time....

Vivado Synthesis模块化的设计方法

全局综合(Global Synthesis)全局综合意味着整个设计在一个Synthesis Desi....