本文用的芯片型号为xcku115-flvd1924-1L-i,时钟频率为400MHz。

两个有符号数相加

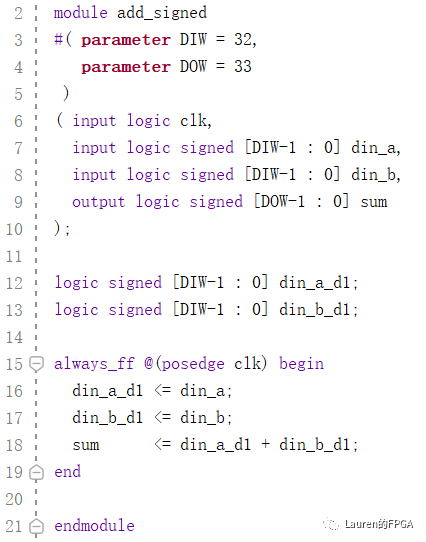

采用RTL代码描述位宽相同的两个数相加或相减,无论是有符号数还是无符号数,Vivado综合后的结果是一致的。以32bit数据为例,相应的代码如下图所示。这里考虑到两个32bit数据相加其结果可能为33bit,同时对于高速设计(时钟频率至少400MHz)为了满足性能,对输入和输出分别添加了流水寄存器。

最终的资源利用率如下图所示。

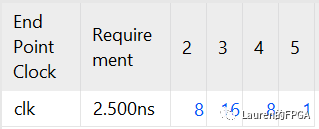

从逻辑级数的角度看,逻辑级数最大为5(有一条),大多数路径为3,如下图所示。

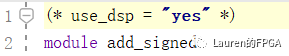

从综合属性角度看,可以通过use_dsp属性使得该加法操作映射到DSP48中,该属性的使用方法如下图所示。

采用DSP48实现时,上述代码可达到完全映射,不会消耗SLICE中的任何资源。假定时钟频率为400MHz,对比使用LUT+FF和DSP48两种实现方式,不难看出后者在时序(逻辑级数降低至1)和功耗方面均有优势。

-

寄存器

+关注

关注

31文章

5589浏览量

129074 -

RTL

+关注

关注

1文章

393浏览量

62400 -

代码

+关注

关注

30文章

4941浏览量

73151

原文标题:两个数相加,三个数相加有什么不同

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

e203乘除法模块(e203_exu_alu_muldiv.v)中的back2back和special case信号的含义

Verilog实现使用Booth编码和Wallace树的定点补码乘法器原理

关于E203内核高性能乘法器优化(一)

RISC-V V扩展的指令代码

RTL8723DS天线引脚焊接问题

0.6 至 3.0 GHz 双通道 SPST (2xSPST) 并联开关(两位控制),采用 WLCSP 封装 skyworksinc

如何使用 SPI 全双工在两个 5LP MPU 之间连接 RAM?

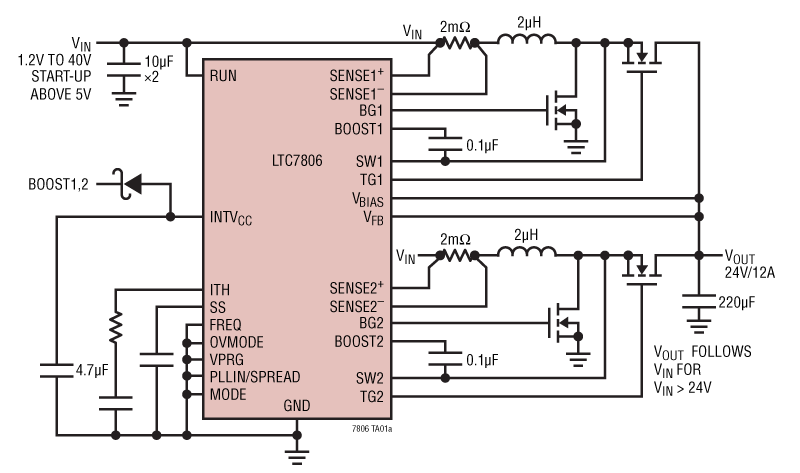

Analog Devices Inc. LTC7806两相同步升压控制器数据手册

变频器相同的故障原因不同的故障代码分类

采用RTL代码描述位宽相同的两个数相加或相减

采用RTL代码描述位宽相同的两个数相加或相减

评论