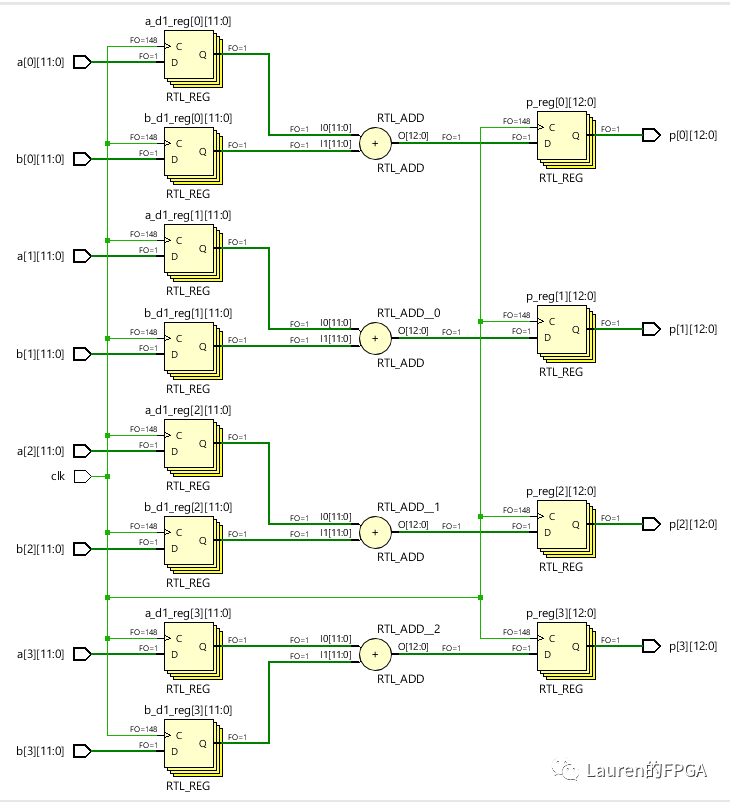

这里并行加法是指多个加法操作同时执行,这意味着需要消耗多个加法器。这里我们以4个12-bit数相加(加数和被加数均为12-bit,故和为13-bit,从而避免了溢出问题)。相应的电路图如下图所示。图中的RTL_ADD即为加法器,同时此电路对输入和输出数据均添加了流水寄存器。

此电路对应的RTL代码如下图所示,这里我们使用了SystemVerilog来描述。输入a和b均为4个12-bit数据构成的数组。输出p也是4个12-bit构成的数组。代码第17行至第23行是核心部分,包括了对输入、输出添加流水寄存器和加法操作。

责任编辑:lq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电路图

+关注

关注

10460文章

10749浏览量

552022 -

加法器

+关注

关注

6文章

183浏览量

31250 -

数组

+关注

关注

1文章

420浏览量

27119

原文标题:并行加法的高效实现

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

串行通讯与并行通讯介绍

按数据传送的方式,通讯可分为串行通讯与并行通讯,串行通讯是指设备之间通过少量数据信号线(一般是8根以下), 地线以及控制信号线,按数据位形式一位一位地传输数据的通讯方式。而并行通讯一般是指使用8

发表于 12-11 06:52

一文看懂AI大模型的并行训练方式(DP、PP、TP、EP)

大家都知道,AI计算(尤其是模型训练和推理),主要以并行计算为主。AI计算中涉及到的很多具体算法(例如矩阵相乘、卷积、循环层、梯度运算等),都需要基于成千上万的GPU,以并行任务的方式去完成。这样

复杂的软件算法硬件IP核的实现

中的运算符有对应关系。

结构域负责将功能域中的各个基本功能单元按特定的顺序和方式连接起来,通常被实现为一个由有限状态机控制的数据通路,该结构与C 语言的流程控制语句相对应。

以一个简单的加法组合逻辑为例

发表于 10-30 07:02

EA-BIM 20005:20通道并行EIS测量,让电池阻抗分析更精准高效

、超快速EIS技术和高精度性能,重新定义电池阻抗检测标准,助力企业实现质量控制与生产效率的双重突破。PART01核心优势,破解EIS测量痛点20通道并行,高吞吐量

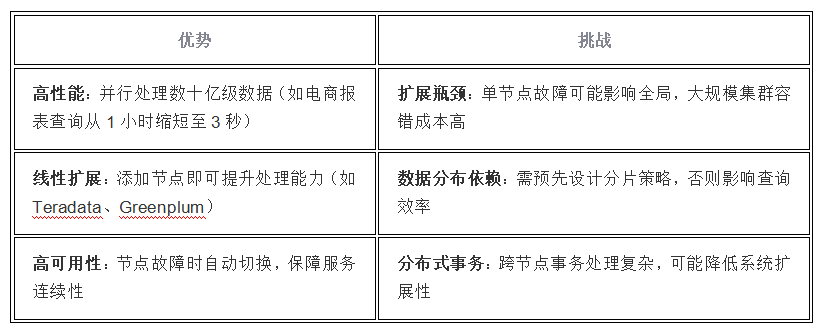

多节点并行处理架构

多节点并行处理架构(如MPP架构)通过分布式计算和存储实现高性能数据处理,其核心设计及典型应用如下: 一、核心架构特征 非共享架构(Share Nothing) 每个节点拥有独立的计算资源(CPU

如何利用RAKsmart服务器实现高效多站点部署方案

利用RAKsmart服务器实现高效多站点部署方案,需结合其网络优势、弹性资源管理和合理的架构设计。以下是分步实施方案,涵盖网络优化、资源分配、数据管理及监控等核心环节,主机推荐小编为您整理发布如何利用RAKsmart服务器实现

读懂极易并行计算:定义、挑战与解决方案

GPU经常与人工智能同时提及,其中一个重要原因在于AI与3D图形处理本质上属于同一类问题——它们都适用极易并行计算。什么是极易并行计算?极易并行计算指的是符合以下特征的计算任务:任务独立性:子任务

如何使用FPGA驱动并行ADC和DAC芯片,使用不同编码方式的ADC与DAC时的注意事项

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和

高效音频编码器设计与实现:重塑声音世界的科技力量

在数字化时代,音频作为信息传播的重要载体,其质量和传输效率成为了衡量技术先进性的关键指标。高效音频编码器的出现,不仅极大地优化了音频数据的压缩率,还在保证音质的前提下,实现了数据的快速传输与存储,为

xgboost的并行计算原理

在大数据时代,机器学习算法需要处理的数据量日益增长。为了提高数据处理的效率,许多算法都开始支持并行计算。XGBoost作为一种高效的梯度提升树算法,其并行计算能力是其受欢迎的原因

并行加法的高效实现

并行加法的高效实现

评论