Vivado HLS 2020.1将是Vivado HLS的最后一个版本,取而代之的是VitisHLS。那么两者之间有什么区别呢?

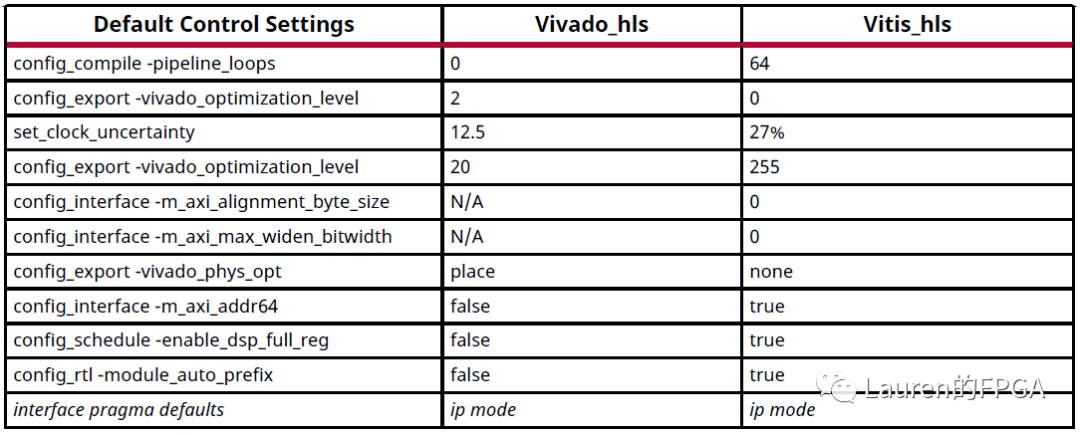

Default User Control Settings

在Vitis HLS下,一个Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下图所示。前者最终导出来的是VivadoIP,用于支持Vivado IP 设计流程。后者用于Vitis应用加速流程,此时,Vitis HLS会自动推断接口,无需在代码里通过Pragma或Directive的方式定义Interface,最终会输出.xo文件。

User Control Settings还有其他的一些变化,如下表所示。例如,在Vivado HLS下,默认是不会对循环设置Pipeline的,但在Vitis HLS下,只要循环边界小于64,就会对循环设置Pipeline。在Vivado HLS下,默认Clock Uncertainty是时钟周期的12.5%,但在Vitis HLS下更严格,达到了27%。

对循环而言,在Vivado HLS下,II(Initial Interval)默认的约束值为1,但在Vitis HLS下,II默认值为auto,意味着工具会尽可能达到最好的II。 目前,针对Vitis HLS,Xilinx已经提供了如下文档和设计案例: UG1391:Vitis HLSMigration Guide UG1399:VitisHigh-Level Synthesis User Guide Vitis HLS examples: https://github.com/Xilinx/HLS-Tiny-Tutorials

责任编辑:xj

原文标题:Vivado HLS和Vitis HLS什么区别?

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

-

代码

+关注

关注

30文章

4977浏览量

74420 -

Vivado

+关注

关注

19文章

860浏览量

71430 -

HLS

+关注

关注

1文章

135浏览量

25995

原文标题:Vivado HLS和Vitis HLS什么区别?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

保险丝与熔断器有什么区别

HLS设计中的BRAM使用优势

蜂鸟处理器+OV5640摄像头模块开发

SD-WAN和专线的区别是什么?两者详细对比介绍!

如何在vivadoHLS中使用.TLite模型

CBB82电容和CBB81电容有什么区别

TVS ESD,都是保护二极管,有什么区别?如何选型?

使用AMD Vitis Unified IDE创建HLS组件

如何使用AMD Vitis HLS创建HLS IP

Vivado HLS和Vitis HLS 两者之间有什么区别

Vivado HLS和Vitis HLS 两者之间有什么区别

评论