电子发烧友网综合报道

当谷歌凭借TPU芯片与Gemini 3模型加冕AI新王,算力领域的技术迭代正引发连锁反应。作为高效能运算的核心配套,先进封装技术市场正经历前所未有的变革,英特尔推出的EMIB技术悄然崛起,向长期占据主导地位的台积电CoWoS方案发起挑战,一场关乎AI产业成本与效率的技术博弈已然拉开序幕。

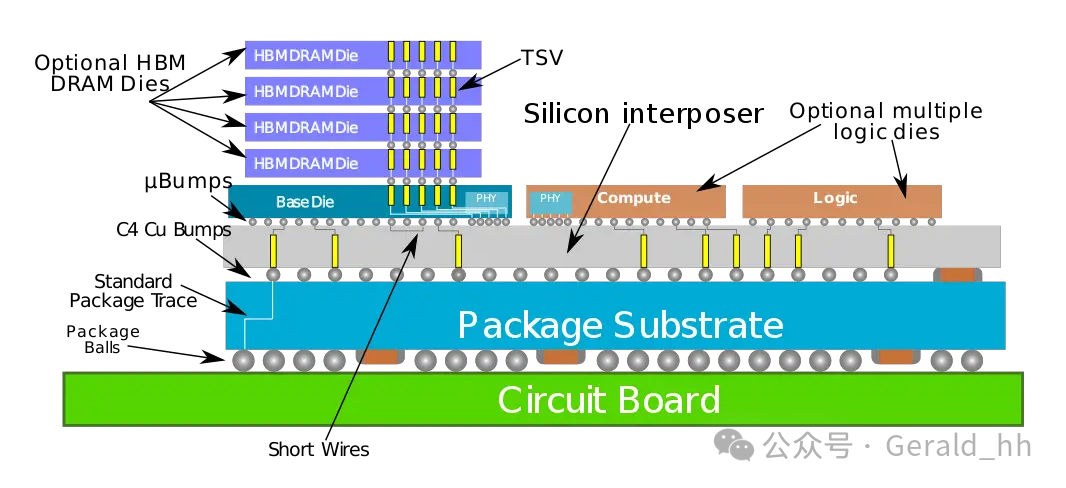

在AI算力需求呈指数级增长的当下,先进封装技术成为突破芯片性能瓶颈的关键。台积电的CoWoS技术历经十余年迭代,凭借成熟的工艺和出色的传输性能,长期垄断高端市场。

英伟达、AMD等GPU巨头对带宽、传输速度及低延迟的极致追求,使其成为CoWoS方案的核心拥趸,英伟达一家便占据了CoWoS超过60%的产能。英伟达CEO黄仁勋曾明确表示,CoWoS是当前最先进的封装技术,公司目前没有替代选择,这一表态也印证了CoWoS在高性能计算领域的核心地位。

然而,AI产业的爆发式增长让CoWoS的短板日益凸显,产能短缺成为制约行业发展的关键瓶颈。今年10月台积电坦言,AI应用仍处于早期阶段,相关产能极度紧张,虽计划在2026年提升CoWoS产能,但短期内供需矛盾难以缓解。

与此同时,CoWoS内部大中介层带来的高昂成本,以及光罩尺寸的限制,让不少中小型客户望而却步,为市场变革埋下了伏笔。

就在CoWoS面临发展困境之际,英特尔的EMIB技术凭借精准的定位迅速获得市场关注。作为一种2.5D先进封装技术,EMIB最大的优势在于面积灵活性与成本控制。与CoWoS-S仅3.3倍、CoWoS-L当前3.5倍的光罩尺寸相比,EMIB-M已能提供6倍光罩尺寸,预计2026至2027年可进一步拓展至8倍至12倍,远超CoWoS的发展上限。

在成本方面,EMIB舍弃了价格高昂的中介层,采用将芯片内嵌在载板硅桥的方式实现互连,简化了整体结构,为对成本敏感的AI客户提供了更具性价比的选择。这一技术特性恰好契合了以谷歌为代表的ASIC方案崛起的市场趋势,有机构指出,谷歌已构建起成熟的训推一体ASIC体系,其Gemini 3模型依托TPU集群完成训练,下一代Ironwood(TPU v7)芯片更展现了大规模低功耗推理的工程化优势。

受此带动,谷歌计划在2027年的TPU v9中导入EMIB试用,Meta也在积极评估将其应用于MTIA产品,市场对ASIC芯片的关注度持续升温。

ASIC方案的爆发预期成为EMIB技术普及的核心推力。Wedbush Securities的Dan Ives观察到,市场正在重新发现ASIC芯片的巨大潜力,多家机构研判,2026至2027年,谷歌、亚马逊、Meta、Open AI及微软的ASIC 芯片数量将迎来爆发式增长。

云端服务业者加速自研ASIC的过程中,对整合复杂功能的芯片封装面积需求不断扩大,台积电CoWoS的产能限制与成本压力,让英特尔EMIB成为理想替代方案。除了谷歌、Meta,苹果在DRAM封装工程师招聘中明确要求具备EMIB技术经验,高通为数据中心业务招聘的产品管理总监职位也将EMIB技术列为必备技能,美满电子、联发科等厂商更是考虑为ASIC项目导入EMIB封装,一场由头部企业引领的技术迁移正在悄然发生。

不过,EMIB想要完全撼动CoWoS的地位仍面临挑战。Trendforce指出,EMIB技术受限于硅桥面积与布线密度,在互连带宽、讯号传输距离和延迟性方面存在短板,目前仅能满足ASIC客户的需求。对于英伟达、AMD等对性能要求极致的GPU供应商而言,CoWoS仍是不可替代的选择。这意味着未来先进封装市场或将呈现双雄并立的格局,CoWoS继续主导高性能GPU领域,而EMIB则在ASIC市场快速扩张,两者根据不同应用场景形成互补。

当谷歌凭借TPU芯片与Gemini 3模型加冕AI新王,算力领域的技术迭代正引发连锁反应。作为高效能运算的核心配套,先进封装技术市场正经历前所未有的变革,英特尔推出的EMIB技术悄然崛起,向长期占据主导地位的台积电CoWoS方案发起挑战,一场关乎AI产业成本与效率的技术博弈已然拉开序幕。

在AI算力需求呈指数级增长的当下,先进封装技术成为突破芯片性能瓶颈的关键。台积电的CoWoS技术历经十余年迭代,凭借成熟的工艺和出色的传输性能,长期垄断高端市场。

英伟达、AMD等GPU巨头对带宽、传输速度及低延迟的极致追求,使其成为CoWoS方案的核心拥趸,英伟达一家便占据了CoWoS超过60%的产能。英伟达CEO黄仁勋曾明确表示,CoWoS是当前最先进的封装技术,公司目前没有替代选择,这一表态也印证了CoWoS在高性能计算领域的核心地位。

然而,AI产业的爆发式增长让CoWoS的短板日益凸显,产能短缺成为制约行业发展的关键瓶颈。今年10月台积电坦言,AI应用仍处于早期阶段,相关产能极度紧张,虽计划在2026年提升CoWoS产能,但短期内供需矛盾难以缓解。

与此同时,CoWoS内部大中介层带来的高昂成本,以及光罩尺寸的限制,让不少中小型客户望而却步,为市场变革埋下了伏笔。

就在CoWoS面临发展困境之际,英特尔的EMIB技术凭借精准的定位迅速获得市场关注。作为一种2.5D先进封装技术,EMIB最大的优势在于面积灵活性与成本控制。与CoWoS-S仅3.3倍、CoWoS-L当前3.5倍的光罩尺寸相比,EMIB-M已能提供6倍光罩尺寸,预计2026至2027年可进一步拓展至8倍至12倍,远超CoWoS的发展上限。

在成本方面,EMIB舍弃了价格高昂的中介层,采用将芯片内嵌在载板硅桥的方式实现互连,简化了整体结构,为对成本敏感的AI客户提供了更具性价比的选择。这一技术特性恰好契合了以谷歌为代表的ASIC方案崛起的市场趋势,有机构指出,谷歌已构建起成熟的训推一体ASIC体系,其Gemini 3模型依托TPU集群完成训练,下一代Ironwood(TPU v7)芯片更展现了大规模低功耗推理的工程化优势。

受此带动,谷歌计划在2027年的TPU v9中导入EMIB试用,Meta也在积极评估将其应用于MTIA产品,市场对ASIC芯片的关注度持续升温。

ASIC方案的爆发预期成为EMIB技术普及的核心推力。Wedbush Securities的Dan Ives观察到,市场正在重新发现ASIC芯片的巨大潜力,多家机构研判,2026至2027年,谷歌、亚马逊、Meta、Open AI及微软的ASIC 芯片数量将迎来爆发式增长。

云端服务业者加速自研ASIC的过程中,对整合复杂功能的芯片封装面积需求不断扩大,台积电CoWoS的产能限制与成本压力,让英特尔EMIB成为理想替代方案。除了谷歌、Meta,苹果在DRAM封装工程师招聘中明确要求具备EMIB技术经验,高通为数据中心业务招聘的产品管理总监职位也将EMIB技术列为必备技能,美满电子、联发科等厂商更是考虑为ASIC项目导入EMIB封装,一场由头部企业引领的技术迁移正在悄然发生。

不过,EMIB想要完全撼动CoWoS的地位仍面临挑战。Trendforce指出,EMIB技术受限于硅桥面积与布线密度,在互连带宽、讯号传输距离和延迟性方面存在短板,目前仅能满足ASIC客户的需求。对于英伟达、AMD等对性能要求极致的GPU供应商而言,CoWoS仍是不可替代的选择。这意味着未来先进封装市场或将呈现双雄并立的格局,CoWoS继续主导高性能GPU领域,而EMIB则在ASIC市场快速扩张,两者根据不同应用场景形成互补。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CoWoS

+关注

关注

0文章

166浏览量

11465 -

EMIB

+关注

关注

0文章

15浏览量

4021 -

先进封装

+关注

关注

2文章

522浏览量

983

发布评论请先 登录

相关推荐

热点推荐

五家大厂盯上,英特尔EMIB成了?

电子发烧友网综合报道 最近,英特尔EMIB封装火了,在苹果、高通、博通的招聘信息中,都指出正在招募熟悉EMIB封装的工程师。近期还有消息称,由于台积电

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

台积电在先进封装技术,特别是CoWoS(Chip on Wafer on Substrate)平台上的微通道芯片液冷技术路线,是其应对高性能计算和AI芯片高热流密度挑战的关键策略。本报告将基于台积电相关的研究成果和已发表文献,深

HBM技术在CowoS封装中的应用

HBM通过使用3D堆叠技术,将多个DRAM(动态随机存取存储器)芯片堆叠在一起,并通过硅通孔(TSV,Through-Silicon Via)进行连接,从而实现高带宽和低功耗的特点。HBM的应用中,CowoS(Chip on Wafer on Substrate)封装技术

CoWoP能否挑战CoWoS的霸主地位

在半导体行业追逐更高算力、更低成本的赛道上,先进封装技术成了关键突破口。过去几年,台积电的CoWoS(Chip-on-Wafer-on-Substrate)技术凭借对AI芯片需求的精准适配,成了

从InFO-MS到InFO_SoW的先进封装技术

在先进封装技术向超大型、晶圆级系统集成深化演进的过程中,InFO 系列(InFO-MS、InFO-3DMS)与 CoWoS-L、InFO_SoW 等技术持续突破创新。

120×180mm怪兽封装!EMIB-T让AI芯片起飞

EMIB技术基础上引入硅通孔(TSV)的重大升级,旨在解决高性能计算、AI加速器和数据中心芯片的异构集成挑战。其核心是通过垂直互连提升封装密度和性能,同时降低功耗和延迟。 传统EMIB利用嵌入在

英特尔先进封装,新突破

了英特尔在技术研发上的深厚底蕴,也为其在先进封装市场赢得了新的竞争优势。 英特尔此次的重大突破之一是 EMIB-T 技术。EMIB-T 全称

日月光扩大CoWoS先进封装产能

近期,半导体封装巨头日月光投控在先进封装领域再次迈出重要一步,宣布将扩大其CoWoS(Chip-on-Wafer-on-Substrate)先进

先进封装行业:CoWoS五问五答

前言 一、CoWoS 技术概述 定义与结构:CoWoS(Chip on Wafer on Substrate)是一种 2.5D 先进封装技术,由 Chip on Wafer(CoW)和

台积电先进封装大扩产,CoWoS制程成扩充主力

近日,台积电宣布了其先进封装技术的扩产计划,其中CoWoS(Chip-on-Wafer-on-Substrate)制程将成为此次扩产的主力军。随着对群创旧厂的收购以及相关设备的进驻,以及台中厂产能

先进封装市场迎来EMIB与CoWoS的格局之争

先进封装市场迎来EMIB与CoWoS的格局之争

评论