文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了从InFO-MS到InFO_SoW的先进封装技术。

在先进封装技术向超大型、晶圆级系统集成深化演进的过程中,InFO 系列(InFO-MS、InFO-3DMS)与 CoWoS-L、InFO_SoW 等技术持续突破创新。

这些技术通过工艺融合与架构重构,在高带宽存储器集成、三维异构堆叠、晶圆级系统构建等方面实现突破,既优化了成本与性能平衡,又满足了 HPC、AI 加速器等场景对高带宽、高密度互连的需求,推动封装技术向更广阔的系统级扩展维度迈进,本文分述如下:

板载存储芯片的InFO技术(InFO-MS)

3D多硅InFO(InFO-3DMS)和CoWoS-L

晶圆上 InFO系统(InFO_SoW)

板载存储芯片的InFO技术(InFO-MS)

在高性能计算(HPC)系统向超异构集成演进的背景下,台积电的InFO-MS(板载存储器扇出型封装)技术通过工艺创新与架构重构,为高带宽存储器(HBM)与逻辑芯片的集成提供了全新解决方案。作为InFO平台的延伸,该技术将HBM芯片直接嵌入扇出型塑封料中,再通过高密度重布线层(RDL)实现与SoC的垂直互连,其核心突破在于通过改进的RDL线宽/间距(低至2μm/2μm)与嵌入式LSI(局部硅互连)芯片,在保持成本竞争力的同时,实现了媲美CoWoS-R的电气性能与带宽密度。

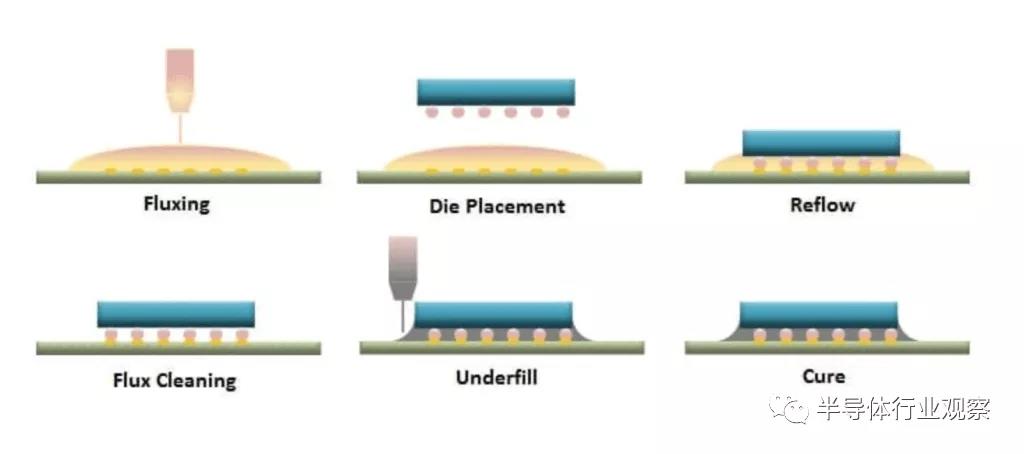

从技术实现路径看,InFO-MS采用"芯片预嵌入+RDL成型"的工艺流程:HBM与SoC芯片首先在晶圆级基板上完成精准定位,随后通过光刻工艺构建多层铜重布线层,线宽/线距可压缩至2μm/2μm级别。这种设计使单块封装即可集成多颗异质芯片(如逻辑、存储模块),并通过扇出型走线实现芯片间横向互连。值得关注的是,该技术通过模块化预堆叠工艺,使存储单元可独立测试后嵌入系统,显著提升了生产良率与设计灵活性。

针对第三方HBM的兼容性挑战,InFO-MS通过自适应工艺调整与严格公差控制,解决了不同厂商存储芯片在封装过程中的对齐难题。

从成本与布局灵活性看,InFO-MS通过复用现有InFO产线设备,将高端封装的准入门槛降低了30%以上。与CoWoS-R相比,该技术无需依赖硅转接板,转而采用有机基板与扇出工艺的结合,在保持超薄封装外形(0.5mm量级)的同时,实现了光罩尺寸的突破——当前量产产品已覆盖1.7倍光罩,而大于2.5倍光罩的下一代技术正在研发中。这种"全局宽松+局部精密"的互连设计,为构建超大型HPC系统(如数据中心交换机)提供了可行性路径,满足6.4Tbit/s至25.6Tbit/s级数据交换容量对带宽与延迟的严苛要求。

随着玻璃基板替代有机基材的研究推进,InFO-MS有望在2026年实现光罩尺寸突破3倍,进一步缩小与单片SoC的性能差距。这种技术演进不仅满足了AI算力芯片、5G基站射频模块等高带宽需求应用的需求,更通过模块化设计与工艺解耦,为设计公司开辟了更灵活的制造资源调配路径,重新定义了HPC系统集成的成本与性能平衡点。

3D多硅InFO(InFO-3DMS)和CoWoS-L

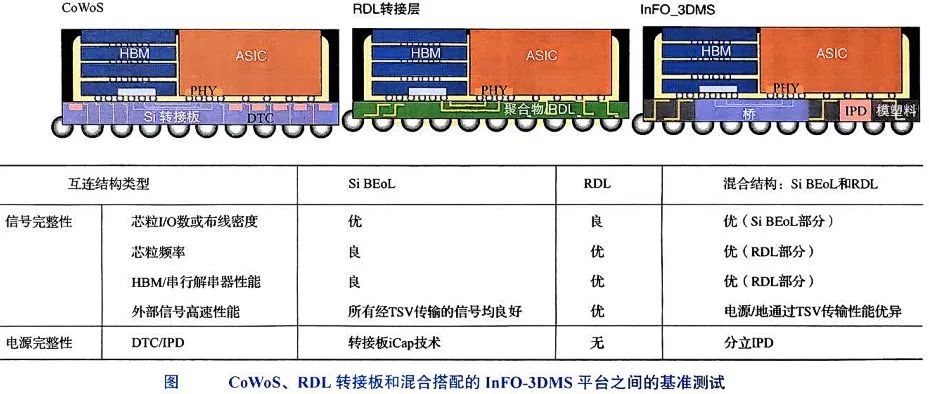

在先进封装技术向三维异构集成深度演进的背景下,InFO-3DMS(3D多硅扇出型封装)与CoWoS-L技术通过工艺融合与架构创新,重新定义了超大型系统集成的性能与成本平衡点。

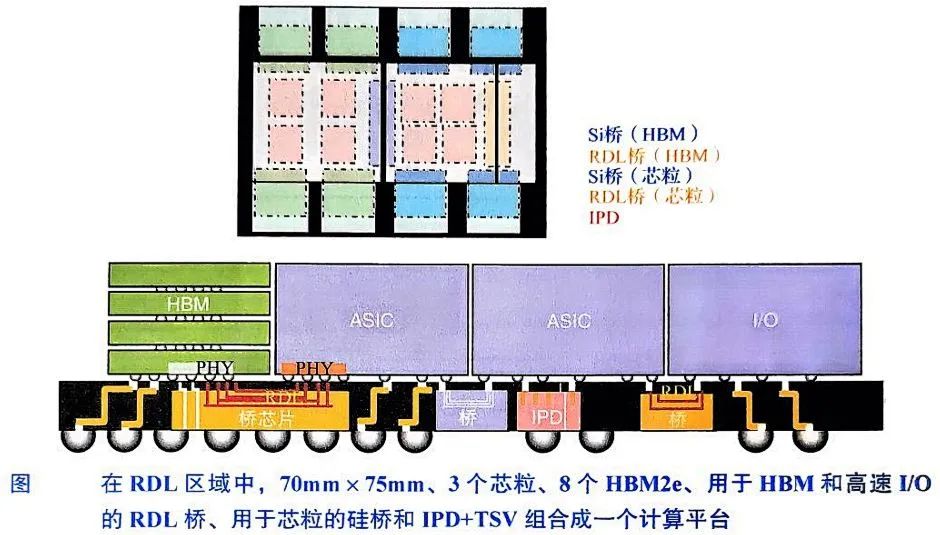

作为该领域的标志性创新,InFO-3DMS将扇出型重布线层(RDL)与多类型硅芯片(包括有源逻辑、无源器件及局部硅桥)的垂直堆叠相结合,既保留了InFO工艺的高密度互连优势(线宽/间距低至2μm/2μm),又通过硅桥接片的嵌入式设计实现了局部亚微米级互连(如0.8μm节距)。这种"全局扇出+局部精密"的架构,使单块封装即可集成逻辑、存储、射频模块及无源器件,并通过分层测试流程(先验证芯粒功能,再组装至InFO基板)将良率损失控制在行业领先水平。

CoWoS-L作为CoWoS平台的延伸,通过局部硅互连(LSI)芯片与RDL层的协同设计,解决了传统硅转接板在成本与灵活性上的瓶颈。其核心突破在于将微型硅桥接片嵌入RDL层中,在特定区域实现超高密度互连(如0.5μm节距),同时保留有机基板的大面积布局优势。当与InFO-3DMS结合时,系统架构师得以在超大型封装内实现"全局宽松+局部精密"的互连设计——例如在AI加速器中,通过CoWoS-L完成HBM与计算核心的高速互连,再利用InFO-3DMS将射频模块与基带芯片集成至同一封装,从而在保持系统成本竞争力的同时,满足6.4Tbit/s至25.6Tbit/s级数据交换容量对带宽与延迟的严苛要求。

从市场定位看,上图定性比较揭示了InFO-3DMS与CoWoS-L的技术差异:前者通过扇出工艺与硅桥接片的结合,在移动终端与边缘计算场景中提供超薄封装(0.5mm量级)与低成本优势;后者则依托硅转接板的高热导率特性,在HPC领域实现更高的带宽密度(如HBM集成)。这种差异化布局使两者在AI算力芯片、数据中心交换机等场景中形成互补,共同推动摩尔定律在系统级封装(SiP)领域的延续。

晶圆上InFO系统(InFO_SoW)

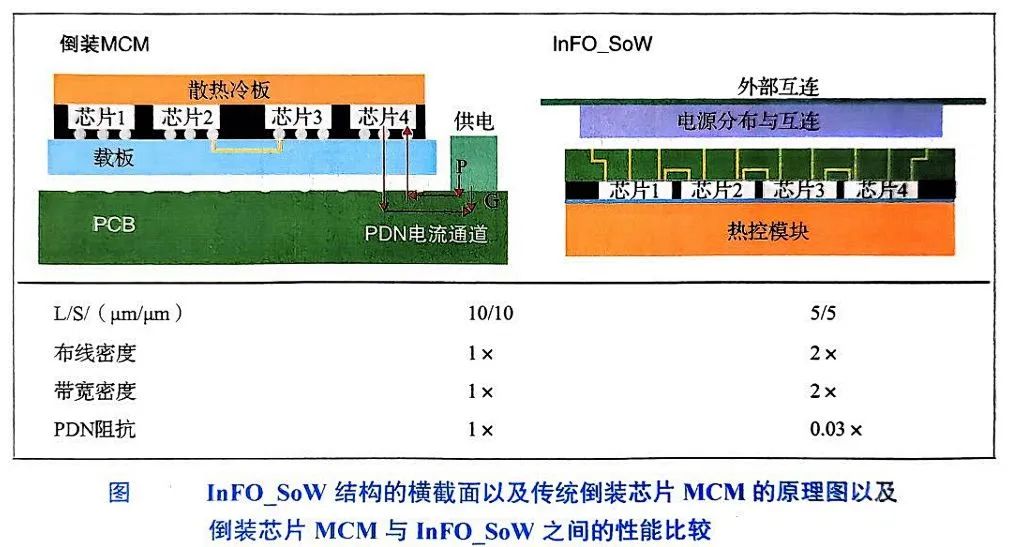

在超大型系统集成向晶圆级架构演进的浪潮中,InFO_SoW(晶圆上InFO系统)技术通过全晶圆级工艺与三维异构集成,重新定义了高性能计算(HPC)与AI加速器的封装边界。

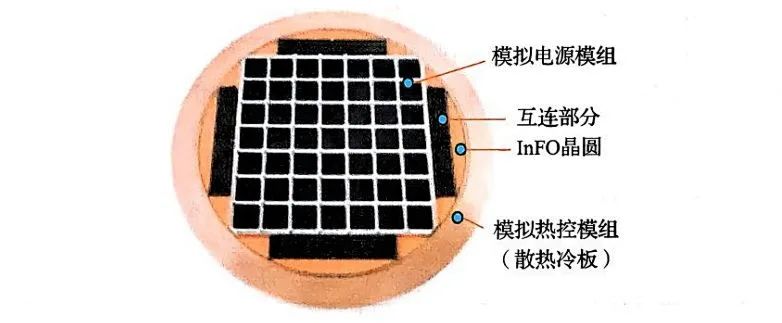

作为业界首款晶圆级系统集成方案,该技术将整个300mm晶圆转化为单一封装基板,通过超低表面粗糙度的RDL(重布线层)实现芯片间高密度互连——线宽/间距低至5μm/5μm,单层RDL即可构建两倍于传统基板的布线密度,使30mm级互连的功耗降低15%,信号完整性在28GHz频段下仍保持优异(30mm线路损耗仅0.7dB)。这种架构突破不仅消除了传统封装中基板与PCB的物理限制,更通过电源分配网络(PDN)阻抗降低97%,为超万兆级数据传输提供了零损耗的电力供应通道。

散热管理方面,InFO_SoW采用微通道液冷方案,通过2×5阵列加热器测试结构验证了其热稳定性:在7000W功率密度(1.2W/mm²)与16℃冷却水温条件下,虚拟加热器最高温度控制在90℃以下,较传统倒装芯片MCM方案降低30%热阻。值得关注的是,该技术通过晶圆级CPI(芯片-封装-相互作用)研究证明,其热机械风险显著低于先进制程的倒装芯片封装,为超大型系统在数据中心机架中的密集部署提供了可靠性保障。

-

晶圆

+关注

关注

53文章

5450浏览量

132765 -

存储芯片

+关注

关注

11文章

1058浏览量

44870 -

info

+关注

关注

0文章

12浏览量

10427 -

先进封装

+关注

关注

2文章

563浏览量

1062

原文标题:从InFO-MS到InFO_SoW,解锁超大型系统集成新可能

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何基于3DICC实现InFO布局布线设计

台积电InFO明年初通吃4厂有难度?外资提出 3 疑点

台积电或将生产Cerebras的“超级”AI芯片

探究IOBUS_INFO[]读取是否会出现总线故障

![探究IOBUS_<b class='flag-5'>INFO</b>[]读取是否会出现总线故障](https://file.elecfans.com/web1/M00/EE/6A/pIYBAGCWBbyAX-AwAAAYSRZEjrw906.png)

巨头们先进封装技术的详细解读

KUKA系统变量:$PROG_INFO

行业资讯 I 面向 TSMC InFO 技术的高级自动布线功能

采用InFO封装的新型UltraScale+器件支持紧凑型工业相机

台积电2023年报:先进制程与先进封装业务成绩

谷歌Tensor G5芯片转投台积电3nm与InFO封装

详解超高密度互连的InFO封装技术

从InFO-MS到InFO_SoW的先进封装技术

从InFO-MS到InFO_SoW的先进封装技术

评论