随着高性能计算(HPC)、人工智能(AI)和大数据分析的快速发展,诸如CoWoS(芯片-晶圆-基板)等先进封装技术对于提升计算性能和效率的重要性日益凸显。

CoWoS技术的基本原理

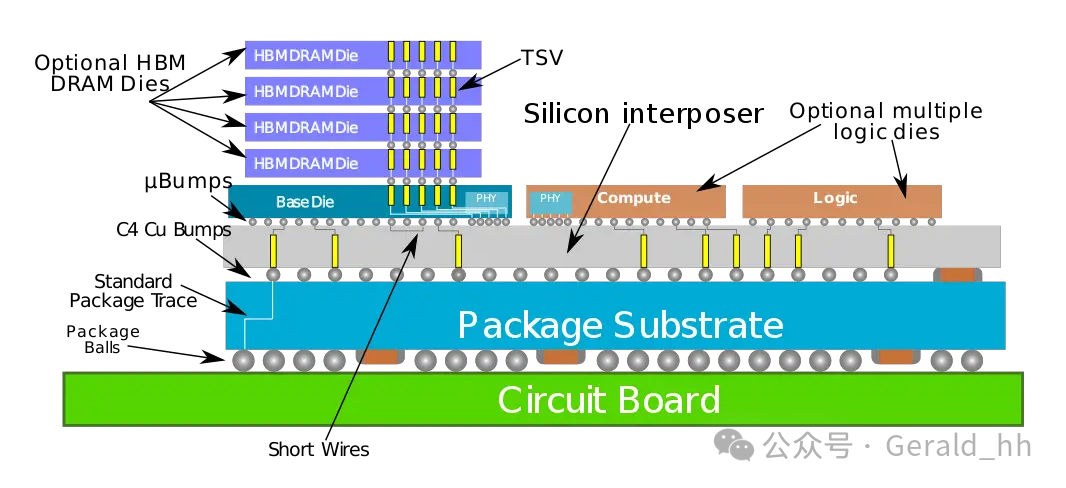

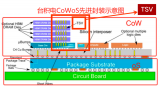

台积电推出的CoWoS技术是一种先进的封装技术,它将多个处理器芯片(例如SoC)直接封装在硅中介层上。这些芯片通过中介层上的硅通孔(TSV)垂直连接,形成高度集成的系统封装。然后,将该硅中介层集成到基板(例如PCB)上。这种方法显著缩短了芯片之间的连接距离,提高了数据传输速度,降低了延迟,并提升了系统的整体性能。

CoWoS技术的关键在于其高度集成的封装方式。通过将多个芯片集成在单个封装中,CoWoS能够提供更高的数据传输速率和更低的功耗,使其特别适用于高性能、高效率的计算应用,例如高性能计算(HPC)和人工智能(AI)。

CoWoS-S、CoWoS-R 和 CoWoS-L 技术简介

CoWoS架构融合了2.5D水平堆叠和3D垂直堆叠两种配置,彻底革新了传统的芯片封装模式。这种创新方法允许将各种处理器和内存模块逐层堆叠,形成互连的芯片组,最终构成一个完整的系统。与传统的2D封装方法相比,CoWoS利用硅通孔(TSV)和微凸点,实现了更短的互连长度、更低的功耗和更高的信号完整性。

从实际应用角度来看,CoWoS 技术能够将 GPU 和 AI 加速器等先进处理单元与高带宽内存 (HBM) 模块无缝集成。这种集成对于 AI 应用尤为重要,因为 AI 应用对强大的计算能力和快速的数据访问速度有着极高的要求。通过将处理单元和内存单元紧密地放置在一起,CoWoS 最大限度地降低了延迟,提高了吞吐量,从而为内存密集型任务带来了前所未有的性能提升。

台积电的CoWoS技术平台包括CoWoS-S、CoWoS-R和CoWoS-L,分别针对不同的高性能计算需求进行了优化。

CoWoS-S:

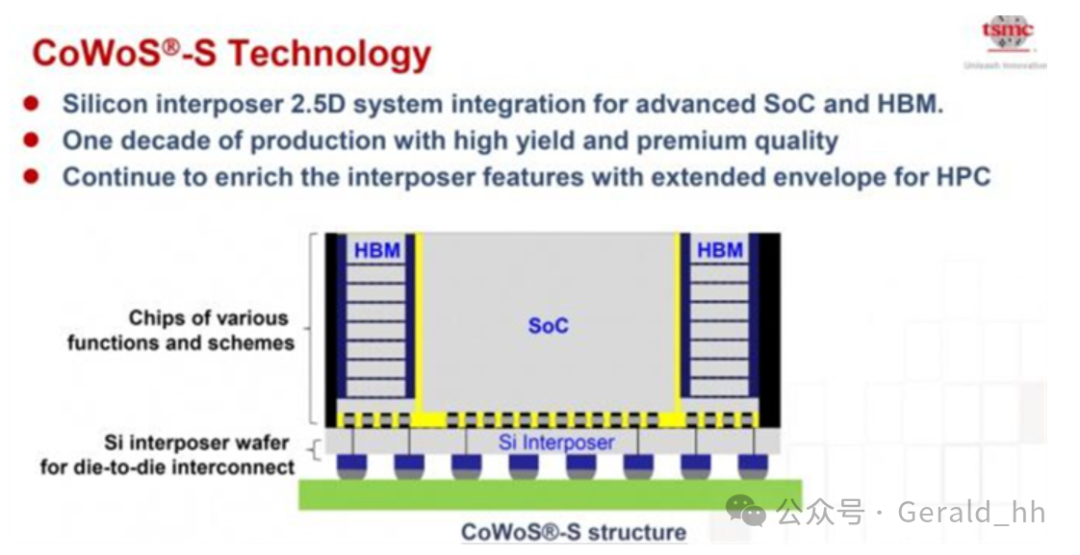

CoWoS-S 是台积电的首款 CoWoS 技术,采用单片硅中介层和硅通孔(TSV),以实现芯片和衬底之间高速电信号的直接传输。该技术可容纳最大尺寸为光罩尺寸 3.3 倍(或约 2700mm²)的中介层,并支持多达四个 HBM2/HBM2E 内存堆叠。这种封装方式显著提升了高性能计算应用的性能和集成密度。

CoWoS-R:

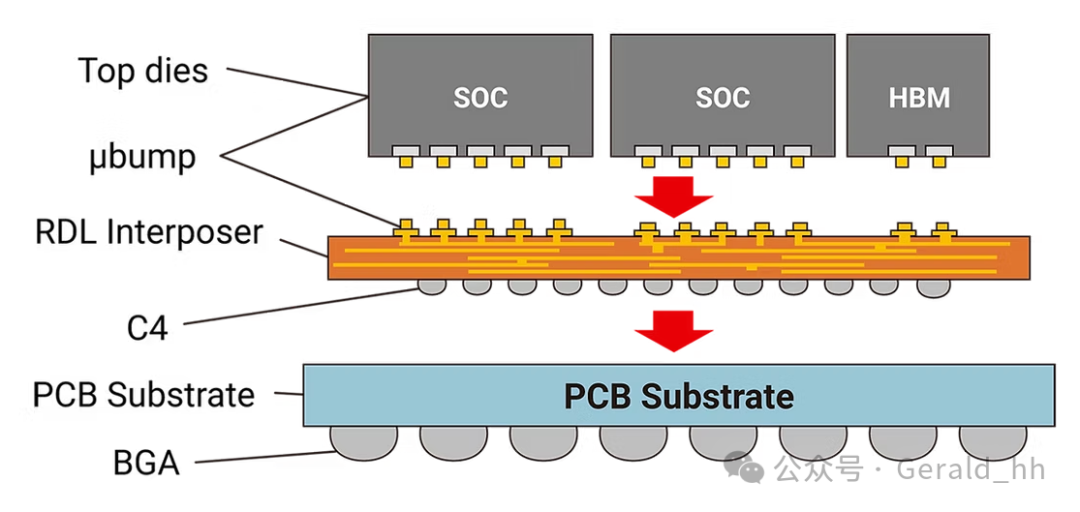

CoWoS-R结合了台积电的InFO技术和用于芯片连接的重分布层(RDL)中介层。用有机中介层取代了CoWoS-S中的硅中介层。该有机中介层具有细间距的RDL,可在HBM和芯片之间,甚至在芯片和基板之间提供高速连接。与CoWoS-S相比,CoWoS-R具有更高的可靠性和良率,因为有机中介层本身具有柔性,可以起到应力缓冲作用,从而缓解因基板和中介层热膨胀系数不匹配而导致的可靠性问题。

RDL interposer:重分配层 (RDL) 用于重新分配芯片与封装基板之间的电气连接。RDL 通常由聚合物材料和铜线构成,将芯片的输入/输出 (I/O) 信号重新分配到封装触点。这使其具有出色的机械柔韧性和电气性能,能够处理高密度互连并确保信号完整性。重分配层 (RDL) 用于重新分配芯片与封装基板之间的电气连接。RDL 通常由聚合物材料和铜线构成,将芯片的输入/输出 (I/O) 信号重新分配到封装的各个触点。这使其具有出色的机械柔韧性和电气性能,能够处理高密度互连并确保信号完整性。

C4 bump:这些连接通过 RDL 层连接不同的芯片和高带宽存储器 (HBM),提供稳定可靠的电气连接。这些连接点通过 RDL 层连接不同的芯片和高带宽存储器 (HBM),提供稳定可靠的电气连接。

(图片来源:台积电)CoWoS封装技术架构——该图展示了CoWoS封装技术的架构,图中显示了集成在同一硅中介层上的多个系统级芯片(SoC)和高带宽内存(HBM)。这些组件通过硅通孔(TSV)连接到PCB基板。

CoWoS-L:

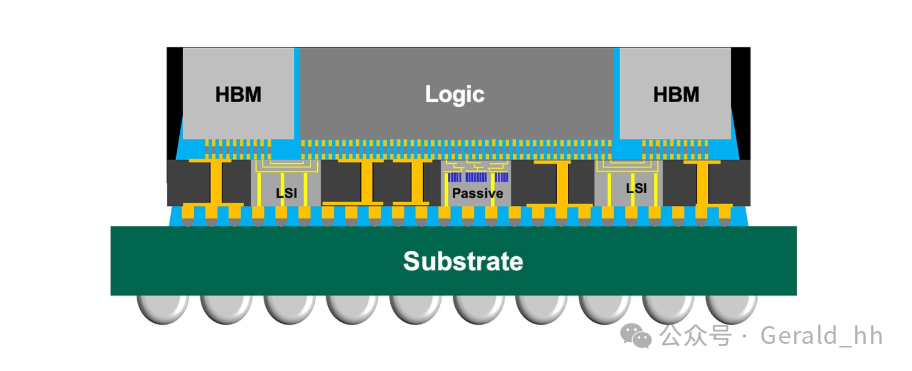

CoWoS-L 是台积电 CoWoS 平台内的一种芯片后封装技术。它结合了 CoWoS-S 和 InFO 技术的优势,该技术采用局部硅互连(LSI)和RDL中介层,共同构成重组中介层(RI)。除了RDL中介层外,它还保留了CoWoS-S的硅通孔(TSV)这一优势。这也有助于缓解CoWoS-S中因使用大型硅中介层而导致的良率问题。在某些实现方案中,为了最大限度地降低插入损耗,还可以使用绝缘体通孔(TIV)代替TSV。

局部硅互连(LSI):LSI 芯片用于芯片之间的高密度互连,从而实现高效的数据传输和低延迟。

Redistribution Layer (RDL):RDL层负责电力和信号传输,提供稳定可靠的电气连接。

Packaging Structure:从 1.5 倍光掩模尺寸的中介层开始,逐步扩展以集成更多芯片,以适应各种应用需求。

(图片来源:台积电官网)此图展示了CoWoS-L技术的封装结构。图中可见高带宽内存(HBM)和片上系统(SoC)通过局部硅互连(LSI)芯片和重分布层(RDL)互连。这些组件最终集成到基板(PCB)上。

CoWoS-L封装的组成部分和制造步骤:

1.CoWoS-L 是一种芯片后组装工艺,因为首先制造中介层,然后将晶圆芯片堆叠在其上。中介层是 CoWoS 技术中的关键原材料之一,因为多个晶圆芯片(例如 SoC、HBM 等)都安装在中介层上,从而实现了芯片之间的高效连接和通信。中介层制造完成后,下一步是在晶圆芯片上创建通孔绝缘通孔 (TIV)。

2.然后将已知合格的芯片(KGD)安装到晶圆上。芯片与TIV之间的间隙用封装材料填充,之后采用CMP工艺获得平整的表面。

3.下一步,制造两个RDL层。一个位于中介层正面,通过μ-bump连接晶圆和基板。第二个 RDL 位于中介层背面,通过 C4 bump连接中介层和基板。

此外,CoWoS-L技术还采用了深沟槽电容器(DTC),这种电容器具有高电容密度,可提升系统的电气性能。这些电容器充当电荷存储器,满足高速计算应用运行时瞬时电流的需求。

-

台积电

+关注

关注

44文章

5811浏览量

177057 -

封装技术

+关注

关注

12文章

605浏览量

69367 -

CoWoS

+关注

关注

0文章

170浏览量

11536

原文标题:多芯片封装技术——CoWoS@TSMC

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

台积电第五代CoWoS封装技术即将问世 晶圆代工优势扩大

台积电CoWoS订单增加 生产线满载运行

消息称台积电将CoWoS部分流程外包给OSAT

报告称台积电改机增CoWoS产能 预估明年倍增

曝台积电考虑引进CoWoS技术

曝台积电考虑引进CoWoS技术 筹划日本建先进封装产能

台积电加速扩产CoWoS,云林县成新封装厂选址

消息称台积电首度释出CoWoS封装前段委外订单

台积电CoWoS产能将提升4倍

台积电CoWoS封装A1技术介绍

台积电CoWoS技术的基本原理

台积电CoWoS技术的基本原理

评论