以下文章来源于算力冷时代圈,作者冷时代

台积电在先进封装技术,特别是CoWoS(Chip on Wafer on Substrate)平台上的微通道芯片液冷技术路线,是其应对高性能计算和AI芯片高热流密度挑战的关键策略。本报告将基于台积电相关的研究成果和已发表文献,深入探讨其微通道芯片封装液冷技术的演进路线。

作为全球领先的晶圆代工企业,台积电在先进封装技术方面持续创新,其研发的CoWoS平台,已成为集成高带宽内存(HBM)和多个系统级芯片(SoC)的关键技术 。CoWoS技术虽然极大地提升了芯片的集成度和性能,但也带来了前所未有的散热挑战。为此,台积电及其生态系统伙伴积极探索并部署一系列前沿液冷解决方案,以期有效管理这些高性能芯片所产生的巨大热量,其技术演进主要体现在以下几个方面。

一、CoWoS平台与芯片液冷的初期探索

(2009年前后)

CoWoS技术是台积电开发的一种2.5D/3D堆叠异构集成封装解决方案,通过将多个芯片集成在单一硅中介层上实现高密度互联。

工艺流程分为两个主要步骤:首先芯片通过Chip-on-Wafer(CoW)的方式连接到硅晶圆,随后,将此结构与基板(Substrate)结合,形成完整的CoWoS封装。硅中介层作为核心技术组件,利用微凸块(μBumps)和硅通孔(TSV)替代传统引线键合,显著提升了芯片间的互联密度和数据传输带宽。

图1:CoWoS 2.5D封装示意图

技术应用:该技术广泛应用于数据中心和AI系统的HPC领域,以集成大型中介层、SoC芯片和高带宽内存(HBM)单元。

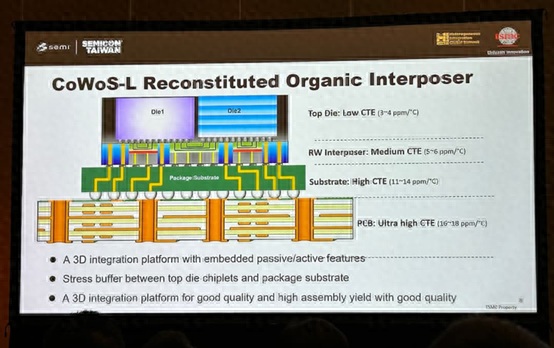

分类与演进:根据硅中介层的设计差异,台积电将CoWoS封装技术分为三种类型——CoWoS-S(Silicon Interposer)、CoWoS-R(RDL Interposer)以及CoWoS-L(Local Silicon Interconnect and RDL Interposer)。根据台积电披露信息,第一个3.5倍光罩尺寸的CoWoS-L 已经开发完成,并于2024年进入生产。针对 5.5倍光罩尺寸中介层的新CoWoS-L开发已于今年开始,以满足封装的更高性能目标。

随着芯片功耗的增加以及芯片内部热点区域热流密度达到500W/cm²以上,芯片液冷成为关键技术,这为后续台积电在CoWoS平台上集成芯片液冷方案奠定了理论基础。

二、微通道芯片液冷的集成与验证

2025年

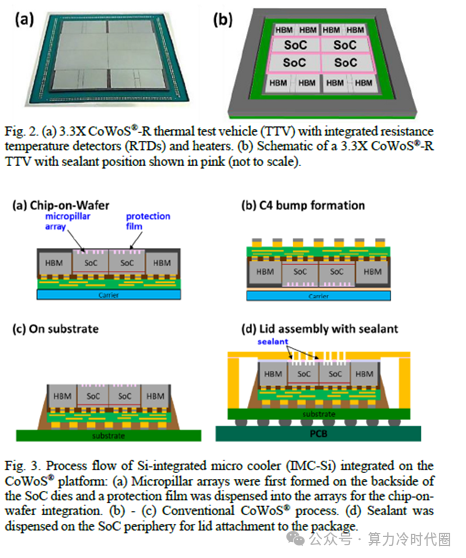

为了解决CoWoS平台上的高功率和高功率密度散热问题,台积电已在2025年的研究中展示了一种芯片液冷解决方案——硅集成微通道冷却系统(IMC-Si)。

IMC-Si 通过SoIC晶圆键合技术,在 SoC 芯片背面制造蛋形硅微柱阵列,冷却液直接流经硅微柱间隙,与芯片热源实现无 TIM 层接触,将热阻降低至趋近于零。阵列高度 150μm,直径 340×220μm,形成硅集成微通道。(前文我们对微通道进行系统分析,请点击查看微纳通道冷板的技术路线及进展)该方案已在3.3X倍光罩尺寸的CoWoS-R封装上进行了演示,其优势在于只需对现有CoWoS工艺流程进行最小化修改。这种芯片液冷解决方案通过在硅逻辑芯片和液体歧管盖之间点胶一种耐翘曲密封剂来形成,实现了冷却剂与芯片的直接接触 。

这标志着微通道芯片液冷技术从概念验证走向实际应用的关键一步,为未来高性能计算和AI应用提供了强大的散热支持。

图2:芯片液冷在 CoWoS平台上的集成工艺流程

三、微通道芯片液冷设计与优化

持续进行

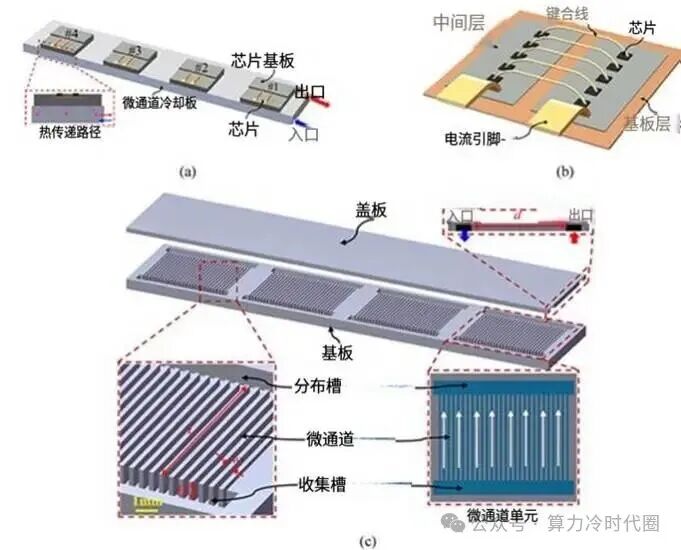

下图展示了微通道芯片液冷的详细技术图,包括芯片冷却组件的分解图、芯片相关组件的内部结构图以及微通道冷却板的详细视图,这些都用于解释微通道芯片液冷系统的结构和工作原理 。

图3:微通道芯片液冷技术图

结构多样化:研究人员对不同结构的微通道设计进行了评估,例如微通道热沉(MCHS)、直列微针翅热沉(I-MPFHS)和交错微针翅热沉(S-MPFHS),并通过微加工和硅-硅直接键合技术集成到微通道芯片液冷系统中 。

多层微通道:多层微通道芯片液冷已被提出用于4x4芯片阵列的散热,其热流密度可达500W/cm² 。

变截面通道:为了进一步优化流动和传热性能,研究人员还提出了可变截面微通道液冷板的设计,以解决服务器芯片微通道液冷板的挑战 。这种设计有助于优化冷却液的流动,提高热交换效率 。

低热阻优化:在实验室环境中,微通道芯片液冷已被设计和表征用于冷却单芯片模块(SCM)中极高功率密度的芯片,通过多个换热区域和优化的翅片设计,实现了芯片表面与入口冷却水之间16.2°C·mm²/W的平均单位热阻 。在实际应用中,单相微通道液冷系统在流体压降为0.25 MPa时,从冷却系统表面到入口冷却水的单位热阻可达10.5°C·mm²/W。

四、芯片液冷封装与多物理场耦合分析

持续进行

台积电的微通道芯片液冷技术路线不仅关注芯片层面的冷却,也致力于封装到系统的整体热解决方案。

芯片板载封装:高功率芯片模块的芯片板载(COB)封装通过简化制造流程、降低支撑结构成本和提供更低的热阻来增强散热 。

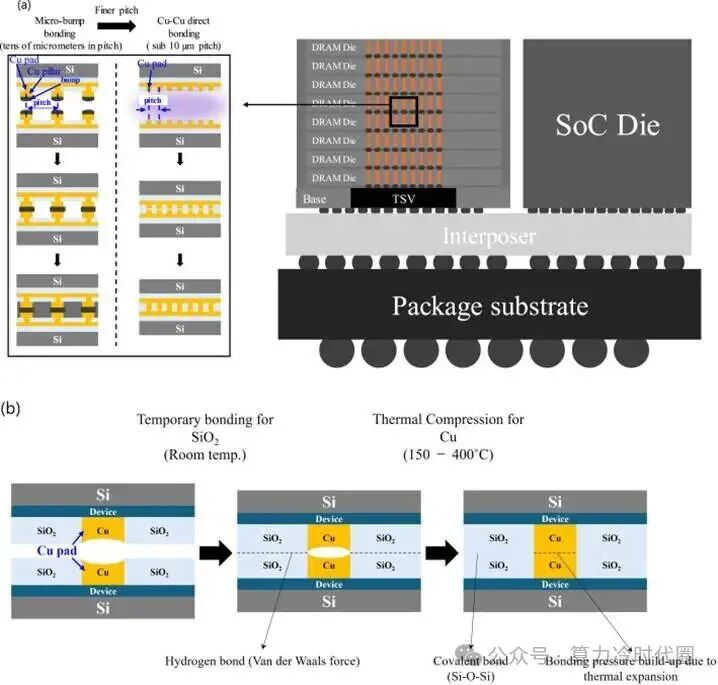

先进键合技术:在先进封装中,无凸块铜-铜键合作为下一代核心技术正在兴起,因为它能解决微凸点间距的限制,这对于将冷却结构与芯片更紧密地集成至关重要 。

图4:芯片液冷封装结构

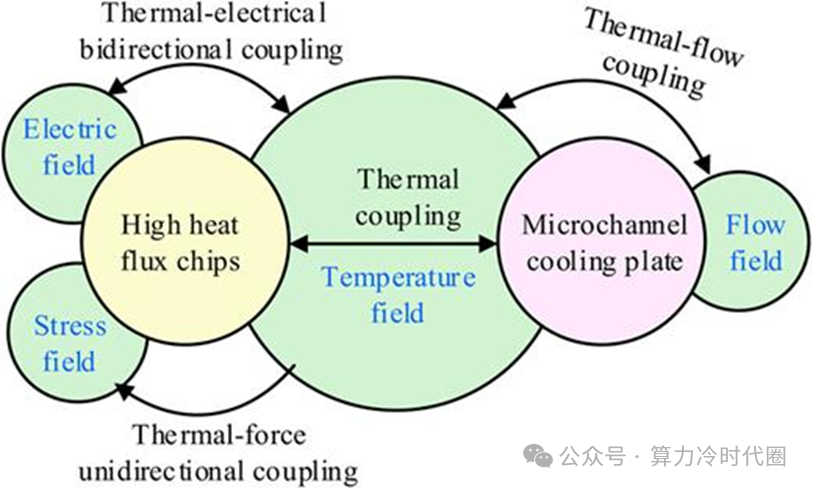

3.多物理场耦合分析:高热流密度的微通道芯片液冷系统涉及到热-流-力-电等多物理场耦合特性 。研究发现,芯片的焦耳热和冷却水流量对多场耦合效应下的冷却性能有显著影响,揭示了多场耦合效应的影响,并提出了增强微通道芯片液冷的方法 。

图5:芯片液冷多物理场耦合关系图

上图展示了高热流密度微通道芯片液冷系统中多场耦合关系的示意图,包括热-电双向耦合、热-流耦合以及热-力单向耦合等。

小结

台积电在CoWoS平台上的微通道芯片液冷技术路线,是一个持续演进的、多方面的策略。它通过将先进的液冷解决方案,如微通道直接集成到封装中,开发和优化芯片微通道结构等增强传热机制,并通过多物理场耦合分析来理解和优化冷却系统的性能,旨在有效管理高性能计算和AI芯片产生的高热流密度,从而确保未来高性能芯片的可靠性和持续发展 。

-

台积电

+关注

关注

44文章

5787浏览量

174702 -

晶圆

+关注

关注

53文章

5344浏览量

131653 -

CoWoS

+关注

关注

0文章

163浏览量

11451

原文标题:台积电高性能芯片热管理:CoWoS芯片液冷技术演进路线

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

评论