电子发烧友网综合报道

近日,据报道,台积电将持续推进先进封装技术,正式整合CoWoS与FOPLP,推出新一代CoPoS工艺。

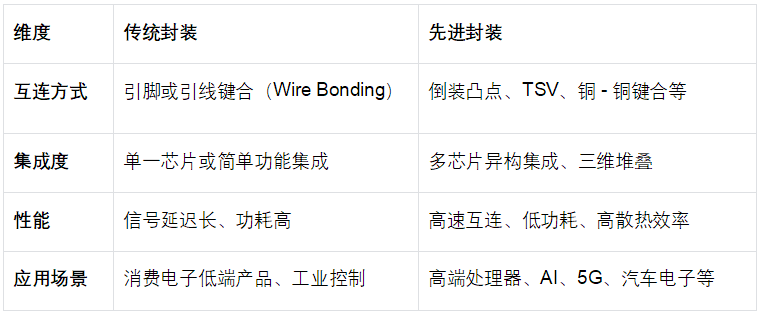

作为台积电先进封装技术的集大成者,CoPoS并非凭空出现,而是建立在成熟技术基础上的创新升级。长期以来,CoWoS作为台积电的主力封装技术,凭借在高性能计算芯片领域的稳定表现占据重要地位,但其采用的圆形硅中介层在面积利用率和大规模量产方面存在局限。

而 FOPLP作为扇出型面板级封装技术,虽能在更大面板上进行芯片封装,却在高集成度场景下的性能表现稍显不足。CoPoS的诞生正是为了融合两者优势,通过“化圆为方”的革新设计,将芯片排列在大型方形基板上,彻底打破传统圆形中介层的束缚。

CoPoS 技术的核心突破在于对封装载体和结构的全面升级。它创新性地采用玻璃或蓝宝石材质的方形载具作为中介层,并在其上镀制 RDL,这一设计不仅支持更大的光罩尺寸和更高的集成度,更有效缓解了大尺寸芯片封装过程中易出现的翘曲问题。

在尺寸与效率方面,CoPoS展现出了惊人的优势。传统300mm圆形晶圆的封装面积有限,而CoPoS支持的面板尺寸可达310x310mm、515x510mm,甚至能达到750x620mm的超大规格。

据Yole的报告数据,采用300x300mm面板时,可容纳16个中介层,面积利用率高达81%;而600x600mm面板更是能集成64个中介层,同样保持81%的高面积利用率,远超传统圆形晶圆45%的利用率水平。

面积利用率的大幅提升直接带来了成本优化,数据显示,相比传统方案,CoPoS技术可实现约10%至20%的成本下降,这对于大规模量产的AI芯片而言,意味着显著的成本优势。

在量产规划方面,台积电已为CoPoS技术制定了清晰的路线图。按照计划,首条CoPoS实验线将于2026年在台积电子公司采钰设立,为技术成熟度验证和工艺优化奠定基础。

量产阶段则将落地嘉义AP7厂的P4、P5厂区,同时美国亚利桑那州的两座先进封装厂也将同步布局,其中一座将以CoPoS技术为主。预计最快到2028年底至2029年上半年,CoPoS技术将实现大规模量产,为半导体产业注入新的活力。

随着相关设备规格与订单量确定,全球供应链企业纷纷加入竞标行列,首波供应链名单囊括 KLA、TEL、Screen、Applied Materials、Disco 等国际大厂,以及印能、辛耘、弘塑、均华、致茂、志圣等 13 家台厂。

从CoWoS到CoPoS,台积电在先进封装技术领域的持续创新,不仅推动了自身技术壁垒的提升,更深刻影响着全球半导体产业的发展格局。在AI技术加速渗透的当下,CoPoS技术的出现将以更大的尺寸、更高的效率、更低的成本,为大尺寸芯片封装提供全新解决方案,助力全球半导体产业迈向更高的集成度与性能水平,为数字经济的发展注入源源不断的动力。

近日,据报道,台积电将持续推进先进封装技术,正式整合CoWoS与FOPLP,推出新一代CoPoS工艺。

作为台积电先进封装技术的集大成者,CoPoS并非凭空出现,而是建立在成熟技术基础上的创新升级。长期以来,CoWoS作为台积电的主力封装技术,凭借在高性能计算芯片领域的稳定表现占据重要地位,但其采用的圆形硅中介层在面积利用率和大规模量产方面存在局限。

而 FOPLP作为扇出型面板级封装技术,虽能在更大面板上进行芯片封装,却在高集成度场景下的性能表现稍显不足。CoPoS的诞生正是为了融合两者优势,通过“化圆为方”的革新设计,将芯片排列在大型方形基板上,彻底打破传统圆形中介层的束缚。

CoPoS 技术的核心突破在于对封装载体和结构的全面升级。它创新性地采用玻璃或蓝宝石材质的方形载具作为中介层,并在其上镀制 RDL,这一设计不仅支持更大的光罩尺寸和更高的集成度,更有效缓解了大尺寸芯片封装过程中易出现的翘曲问题。

在尺寸与效率方面,CoPoS展现出了惊人的优势。传统300mm圆形晶圆的封装面积有限,而CoPoS支持的面板尺寸可达310x310mm、515x510mm,甚至能达到750x620mm的超大规格。

据Yole的报告数据,采用300x300mm面板时,可容纳16个中介层,面积利用率高达81%;而600x600mm面板更是能集成64个中介层,同样保持81%的高面积利用率,远超传统圆形晶圆45%的利用率水平。

面积利用率的大幅提升直接带来了成本优化,数据显示,相比传统方案,CoPoS技术可实现约10%至20%的成本下降,这对于大规模量产的AI芯片而言,意味着显著的成本优势。

在量产规划方面,台积电已为CoPoS技术制定了清晰的路线图。按照计划,首条CoPoS实验线将于2026年在台积电子公司采钰设立,为技术成熟度验证和工艺优化奠定基础。

量产阶段则将落地嘉义AP7厂的P4、P5厂区,同时美国亚利桑那州的两座先进封装厂也将同步布局,其中一座将以CoPoS技术为主。预计最快到2028年底至2029年上半年,CoPoS技术将实现大规模量产,为半导体产业注入新的活力。

随着相关设备规格与订单量确定,全球供应链企业纷纷加入竞标行列,首波供应链名单囊括 KLA、TEL、Screen、Applied Materials、Disco 等国际大厂,以及印能、辛耘、弘塑、均华、致茂、志圣等 13 家台厂。

从CoWoS到CoPoS,台积电在先进封装技术领域的持续创新,不仅推动了自身技术壁垒的提升,更深刻影响着全球半导体产业的发展格局。在AI技术加速渗透的当下,CoPoS技术的出现将以更大的尺寸、更高的效率、更低的成本,为大尺寸芯片封装提供全新解决方案,助力全球半导体产业迈向更高的集成度与性能水平,为数字经济的发展注入源源不断的动力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电

+关注

关注

44文章

5822浏览量

177174 -

封装

+关注

关注

128文章

9373浏览量

149175

发布评论请先 登录

相关推荐

热点推荐

揭秘半导体后道封装辅助小设备:UV解胶机的三大硬指标与未来趋势

在半导体先进封装的微观世界里,一颗芯片的诞生往往伴随着无数次“粘合”与“分离”。当晶圆被切割成数千颗独立的芯片后,如何在不损伤这些脆弱电路的前提下,将它们从固定薄膜上完整取下,成为了决

发表于 05-14 10:19

告别内卷?晶合集成上调10%,世界先进、力积电跟进,半导体供应链逻辑生变

导语: 2026年,半导体行业的“免费午餐”似乎正在一张张涨价函中消失。继晶圆代工龙头台积电被传调涨先进

BW-4022A半导体分立器件综合测试平台---精准洞察,卓越测量

参数,以筛选出在制造过程中就已经出现缺陷的芯片。这可以避免对有明显缺陷的芯片进行后续的封装等昂贵的工序,从而降低成本。对于像英特尔、台积电这样的大型芯片制造商,在

发表于 10-10 10:35

台积电日月光主导,3DIC先进封装联盟正式成立

9月9日,半导体行业迎来重磅消息,3DIC 先进封装制造联盟(3DIC Advanced Manufacturing Alliance,简称 3DIC AMA)正式宣告成立,该联盟由行业巨头台

台积电Q2净利润3982.7亿新台币 暴增60% 创历史新高

电在第二季度毛利率达到58.6%;营业利润率为49.6%,净利率为42.7%。 在2025年第二季度,台积

看点:台积电在美建两座先进封装厂 博通十亿美元半导体工厂谈判破裂

两座先进的封装工厂将分别用于导入 3D 垂直集成的SoIC工艺和 CoPoS 面板级大规模 2.5D 集成技术。 据悉台积

破局前行!联电拟于台湾扩产,全力布局先进封装技术

近日,半导体行业传出重磅消息,联电作为全球知名的晶圆代工厂商,正积极考虑在台湾地区进行大规模扩产,并同步布局先进封装技术,这一战略决策在业界

化圆为方,台积电整合推出最先进CoPoS半导体封装

化圆为方,台积电整合推出最先进CoPoS半导体封装

评论