一、技术前沿探索:从微小到宏大的CoWoS封装技术演进

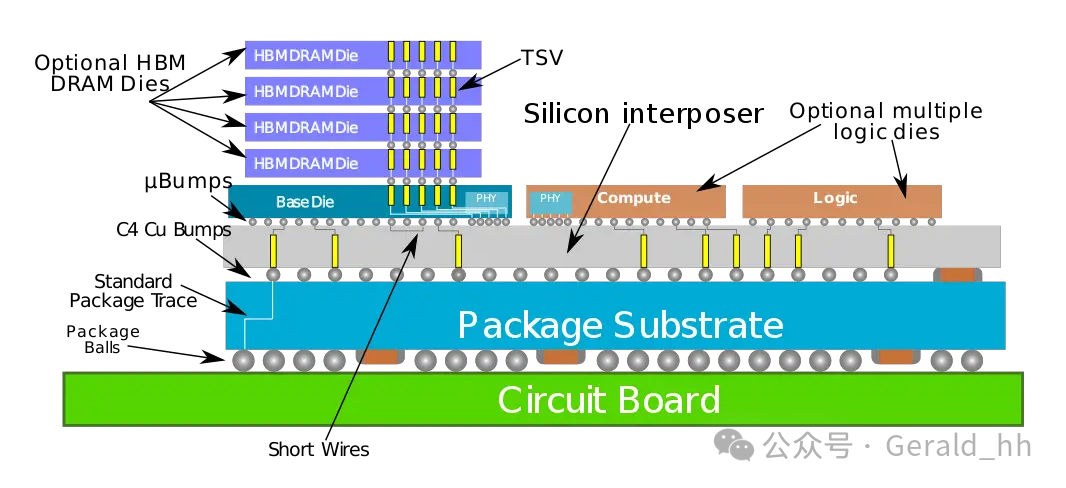

在半导体技术的浩瀚星空中,每一次技术的革新都如同星辰般璀璨夺目。去年台积电在欧洲开放创新平台(OIP)论坛上透露的超大版本CoWoS(晶圆上芯片)封装技术,无疑成为了业界关注的焦点。这项技术不仅预示着半导体封装领域的一次重大突破,更将为高性能计算(HPC)与人工智能(AI)领域带来革命性的性能提升。 希望常见面的话,点击上方即刻关注,设为星标! 二、从1.5到9:CoWoS封装技术的跨越式发展 自2016年台积电首次推出CoWoS技术以来,这一创新封装技术便以其独特的设计理念和卓越的性能表现,赢得了业界的广泛赞誉。从最初的1.5个掩模尺寸,到如今即将推出的9个掩模尺寸的终极版CoWoS,每一次技术的迭代都标志着性能与容量的双重飞跃。

特别是在3.3个掩模尺寸的CoWoS技术面世后,它成功地将8个HBM3堆栈纳入一个封装中,为高性能计算领域提供了全新的解决方案。然而,对于追求极致性能的客户而言,这些进步仍然只是冰山一角。为了满足这些客户的迫切需求,台积电再次发力,推出了更大尺寸的CoWoS封装技术。

三、性能怪兽的诞生:超大版CoWoS封装技术的潜力

借助超大版CoWoS封装技术,AI和HPC芯片设计人员将能够构建出前所未有的高性能处理器。这些处理器不仅体积小巧,而且性能卓越,足以满足最苛刻的应用需求。无论是复杂的科学计算、大规模的数据分析,还是前沿的AI算法训练,这些处理器都将游刃有余。

更令人兴奋的是,台积电还计划将其系统级集成芯片(SoIC)先进封装技术与超大版CoWoS封装技术相结合。这意味着客户可以将不同工艺节点的芯片垂直堆叠在一起,以进一步提高晶体管数量和性能。例如,借助9个掩模尺寸的CoWoS技术,客户可以将1.6nm级芯片放置在2nm级芯片之上,从而实现前所未有的晶体管密度和性能水平。

四、挑战与应对:超大版CoWoS封装技术的实施难题

然而,任何技术的革新都伴随着挑战。对于台积电超大版CoWoS封装技术而言,其面临的挑战同样不容忽视。 首先,基板尺寸的增大带来了设计上的难题。随着封装尺寸的增大,基板的设计、制造和测试难度也随之增加。这不仅需要更高的技术水平,还需要更多的资源和时间投入。 其次,电源与冷却问题同样棘手。随着基板尺寸的增大和功耗的增加,每个机架的电源功率可能达到数百千瓦。为了有效管理这些高功率处理器,需要采用先进的液体冷却和浸没方法。这不仅增加了数据中心的运营成本,也对数据中心的物理布局和散热设计提出了新的要求。 为了应对这些挑战,台积电正在积极寻求解决方案。一方面,他们正在加强与产业链上下游企业的合作,共同推动封装技术的创新和发展。另一方面,他们也在不断探索新的散热技术和能源管理方案,以降低数据中心的运营成本和能耗。

五、展望未来:开启半导体封装技术的新篇章

随着台积电超大版CoWoS封装技术的逐步推进,我们有理由相信,半导体封装领域将迎来一场深刻的变革。这一技术不仅将推动AI和HPC领域的发展,更将为整个半导体行业带来新的机遇和挑战。 对于台积电而言,这一技术的成功推出将进一步巩固其在半导体封装领域的领先地位。同时,这也将激发更多的创新灵感,推动台积电在封装技术方面不断突破自我,开启半导体封装技术的新篇章。 而对于整个半导体行业而言,台积电超大版CoWoS封装技术的推出将促进产业链上下游企业的协同发展。从芯片设计到封装测试,从设备制造到材料供应,每一个环节都将迎来新的发展机遇。这将推动整个半导体行业向更高层次迈进,为全球科技产业的繁荣发展注入新的动力。

-

封装

+关注

关注

128文章

9333浏览量

149052 -

AI

+关注

关注

91文章

41156浏览量

302624 -

CoWoS

+关注

关注

0文章

170浏览量

11536

原文标题:【芯片封装】台积电超大版CoWoS封装技术:重塑高性能计算与AI芯片架构

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

台积电如何为 HPC 与 AI 时代的 2.5D/3D 先进封装重塑热管理

台积电超大版CoWoS封装技术:重塑高性能计算与AI芯片架构

台积电超大版CoWoS封装技术:重塑高性能计算与AI芯片架构

评论