来源:半导体芯闻综合

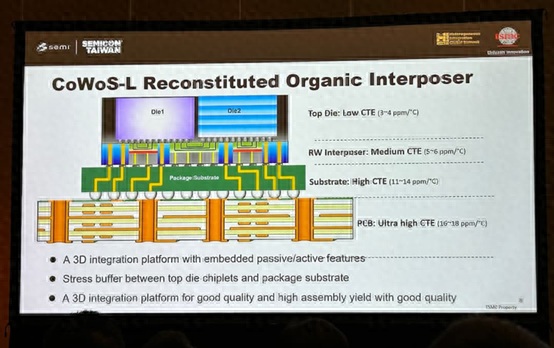

台积电高效能封装整合处处长侯上勇3 日在Semicon Taiwan 2024 中举行专题演讲,表示被视为是三种CoWoS 产品中,能满足所有条件的最佳解决方案,因此会从CoWoS-S 逐步转移至CoWoS -L,并称CoWoS-L 是未来路线图要角。

侯上勇指出,台积电过去的三场演讲,于2012 年发表3D-IC 模组、TSV、微凸块(micro bond)和临时载板制程;2016 年第二次讲座,重点是HBM 逻辑整合;2020 年第三场则确定矽中介层可扩展三倍光罩尺寸;现在则是第四个讲座的最佳时机。

侯上勇认为,由于顶部芯片(Top Die)成本非常高,CoWoS-L 是比CoWoS-R、CoWoS-S 更能满足所有条件的最佳解,且因为具有灵活性,可在其中介层实现异质整合,会有其专精的尺寸与功能。

他提到,CoWoS-L 可相容于各式各样的高效能顶级芯片,例如先进逻辑、SOIC 和高频宽记忆体。

此外,台积电也根据整体系统散热方案开发各种散热解决方案,而共同封装光学(CPO)开发工作也在进行中。侯上勇指出,在CoWoS 封装中使用光学引擎(COUPE)的CPO,将使每瓦效能达到新里程碑。他也提到SOW(System-on-Wafer)技术,表示过去已经用于特斯拉,公司也在帮Cerebras 代工的wafer level chip。

台积电CoW-SoW 预计2027年量产

随着IC设计业者透过增加芯片尺寸提高处理能力,考验芯片制造实力。辉达AI芯片Blackwell,被CEO黄仁勋誉为「非常非常大的GPU」,而确实也是目前业界面积最大的GPU,由两颗Blackwell芯片拼接而成,并採用台积电4纳米制程,拥有2,080亿个电晶体,然而难免遇到封装方式过于复杂之问题;台湾坐拥全球最先进芯片制造,未来有望成为AI重要硅岛。

CoWoS-L封装技术,使用LSI(本地硅互连)桥接RDL(硅中介层)连接晶粒,传输速度可达10/TBs左右;不过封装步骤由于桥接放置精度要求极高,稍有缺陷都可能导致价值4万美元的芯片报废,从而影响良率及获利。

法人透露,由于GPU晶粒、LSI桥接、RDL中介层和主基板之间的热膨胀系数(CTE)相异,导致芯片翘曲、系统故障。为提升良率,辉达重新设计GPU芯片顶部金属层和凸点。不只是AI芯片RTO(重新流片)修改设计,据供应链透露,准备发布之50系列的显卡也需要RTO,上市时间较原本递延。

芯片设计问题将不会只是辉达所独有。供应链透露,这类问题只会越来越多,不过为了消除缺陷或为提高良率而变更芯片设计于业内相当常见。AMD执行长苏姿丰曾透露,随着芯片尺寸不断扩大,制造复杂度将不可避免地增加。次世代芯片需要在效能和功耗方面取得突破,才能满足AI数据中心对算力的巨大需求。

以开发全球最大AI芯片的Cerebras指出,多芯片组合技术难度将呈现指数级成长,强调「一整片晶圆就是一个处理器」,Cerebras的Wafer-Scale Engine(WSE)系列即採用AI领域知名的「晶圆级处理器」。依照台积电一直在发展晶圆级系统整合技术 InFO-SoW(System-on-Wafer),Dojo超级电脑训练区块(Training Tile)就是基于台积电InFO-SoW并已量产的首款解决方案。

因应大芯片趋势、及AI负载需要更多HBM,台积电计划结合InFO-SoW和SoIC为CoW-SoW,将记忆体或逻辑芯片堆迭于晶圆上,并预计在2027年量产。可预见的未来,将看到更多在整片晶圆上迭迭乐的巨无霸AI芯片出现。

台积电直言,硅光大有可为

台湾半导体制造公司和全球顶尖芯片设计商及供应商正在加紧开发下一代硅光子解决方案,目标是在未来三到五年内使该技术投入生产。

他们的努力正值整个行业努力解决人工智能计算繁荣所需的大量能源和更快的数据传输速度之际。硅光子学将硅芯片与光学技术相结合,有望在这两个方面取得进步。

台积电集成互连与封装副总裁 KC Hsu 表示,硅光子市场尚处于起步阶段,但从 2023 年开始将以 40% 的年复合增长率增长,到 2028 年将达到 5 亿美元。Hsu 周二在 SEMICON 台湾贸易展览会前的一个技术论坛上发表了讲话。

Hsu 表示:“增长的驱动力是高数据速率模块的需求,用于提高光纤网络容量,尤其是可插拔和共封装光学器件 (CPO)。我们认为 CPO 器件将成为未来五年内高性能计算的重要平台。”

但许在活动间隙对《日经亚洲》表示,目前还很难确定量产时间表。他表示,这种尖端技术的商业化和大规模产出取决于客户的支持和订单。

共封装光学器件是设计并直接集成到芯片封装中的微型光学系统。与当前数据中心建筑物中外部连接到人工智能服务器系统的“可插拔”解决方案相比,这是一种更先进、更集成的方法。

Marvell 光学和云连接高级副总裁兼首席技术官 Radha Nagarajan 向《日经新闻》表示,与目前的可插拔数据传输解决方案相比,采用共封装光学元件可以“节省 30% 以上的功耗”。他表示,预计未来几年 CPO 解决方案的部署将更加广泛。

“目前已经有一些 [CPO] 部署……但数量非常少,”Nagarajan 说道。“两到三年后,你会看到数量回升。”

他补充说,应用的瓶颈主要在于在芯片层面生产这种新型光学引擎,以及部署能够容纳它们的人工智能计算系统。这涉及重新设计人工智能芯片,将光学互连作为其结构的内部部分。

芯片材料供应商 Soitec 业务部总经理 Rachid Taibi 表示,Meta 和微软等大型数据中心公司是支持 CPO 技术开发的公司之一,因为它具有低功耗的优势。

业界将硅光子技术视为实现人工智能、数据通信、6G 和量子计算等广泛应用的关键技术。与传统数据传输技术相比,光传输更节能、延迟更低,这些特性有助于解决人工智能数据中心日益增长的热量和能耗问题。

台积电的许志强表示,将该技术从外部可插拔解决方案缩小到芯片封装级别,可以实现更快的数据传输,并且每一代带宽都可能翻倍。

然而,采用这项技术将需要整个供应链中更多参与者的支持。

许世友在 SEMI 硅光子产业联盟启动仪式后表示:“硅光子生态系统仍处于早期阶段,需要不断发展。”

他说,构建该技术的生态系统需要整个供应链上的公司参与,从设计软件供应商新思科技(Synopsys)和楷登电子(Cadence Design Systems)、芯片开发商英伟达(Nvidia)和超威半导体(Advanced Micro Devices)等上游企业,一直到人工智能服务器制造商富士康和广达电脑等下游公司。

该新产业联盟的成员包括台积电、富士康、广达电脑等 30 多家供应商,以及全球最大的芯片封装和测试供应商日月光科技控股和领先的连接器供应商 Bizlink。

【近期会议】

10月30-31日,由宽禁带半导体国家工程研究中心主办的“化合物半导体先进技术及应用大会”将首次与大家在江苏·常州相见,邀您齐聚常州新城希尔顿酒店,解耦产业链市场布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二届半导体先进封测产业技术创新大会”将再次与各位相见于厦门,秉承“延续去年,创新今年”的思想,仍将由云天半导体与厦门大学联合主办,雅时国际商讯承办,邀您齐聚厦门·海沧融信华邑酒店共探行业发展!诚邀您报名参会:https://w.lwc.cn/s/n6FFne

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇

-

台积电

+关注

关注

44文章

5811浏览量

177057 -

封装

+关注

关注

128文章

9333浏览量

149052

发布评论请先 登录

台积电计划建设4座先进封装厂,应对AI芯片需求

台积电再扩2纳米产能:AI狂潮下的产能豪赌

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

台积电封装,新规划

台积电封装,新规划

评论