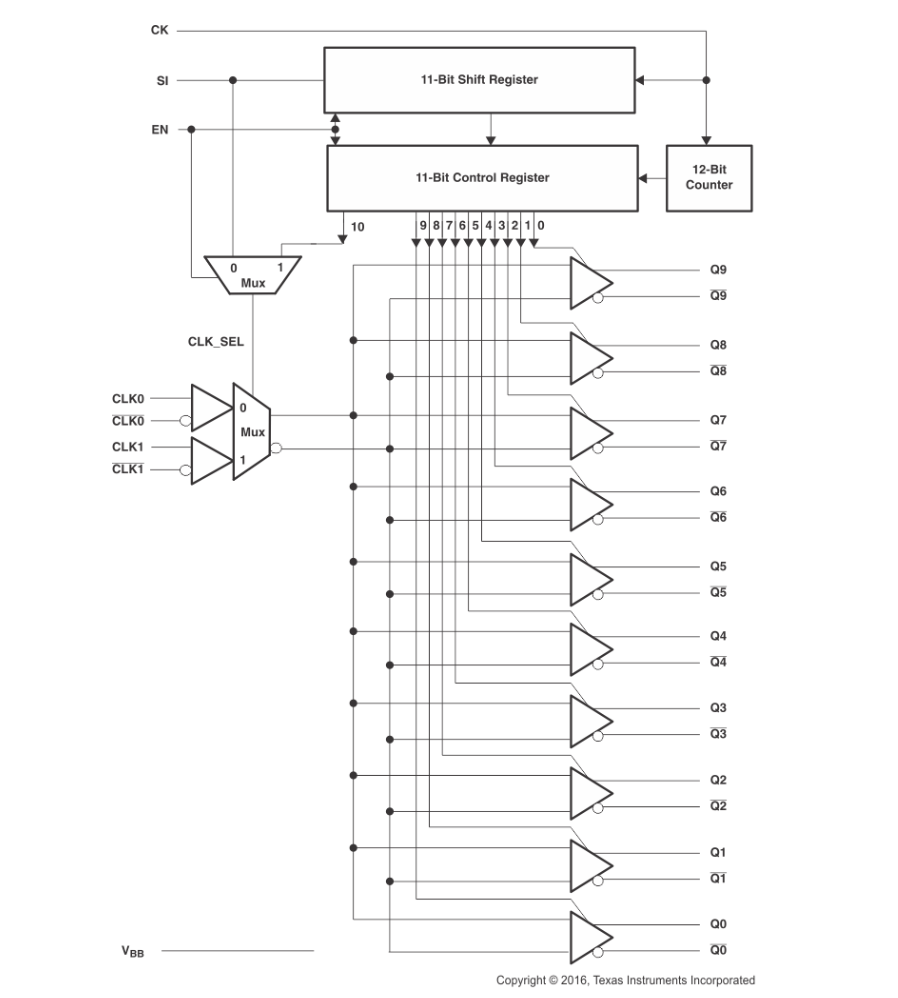

CDCLVD110A时钟驱动器分配一对差分LVDS时钟输入 (CLK0 或 CLK1)到 10 对差分时钟输出(Q0 至 Q9),最小偏移 时钟分配。该CDCLVD110A专门设计用于驱动 50 Ω变速箱 线。

当控制使能为高电平 (EN = 1) 时,10 个差分输出可编程 每个输出都可以根据加载到移位寄存器的前10位单独使能或禁用

(3态)。一旦换班 寄存器加载时,最后一位选择 CLK0 或 CLK1 作为时钟输入。但是,当 EN = 0,输出不可编程,所有输出都已启用。

*附件:cdclvd110a.pdf

该CDCLVD110A具有改进的启动电路,可最大限度地减少交流和交流 直流耦合系统。

该CDCLVD110A的工作温度范围为 –40°C 至 85°C。

特性

- 低输出偏斜 <30 ps(典型值),适用于时钟分配应用

- 将一个差分时钟输入分配给10个LVDS差分时钟输出

- V

CC范围:2.5 V ±5% - 高达 1.1 GHz 的典型信令速率能力

- 可配置寄存器 (SI/CK) 单独启用禁用输出、可选 CLK0、CLK0 或 CLK1、CLK1 输入

- 全轨到轨共模输入范围

- 接收器输入阈值:±100 mV

- 采用 32 引脚 LQFP 和 VQFN 封装

- V的故障安全I/O引脚

DD= 0 V(断电)

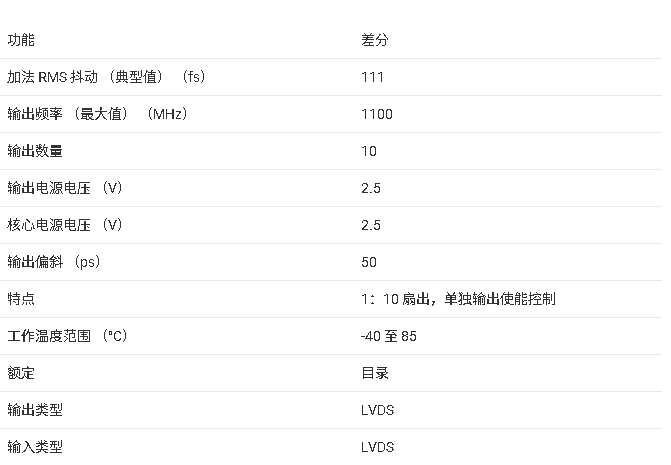

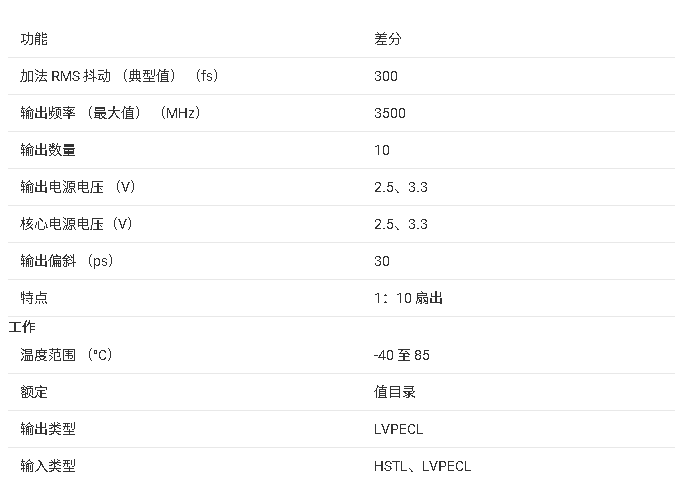

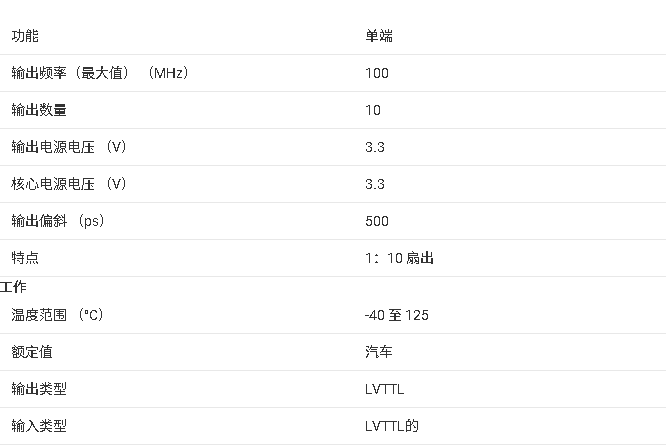

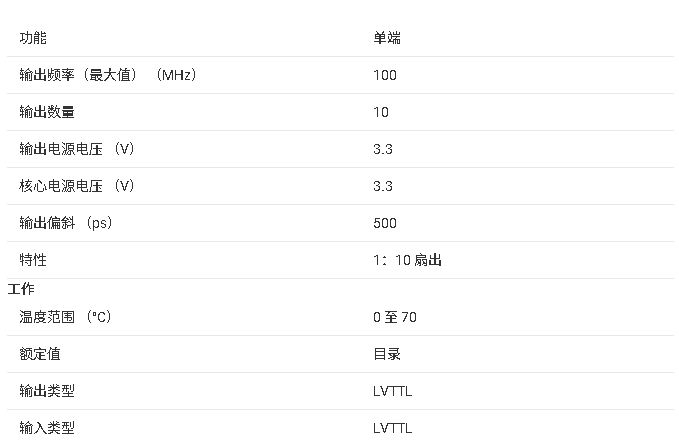

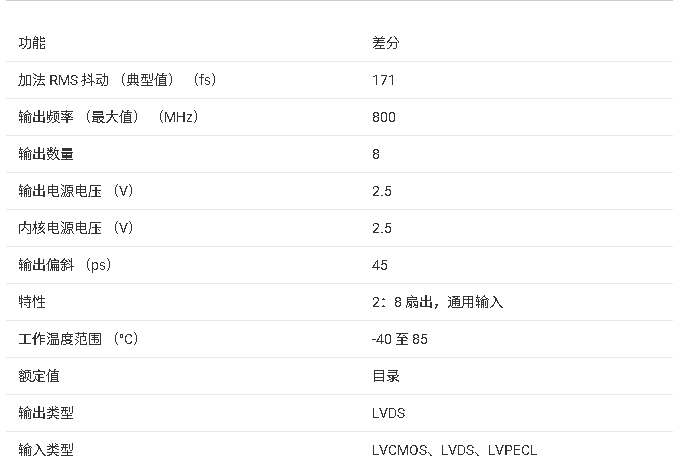

参数

方框图

1. 产品概述

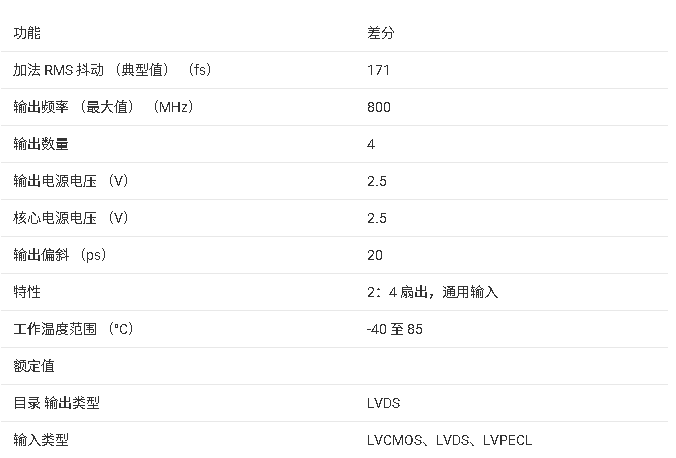

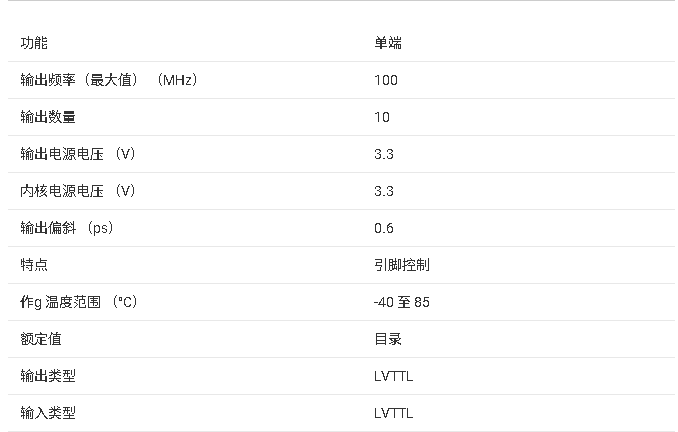

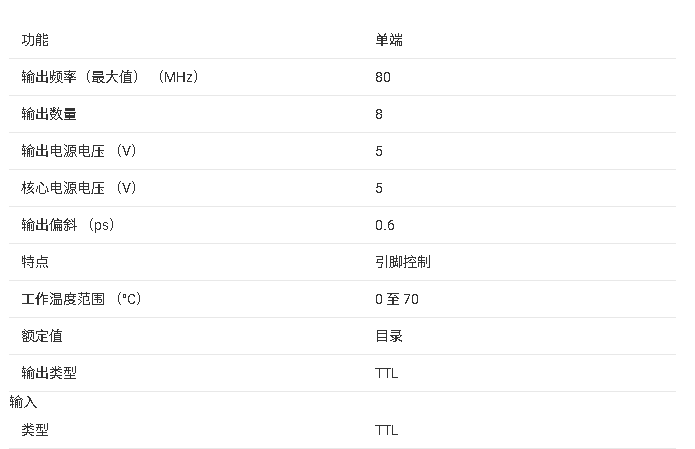

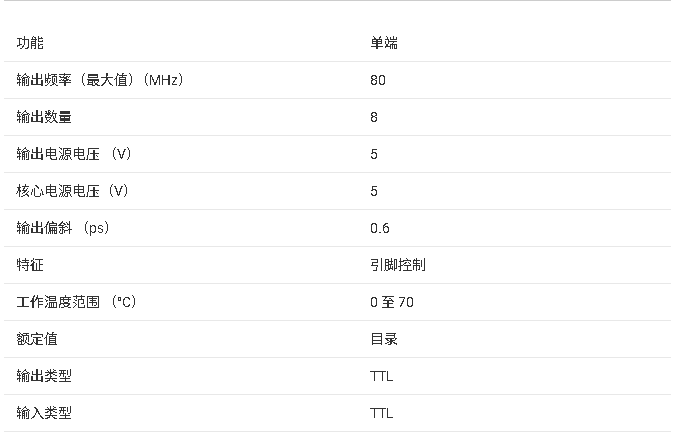

CDCLVD110A是德州仪器(TI)推出的可编程低压1:10 LVDS时钟驱动器,专为低抖动、高精度时钟分配设计。核心功能包括:

- 将1对差分LVDS时钟输入(CLK0或CLK1)分配至10对差分输出(Q0-Q9)

- 典型输出偏斜<30 ps,支持最高1.1 GHz信号速率

- 工作电压范围:2.5V ±5%,工作温度-40°C至85°C

2. 关键特性

- 低抖动性能:典型附加相位抖动281 fs(30.72MHz)和111 fs(125MHz)

- 可编程控制:通过串行接口(SI/CK)独立启用/禁用输出,支持输入时钟选择

- 封装选项:32引脚LQFP(7x7mm)和VQFN(5x5mm)封装

- 失效保护:支持VDD=0V时的I/O引脚安全模式

3. 应用场景

4. 技术细节

- 输入兼容性:支持LVDS/LVPECL/LVCMOS输入,需匹配终端电阻(如LVDS需100Ω)

- 输出配置:支持AC/DC耦合,未用输出可悬空

- 控制逻辑:

- 标准模式(EN=0) :所有输出启用,通过SI选择CLK0/CLK1

- 编程模式(EN=1) :11位移位寄存器控制输出使能及输入选择

5. 设计建议

-

可编程

+关注

关注

2文章

1314浏览量

41336 -

移位寄存器

+关注

关注

3文章

338浏览量

23179 -

lvds

+关注

关注

2文章

1216浏览量

69138 -

时钟驱动器

+关注

关注

0文章

96浏览量

14345

发布评论请先 登录

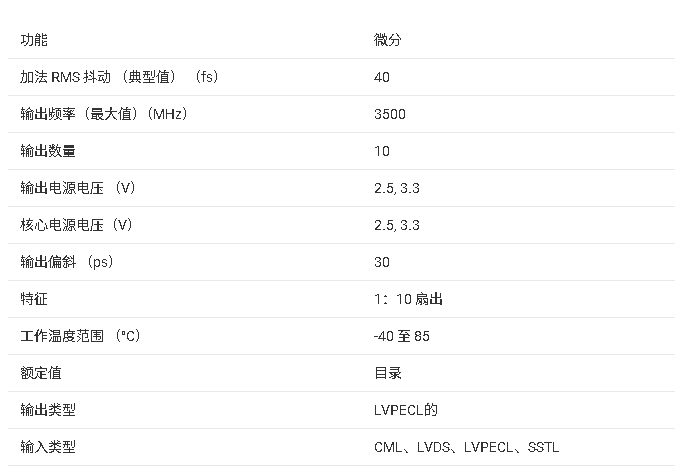

可编程低电压1:10 LVDS时钟驱动器ADN4670

CDCLVD110A可编程低压1:10 LVDS时钟驱动器数据表

CDCLVP111 低电压1:10 LVPECL时钟驱动器技术文档总结

CDCLVP110 1:10 LVPECL/HSTL时钟驱动器技术文档总结

CDC2351-Q1 1:10时钟驱动器技术文档总结

CDC329A 时钟驱动器技术文档总结

CDC2351 1线转10线时钟驱动器技术文档总结

CDCLVD110A 1:10 LVDS时钟驱动器技术文档总结

CDCLVD110A 1:10 LVDS时钟驱动器技术文档总结

评论