该CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到十个输出 (Y),时钟分配的偏斜最小。输出使能 (OE) 输入将输出禁用为高阻抗状态。每个输出都有一个内部串联阻尼电阻,以提高负载的信号完整性。该CDC2351的工作电压为标称电压为3.3V V CC .

传播延迟在工厂使用 P0 和 P1 引脚进行调整。工厂调整可确保零件到零件的偏斜最小化,并保持在指定的窗口内。引脚 P0 和 P1 不适合客户使用,应连接到 GND。

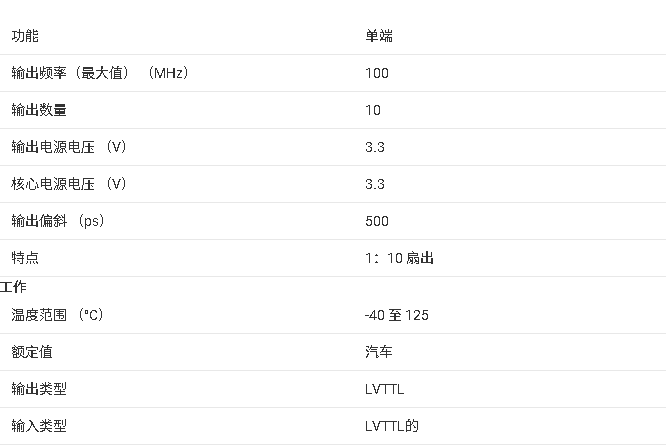

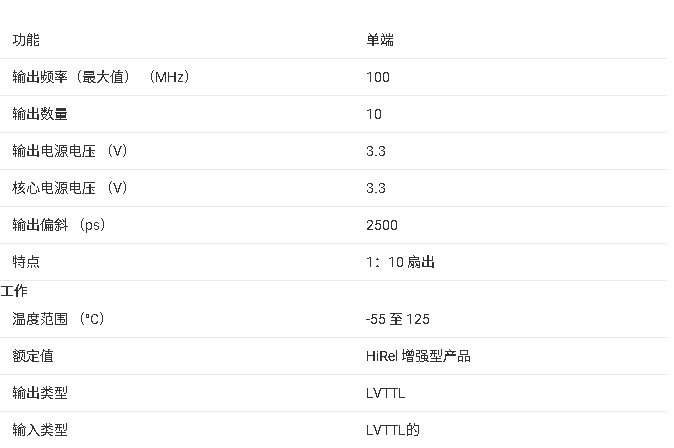

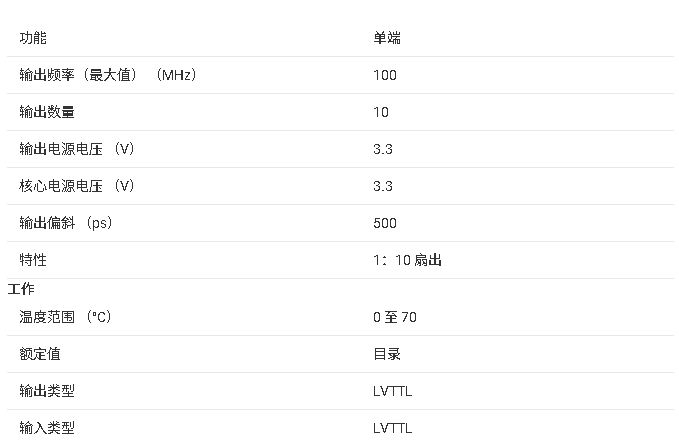

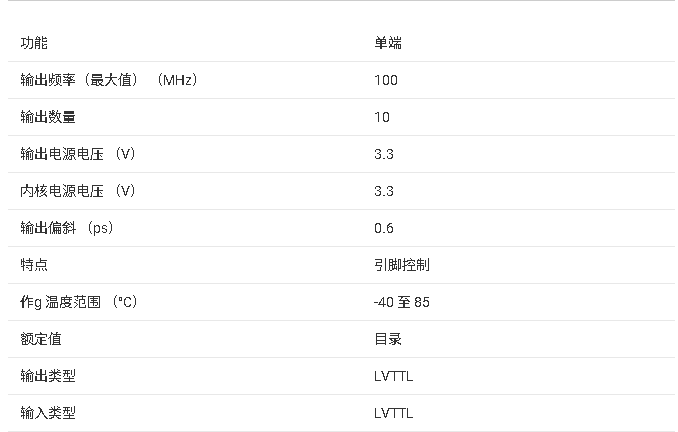

该CDC2351的特点是在 0°C 至 70°C 范围内工作。 该CDC2351Q的特点是在 -40°C 至 125°C 的整个汽车温度范围内工作。

*附件:cdc2351-q1.pdf

特性

- 低输出偏斜、低脉冲偏移,适用于时钟分配和时钟生成应用

- 工作电压为 3.3V V

CC - LVTTL兼容输入和输出

- 支持混合模式信号作(5V 输入和输出电压为 3.3V V

CC) - 将一个时钟输入分配到十个输出

- 输出具有内部串联阻尼电阻,以减少传输线效应

- 分布式V

CC接地引脚可降低开关噪声 - 最先进的 EPIC-II B^TM的^BiCMOS设计显著降低功耗

- 封装选项包括塑料小外形 (DW) 和收缩小外形 (DB) 封装

- 可用于 Q-Temp 汽车高可靠性 汽车应用配置 控制/打印 支持汽车标准认证

参数

1. 核心产品特性

- 时钟分配能力:1:10高精度时钟分配,专为低偏斜应用设计

- 电气特性:

- 工作电压:3.3V±10%(支持5V混合信号输入)

- 频率范围:0-100MHz(工业级)/200MHz(降额使用)

- 输出偏斜:<0.5ns(典型值)

- 关键设计:

- 内部串联阻尼电阻(减少传输线效应)

- 分布式电源引脚(降低开关噪声)

- EPIC-ⅡB™ BiCMOS工艺(降低功耗)

2. 功能控制

- 输出使能(OE) :低电平有效,强制输出高阻态

- 工厂校准:通过P0/P1引脚调整传播延迟(用户需接地)

- 逻辑兼容性:LVTTL输入/输出,支持3.3V与5V混合模式

3. 物理规格

- 封装选项:

- 24引脚SSOP(DB,3.9mm×8.7mm)

- 24引脚SOIC(DW,7.5mm×15.4mm)

- 温度范围:

- 工业级:0°C至70°C

- 车规级(Q1后缀):-40°C至125°C

4. 关键参数

- 绝对最大额定值:

- 电源电压:-0.5V至4.6V

- 输入电压:-0.5V至7V

- 开关特性(3.3V供电):

- 传播延迟:3.6ns(最大4.8ns)

- 输出使能时间:≤6.3ns

5. 文档结构指引

- 功能表(Section 1):OE/A输入与输出状态关系

- 时序图(Section 6):包含tPLH/tPHL等关键参数测量方法

- 参数表格(Section 5):详细电气特性与温度系数

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源

+关注

关注

185文章

19033浏览量

264967 -

电路

+关注

关注

173文章

6091浏览量

179083 -

信号完整性

+关注

关注

68文章

1503浏览量

98338 -

时钟驱动器

+关注

关注

0文章

124浏览量

14431

发布评论请先 登录

相关推荐

热点推荐

CDC2351-EP 1线至10线时钟驱动器技术文档总结

CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到 10 个输出 (Y),时钟分配的偏斜最小。输出使能 (OE)\ 输入将输出禁用到高阻抗状态。每个输出都有一个内部

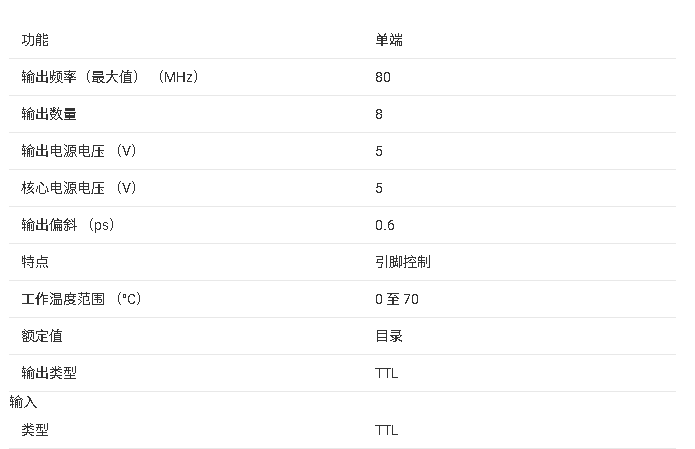

CDC341 1线至8线时钟驱动器技术文档总结

CDC341 是一款高性能时钟驱动器电路,可将一 (A) 输入信号分配到八 (Y) 输出,时钟分配偏移最小。通过使用控制引脚(1G 和 2G),无论 A 输入如何,输出都可以置于低电平

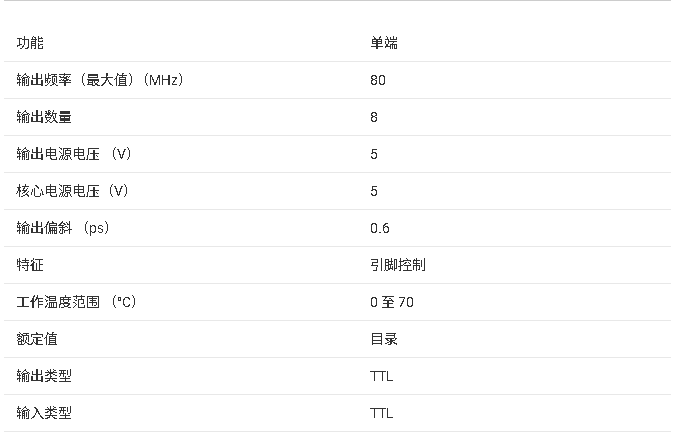

CDC340 1线至8线时钟驱动器技术文档总结

CDC340 是一款高性能时钟驱动器电路,可将一 (A) 输入信号分配给八 (Y) 输出,时钟分配偏斜最小。通过使用控制引脚(1G 和 2G),无论 A 输入如何,输出都可以置于高电平

CDC329A 时钟驱动器技术文档总结

该CDC329A包含一个时钟驱动器电路,该电路将一个输入信号分配到六个输出,时钟分配的偏斜最小。通过使用极性控制输入(T\/C),可以获得真输出和互补输出的各种组合。

该CDC3

CDC2351 1线转10线时钟驱动器技术文档总结

该CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到十个输出 (Y),时钟分配的偏斜最小。输出使能 (OE\) 输入将输出禁用为高阻抗状态。每个输出都有一个内部串联阻尼电阻,以提高负载的信号完整性。该

CDC2351-EP:高性能时钟驱动器的卓越之选

CDC2351-EP:高性能时钟驱动器的卓越之选 在时钟分配和时钟生成应用中,一款高性能的时钟驱动器至关重要。今天,我们就来深入探讨德州仪器

CDC2351:高性能时钟驱动器的卓越之选

CDC2351:高性能时钟驱动器的卓越之选 在电子设计中,时钟驱动器是确保系统时钟信号准确分配和稳定传输的关键组件。今天,我们来深入探讨德州仪器(Texas Instruments)的

CDC341:高性能1线转8线时钟驱动器的设计与应用

CDC341:高性能1线转8线时钟驱动器的设计与应用 在电子设计领域,时钟信号的精确分配至关重要。今天,我们将深入探讨德州仪器(Texas Instruments)的

CDC328A:高性能时钟驱动器的技术剖析

CDC328A:高性能时钟驱动器的技术剖析 在电子设计领域,时钟驱动器对于确保时钟信号的精确分配和稳定传输至关重要。

CDC329A:高性能1线转6线时钟驱动器的深度剖析

CDC329A:高性能1线转6线时钟驱动器的深度剖析 在电子设计领域,时钟驱动器是确保系统时钟信号稳定、准确传输的关键组件。今天,我们就来深

CDC2351:高性能时钟驱动器的卓越之选

CDC2351:高性能时钟驱动器的卓越之选 在电子工程师的日常设计工作中,时钟驱动器是确保时钟信号精准分配和传输的关键组件。今天,我们就来深入探讨一下德州仪器(TI)的

CDC2351-Q1 1:10时钟驱动器技术文档总结

CDC2351-Q1 1:10时钟驱动器技术文档总结

评论