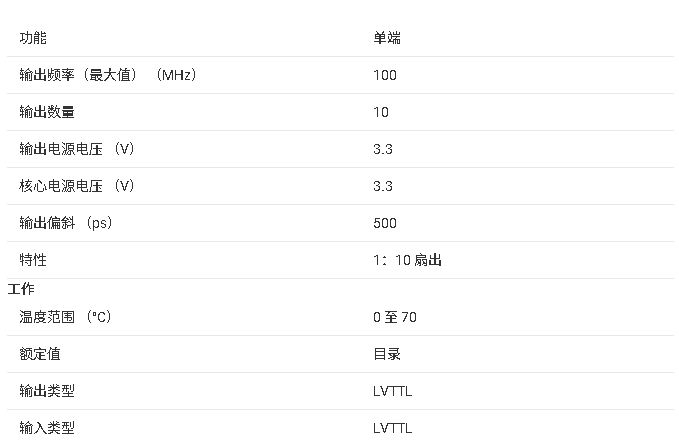

CDC351 是一款高性能时钟驱动器电路,可将 1 个输入 (A) 分配到 10 个输出 (Y),时钟分配偏斜最小。输出使能 (OE) 输入将输出禁用到高阻抗状态。CDC351 的工作电压为标称电压为 3.3V CC .

传播延迟在工厂使用 P0 和 P1 引脚进行调整。工厂调整可确保零件到零件的偏斜最小化,并保持在指定的窗口内。引脚 P0 和 P1 不适合客户使用,应连接到 GND。

*附件:cdc351.pdf

特性

- 低输出偏斜、低脉冲偏移,适用于时钟分配和时钟生成应用

- 工作电压为 3.3V V

CC - LVTTL兼容输入和输出

- 支持混合模式信号作(5V 输入和输出电压为 3.3V V

CC) - 将一个时钟输入分配到十个输出

- 分布式V

CC接地引脚可降低开关噪声 - 高驱动输出 (-32-mA I

哦, 32毫安 I老) - 最先进的 EPIC-IIB^TM的^BiCMOS设计显著降低功耗

- 封装选项包括塑料小外形 (DW) 和收缩小外形 (DB) 封装

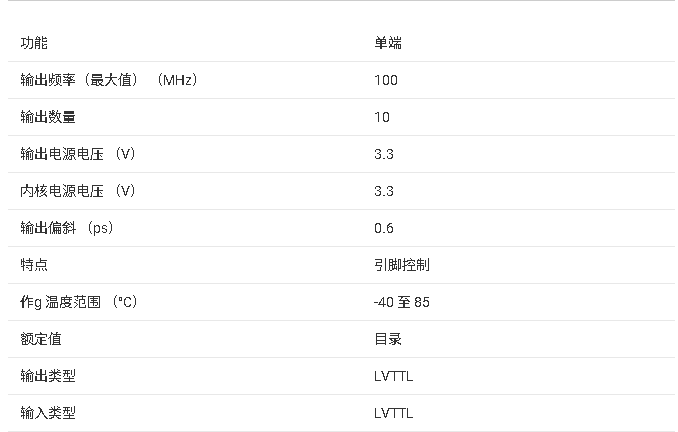

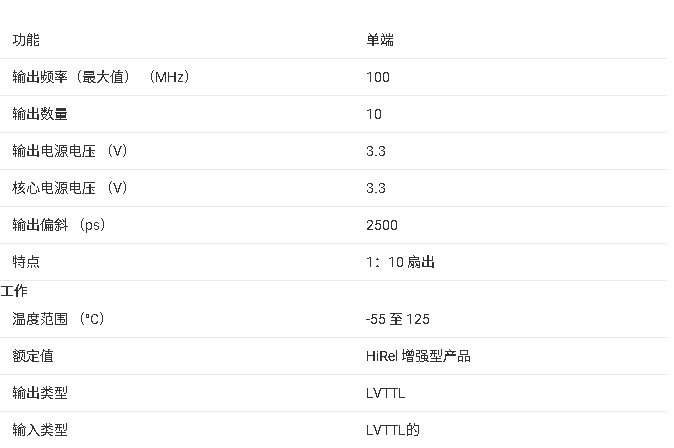

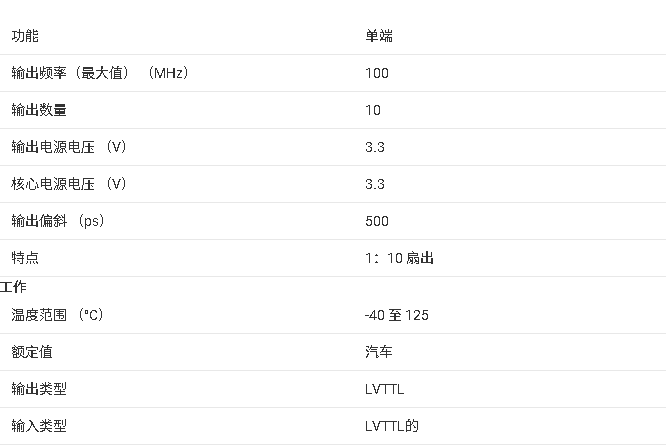

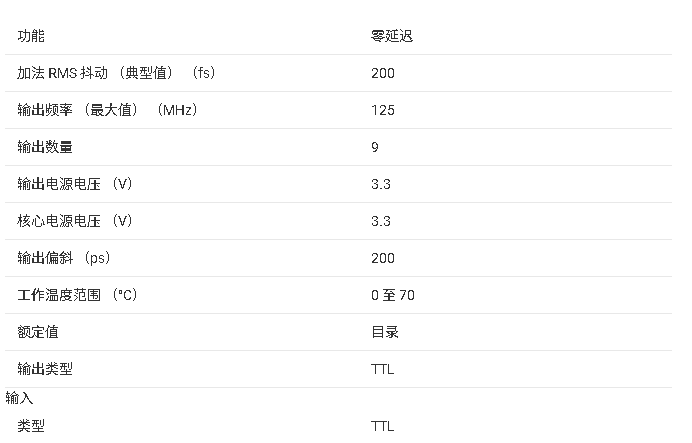

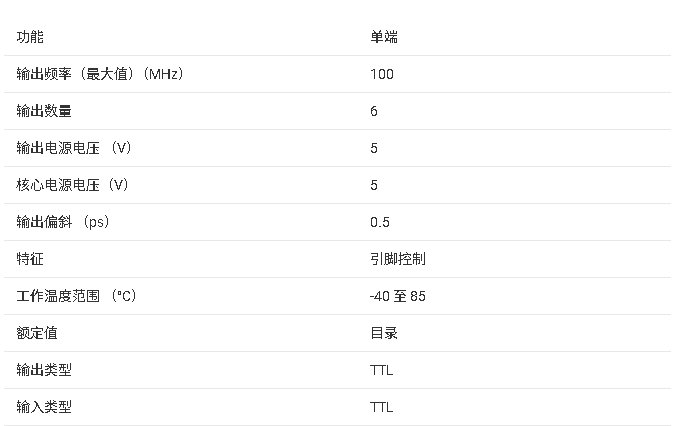

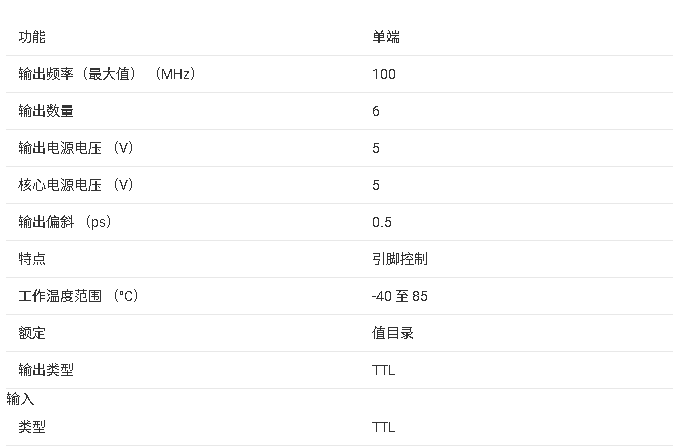

参数

1. 产品概述

- 型号:CDC351/CDC351I,3.3V供电的1输入转10输出时钟驱动器,支持三态输出。

- 核心功能:

- 将单路输入时钟(A)分配至10路低偏移输出(Y1-Y10),输出使能(OE)控制高阻态。

- 采用EPIC-IIB™ BiCMOS工艺,降低功耗,支持5V输入/输出与3.3V供电混合模式。

- 封装:24引脚SSOP(DB)或SOIC(DW),工作温度分商用级(0°C至70°C)和工业级(-40°C至85°C)。

2. 关键特性

- 低偏移设计:输出偏移(tsk(o))≤0.5ns,脉冲偏移(tsk(p))≤0.8ns,确保时钟同步性。

- 输出控制:通过OE引脚(高电平禁用)全局控制10路输出高阻态。

- 工厂校准:P0/P1引脚用于出厂调整传播延迟,用户需接地以保持性能。

- 电气性能:

- 工作电压:3.3V ±10%(3V至3.6V),最高时钟频率100MHz。

- 驱动能力:±32mA(高/低电平输出电流)。

3. 引脚与功能

- 关键引脚:

- A(6脚):输入时钟信号。

- OE(5脚):输出使能(高电平禁用)。

- Y1-Y10:10路输出,每路可驱动5个时钟负载。

- P0/P1(7/8脚):工厂校准引脚,用户需接地。

- 电源设计:分布式VCC/GND引脚(如3/10/14/22脚)减少开关噪声。

4. 性能参数

- 传播延迟:

- 典型值3.5ns(A→Y),使能/禁用延迟3.8-5.9ns(OE→Y)。

- 温度系数:≤65ps/10°C,电压系数:≤-140ps/100mV。

- 功耗:静态电流0.3mA(输出禁用),动态电流随频率线性增加。

5. 绝对最大额定值

- 电源电压:-0.5V至4.6V,输入电压:-0.5V至7V,超出可能损坏器件。

- 热阻:147°C/W(DB封装),101°C/W(DW封装)。

6. 封装与订购信息

- 封装选项:

- SSOP(DB):卷带封装(CDC351DBR)或管装(CDC351DB)。

- SOIC(DW):卷带封装(CDC351DWR)或管装(CDC351DW)。

- 环保认证:符合RoHS标准,引脚镀层为无铅镍钯金(NiPdAu)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

输出电压

+关注

关注

2文章

2037浏览量

40780 -

引脚

+关注

关注

16文章

2091浏览量

55140 -

GND

+关注

关注

2文章

548浏览量

41143 -

时钟驱动器

+关注

关注

0文章

96浏览量

14345

发布评论请先 登录

相关推荐

热点推荐

CDC2351-EP 1线至10线时钟驱动器技术文档总结

CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到 10 个输出 (Y),时钟分配的偏斜最小。输出使能 (OE)\ 输入将输出禁用到高阻抗状态。每个输出都有一个内部

CDC2351-Q1 1:10时钟驱动器技术文档总结

该CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到十个输出 (Y),时钟分配的偏斜最小。输出使能 (OE\) 输入将输出禁用为高阻抗状态。每个输出都有一个内部串联阻尼电阻,以提高负载的信号完整性。该

CDC509 3.3V相位锁定环时钟驱动器技术文档总结

CDC509 是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用 PLL 在频率和相位上将反馈 (FBOUT) 输出精确对齐到时钟 (CLK) 输入信号。它专为与同步 DRAM 一起使用而设计。

CDC516 3.3V相位锁定环时钟驱动器技术文档总结

CDC516 是一款高性能、低偏斜、低抖动、锁相环时钟驱动器。它使用锁相环 (PLL) 将反馈输出 (FBOUT) 与时钟 (CLK) 输入信号在频率和相位上精确对齐。它专为与同步 DRAM 一起使用而设计。

CDC208 双路1线至4线时钟驱动器技术文档总结

CDC208包含双时钟驱动器电路,可将一个输入信号扇出到四个输出,时钟分配的偏斜最小(见图2)。该器件还为每个电路提供两个输出使能(OE1\和OE2\)输入,可以强制将输出禁用到高阻抗

CDC341 1线至8线时钟驱动器技术文档总结

CDC341 是一款高性能时钟驱动器电路,可将一 (A) 输入信号分配到八 (Y) 输出,时钟分配偏移最小。通过使用控制引脚(1G 和 2G),无论 A 输入如何,输出都可以置于低电平

CDC340 1线至8线时钟驱动器技术文档总结

CDC340 是一款高性能时钟驱动器电路,可将一 (A) 输入信号分配给八 (Y) 输出,时钟分配偏斜最小。通过使用控制引脚(1G 和 2G),无论 A 输入如何,输出都可以置于高电平

CDC328A 时钟驱动器技术文档总结

该CDC328A包含一个时钟驱动器电路,该电路分配一个 输入信号到六个输出,时钟分配的偏差最小。 通过使用极性控制输入 (T\/C),各种 可以获得真实输出和互补输出的组合。

CDC329A 时钟驱动器技术文档总结

该CDC329A包含一个时钟驱动器电路,该电路将一个输入信号分配到六个输出,时钟分配的偏斜最小。通过使用极性控制输入(T\/C),可以获得真输出和互补输出的各种组合。

该CDC3

CDC391 时钟驱动器技术文档总结

CDC391 包含一个时钟驱动器电路,该电路分配一个 输入信号到六个输出,时钟分配的偏差最小。 通过使用极性控制 (T\/C) 输入,各种 可以获得真实输出和互补输出的组合。这 output-enable 输入为 用于将输出禁

CDC2536 锁相环时钟驱动器技术文档总结

CDC2536是一款高性能、低偏斜、低抖动的时钟驱动器。它使用锁相环 (PLL) 将时钟输出信号在频率和相位上精确对齐到时钟输入 (CLKIN) 信号。它专门设计用于同步 DRAM 和

CDC2351 1线转10线时钟驱动器技术文档总结

该CDC2351是一种高性能时钟驱动器电路,可将一个输入 (A) 分配到十个输出 (Y),时钟分配的偏斜最小。输出使能 (OE\) 输入将输出禁用为高阻抗状态。每个输出都有一个内部串联阻尼电阻,以提高负载的信号完整性。该

CDC351 1:10时钟驱动器技术文档总结

CDC351 1:10时钟驱动器技术文档总结

评论