前言

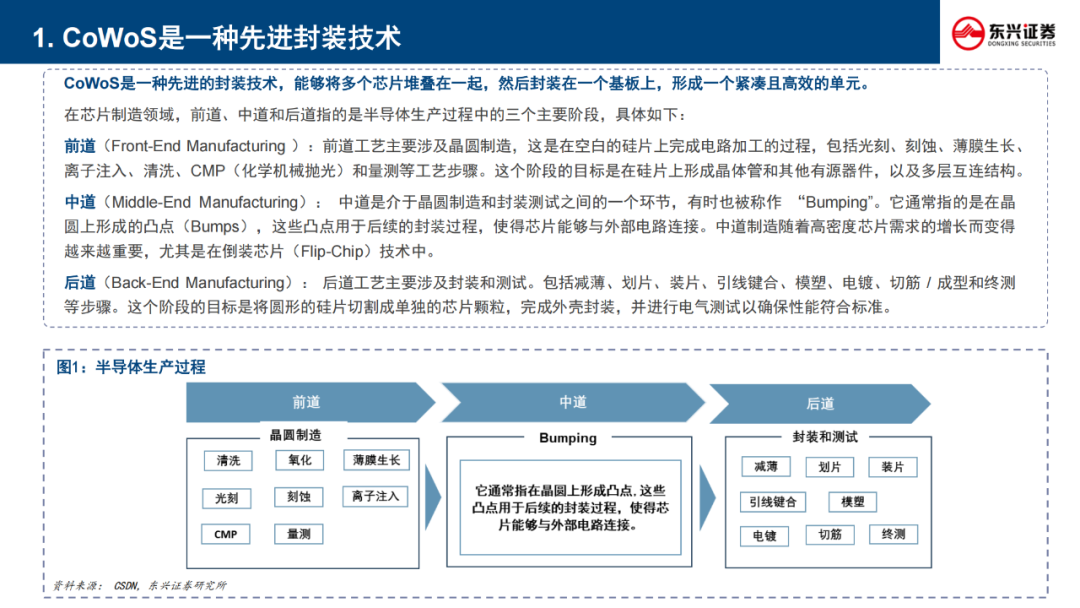

一、CoWoS 技术概述

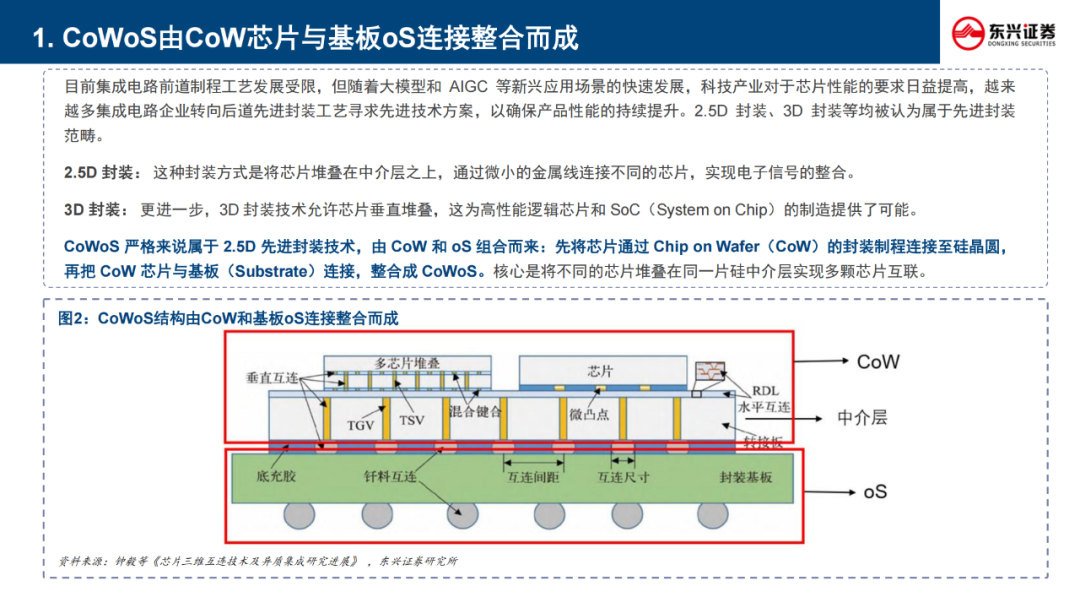

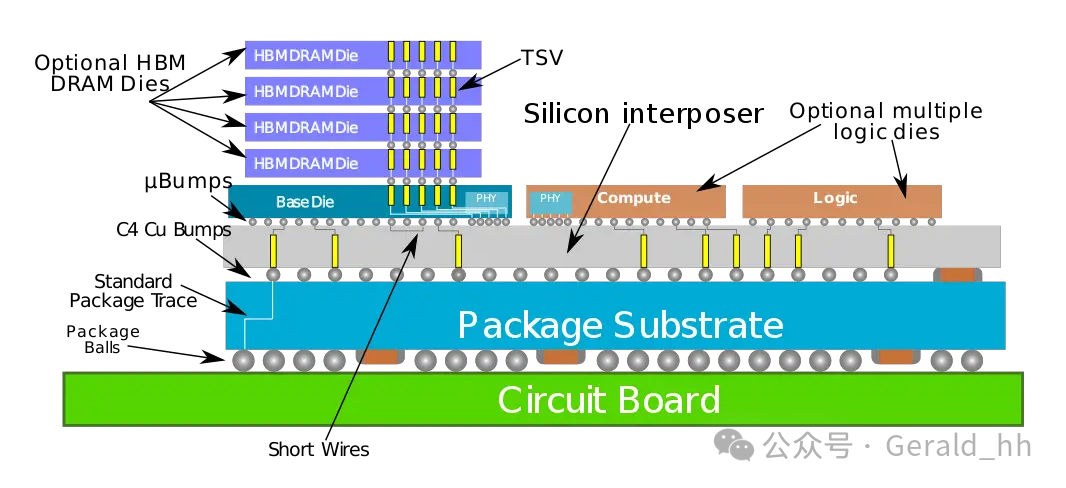

定义与结构:CoWoS(Chip on Wafer on Substrate)是一种 2.5D 先进封装技术,由 Chip on Wafer(CoW)和基板(Substrate)连接整合而成。其核心在于将不同芯片堆叠在同一硅中介层上,实现多芯片互联,从而提高芯片的集成度和性能。

发展历程:

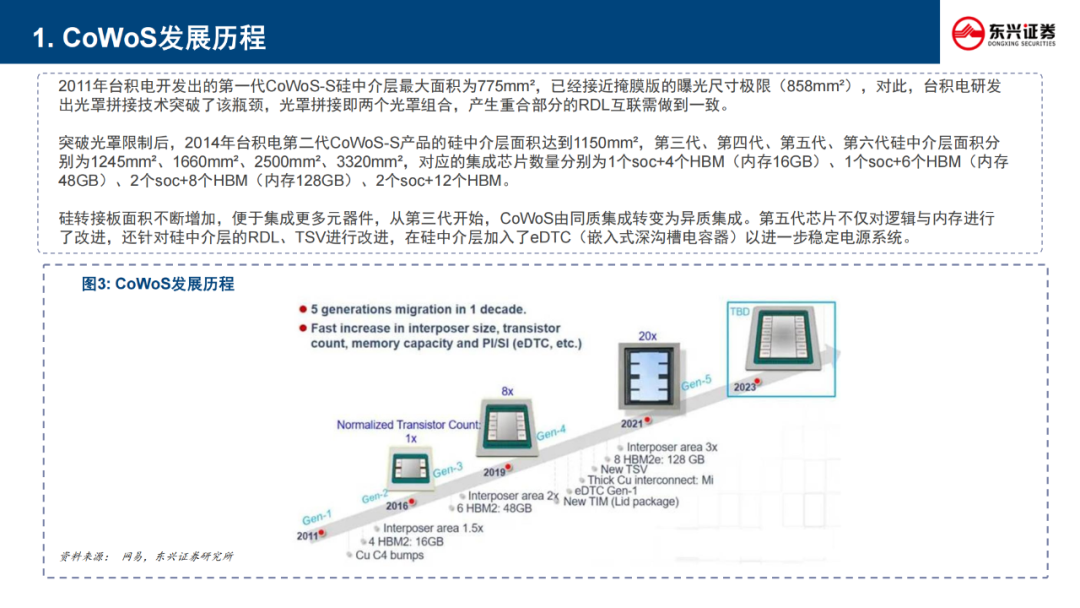

2011 年:台积电开发出第一代 CoWoS-S,硅中介层最大面积为 775mm²,接近掩膜版曝光尺寸极限(858mm²)。

2014 年:第二代 CoWoS-S 硅中介层面积达到 1150mm²。

后续迭代:第三代至第六代硅中介层面积分别为 1245mm²、1660mm²、2500mm²、3320mm²,集成芯片数量从 1 个 SoC + 4 个 HBM(内存 16GB)增至 2 个 SoC + 12 个 HBM(内存 128GB)。

技术分类:

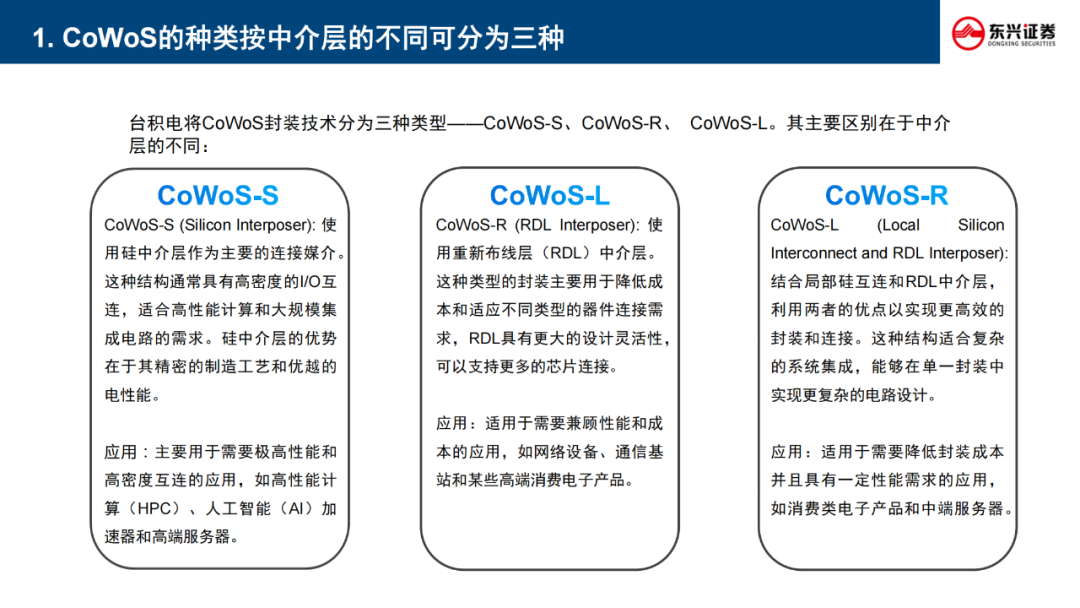

CoWoS-S(Silicon Interposer):使用硅中介层,具有高密度 I/O 互连,适用于高性能计算(HPC)、人工智能(AI)加速器和高端服务器。

CoWoS-R(RDL Interposer):使用重新布线层(RDL)中介层,具有更大的设计灵活性,适用于网络设备、通信基站等。

CoWoS-L(Local Silicon Interconnect and RDL Interposer):结合局部硅互连和 RDL 中介层,适合复杂的系统集成,如消费类电子产品和中端服务器。

二、CoWoS 的优势与挑战

优势:

高度集成:多个芯片可在同一封装内实现高度集成,满足空间效率要求高的行业需求,如互联网、5G 和人工智能。

高速和高可靠性:芯片与晶圆直接相连,提高信号传输速度和可靠性,缩短信号传输距离,减少传输时延和能量损失,适用于高性能计算和数据密集型应用。

高性价比:简化封装步骤,降低制造和封装成本,提高生产效率,相比传统封装技术具有更高的成本效益。

挑战:

信号完整性:逻辑晶圆到基板的互连在高数据速率下,由于 TSV 的寄生电容和电感,互连的信号传输会变差,需优化 TSV 设计。

电源完整性:CoWoS 封装通常用于高性能应用,数据切换率高、工作电压低,容易受到电源完整性挑战,如电源噪声和电压波动。

制造复杂性:作为 2.5D/3D 集成技术,制造过程复杂,涉及多个芯片的精确对准和连接,导致芯片成本增加。

集成和良率挑战:2.5D 和 3D 集成电路测试复杂,每个晶圆芯片在安装到中介层之前需要单独测试,安装后还需再次测试,硅通孔(TSV)也需要测试,大型硅中介层易受制造缺陷影响,导致产量损失。

电气挑战:

散热挑战:中介层和基板之间的热膨胀系数(CTE)不同,易产生散热问题,导致芯片温度过高,影响性能和可靠性。使用有机中介层和底部填充材料可在一定程度上缓解散热问题。

三、产业市场现状

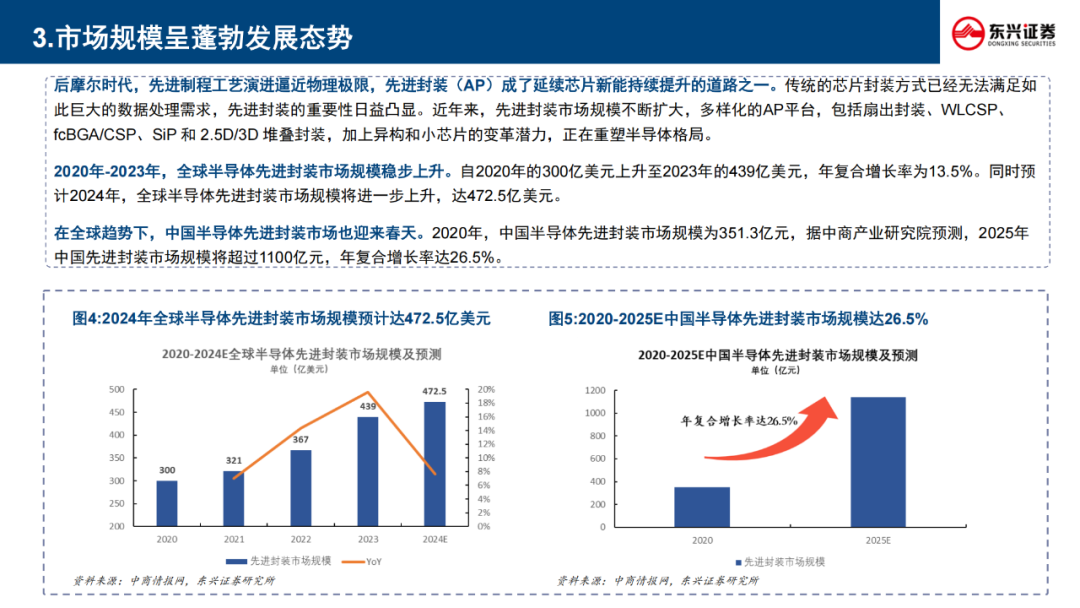

市场规模增长:

全球市场:2020 年全球半导体先进封装市场规模为 300 亿美元,2023 年上升至 439 亿美元,年复合增长率为 13.5%。预计 2024 年将进一步上升至 472.5 亿美元。

中国市场:2020 年中国半导体先进封装市场规模为 351.3 亿元,预计 2025 年将超过 1100 亿元,年复合增长率为 26.5%。

CoWoS 需求上升:

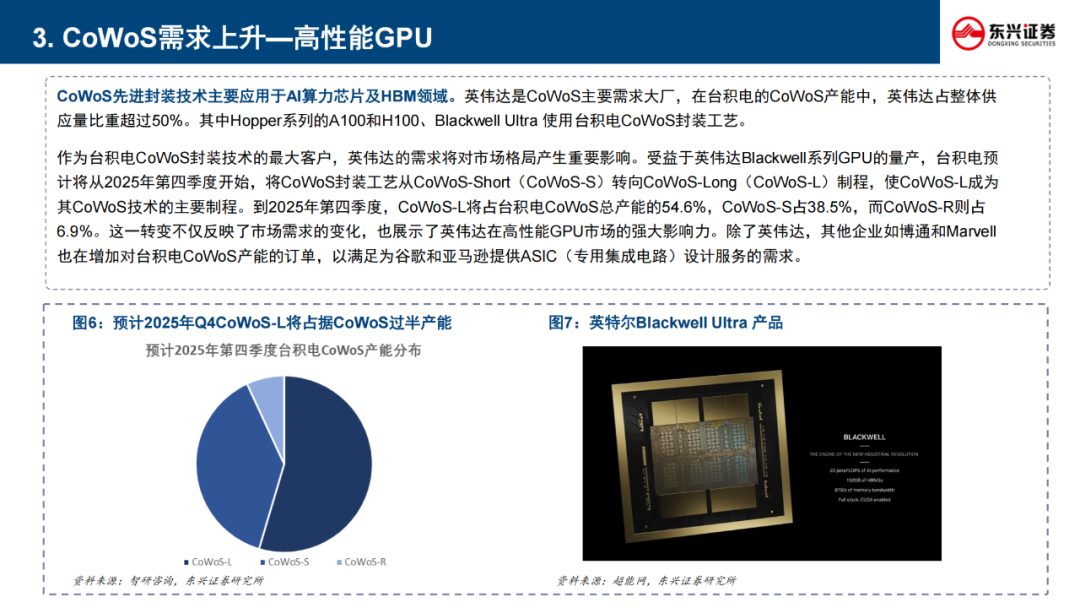

高性能 GPU:CoWoS 主要应用于 AI 算力芯片及 HBM 领域。英伟达是主要需求大厂,在台积电的 CoWoS 产能中占比超过 50%。受益于英伟达 Blackwell 系列 GPU 量产,台积电预计从 2025 年第四季度开始,将 CoWoS 封装工艺从 CoWoS-S 转向 CoWoS-L 制程,使 CoWoS-L 成为其 CoWoS 技术的主要制程。到 2025 年第四季度,CoWoS-L 将占台积电 CoWoS 总产能的 54.6%,CoWoS-S 占 38.5%,CoWoS-R 占 6.9%。

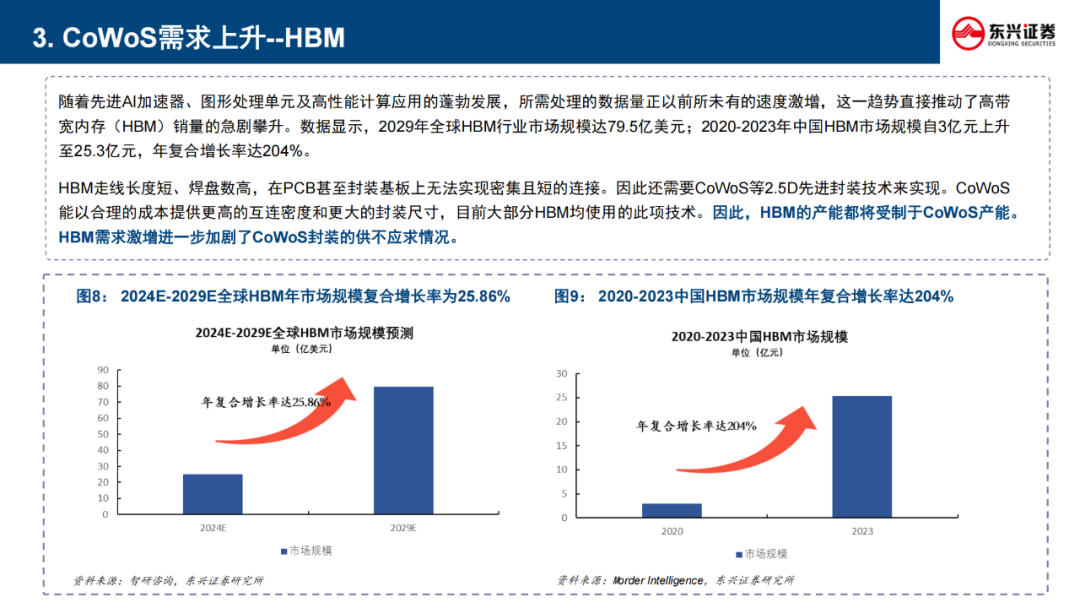

HBM:随着 AI 加速器、图形处理单元及高性能计算应用的蓬勃发展,HBM 销量急剧攀升。2029 年全球 HBM 行业市场规模预计达 79.5 亿美元;2020 - 2023 年中国 HBM 市场规模自 3 亿元上升至 25.3 亿元,年复合增长率为 204%。HBM 需要 CoWoS 等 2.5D 先进封装技术实现,其产能受 CoWoS 产能制约,需求激增加剧了 CoWoS 封装供不应求情况。

四、中国大陆主要参与企业

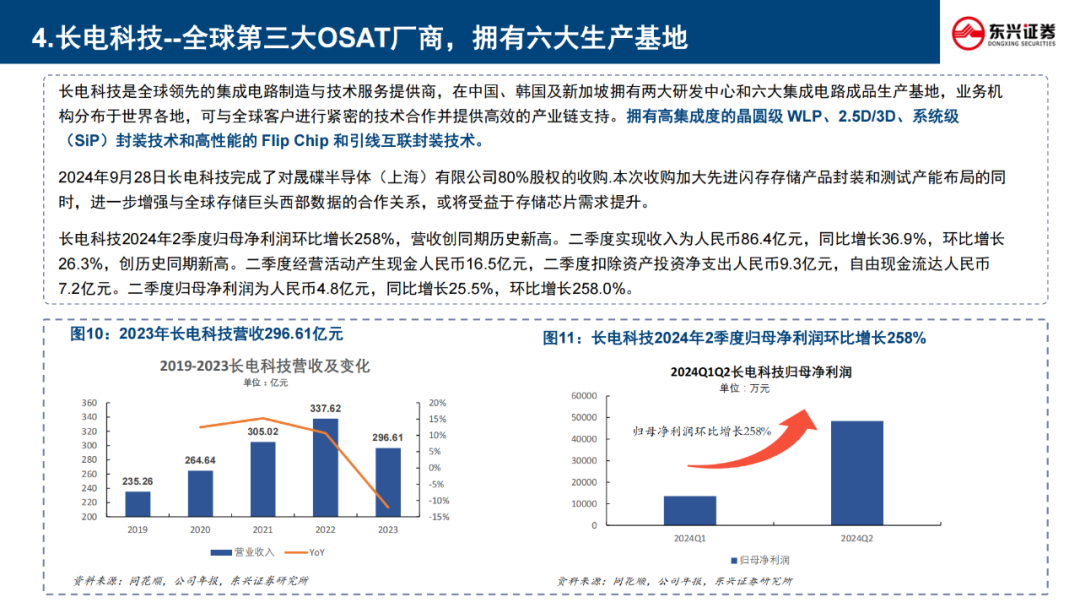

长电科技:

技术优势:拥有高集成度的晶圆级 WLP、2.5D/3D、系统级(SiP)封装技术和高性能的 Flip Chip 和引线互联封装技术。

市场表现:2024 年 9 月 28 日完成对晟碟半导体(上海)有限公司 80% 股权的收购,增强与全球存储巨头西部数据的合作关系,受益于存储芯片需求提升。2024 年 2 季度归母净利润环比增长 258%,营收创同期历史新高,实现收入为人民币 86.4 亿元,同比增长 36.9%,环比增长 26.3%。

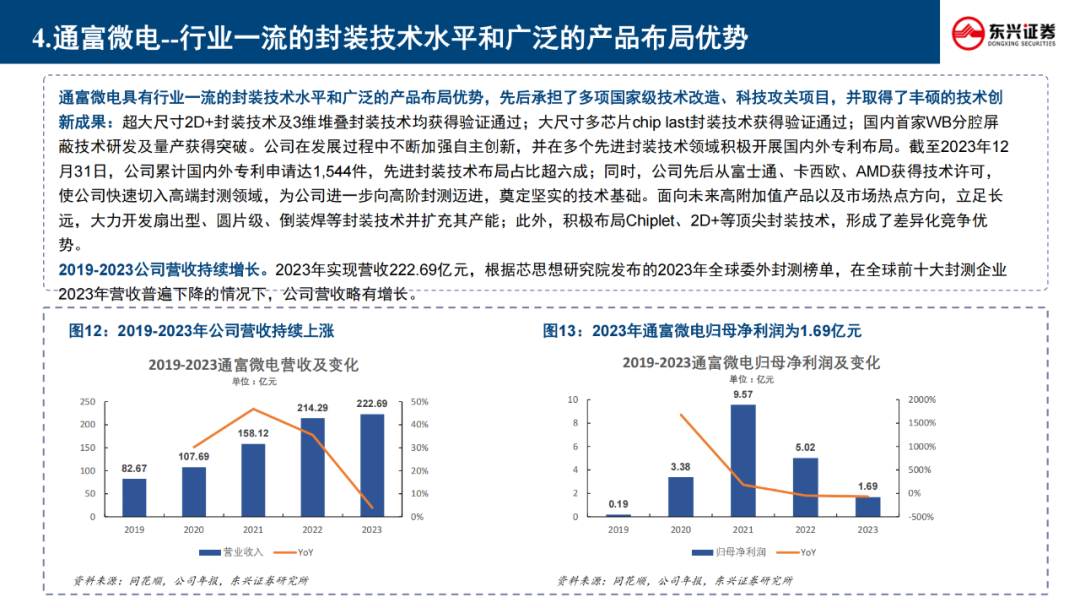

通富微电:

技术优势:超大尺寸 2D + 封装技术及 3 维堆叠封装技术均获得验证通过,大尺寸多芯片 chip last 封装技术获得验证通过,国内首家 WB 分腔屏蔽技术研发及量产获得突破。

市场表现:2019 - 2023 年公司营收持续增长,2023 年实现营收 222.69 亿元,归母净利润为 1.69 亿元。

华天科技:

技术优势:已掌握 SiP、FC、TSV、Bumping、Fan-Out、WLP、3D 等集成电路先进封装技术,推进 FOPLP 封装工艺开发和 2.5D 工艺验证,具备 3D NAND Flash 32 层超薄芯片堆叠封装能力。

市场表现:2024 年前三季度实现营收预计 105.31 亿元,同比增长 30.52%。2019 - 2023 年研发投入持续增长,分别为 4.02、4.62、6.5、7.08、6.94 亿元。

五、CoWoS 技术发展趋势

CoWoS-L 成为主流:CoWoS-L 结合了 CoWoS-S 和 InFO 技术的优点,使用中介层与 LSI 芯片进行芯片间互连,并用 RDL 层进行功率和信号传输,提供最灵活集成。其中介层包括多个局部硅互连(local silicon interconnect,LSI)芯片和全局重布线(global redistribution layers),形成一个重组的中介层(reconstituted interposer,RI),以替代 CoWoS-S 中的单片硅中介层。LSI 芯片保留了硅中介层的所有优秀特性,包括保留亚微米铜互连、硅通孔(TSV)和嵌入式深沟槽电容器(eDTC),以确保良好的系统性能,同时避免了单个大型硅中介层的良率损失问题。在电气性能方面,CoWoS 平台引入第一代深沟槽电容器(eDTC)提升电气性能,配备第一代 eDTC 的 CoWoS 可以将系统电源分配网络(PDN)的阻抗降低 93%,压降比没有使用 eDTC 的情况低 72%。此外,HBM VDDQ 的同步开关噪声(SSN)可以在 3.2 GHz 时比没有 eDTC 的情况减少到 38%,信号完整性也可以得到改善。新一代的 eDTC 可以提供 1100 nF/mm² 的电容密度,高电容密度为高速计算的电源效率提供了巨大的优势。出于良率考虑,单个硅芯片上 eDTC 的最大面积上限约为 300 平方毫米。通过连接所有 LSI 芯片的电容,CoWoS-L 搭载多个 LSI 芯片,可以显著增加 RI 上的总 eDTC 电容。

-

CoWoS

+关注

关注

0文章

170浏览量

11536 -

先进封装

+关注

关注

2文章

562浏览量

1062

原文标题:新技术前瞻专题系列(七):先进封装行业:CoWoS五问五答

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

十五五开局,磁性元件行业企业要怎么走

【深度报告】CoWoS封装的中阶层是关键——SiC材料

AI芯片发展关键痛点就是:CoWoS封装散热

CoWoS产能狂飙下的隐忧:当封装“量变”遭遇检测“质控”瓶颈

先进封装市场迎来EMIB与CoWoS的格局之争

南方测绘亮相2025迪拜国际五大行业展览会

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

五金冲压行业mes系统解决方案:实现高效生产与智能管理的利器

HBM技术在CowoS封装中的应用

CoWoP能否挑战CoWoS的霸主地位

从InFO-MS到InFO_SoW的先进封装技术

五路有源功率分配器 skyworksinc

先进封装行业:CoWoS五问五答

先进封装行业:CoWoS五问五答

评论