编辑语

集成电路占用面积的不断缩小,正在将性能限制,从晶体管本身转移到晶体管之间的互连工艺。互连的电阻-电容延迟,随着器件密度的增加而恶化,因为互连路径变长,导线变窄,并且随着新材料集成到电路中,需要更多类型的连接。这一综述,通过关注材料的载流子平均自由程和内聚能,回顾了开发更好互连的策略。

摘 要

在芯片上集成更多器件的半导体技术,目前达到了器件单独缩放,已经不再是提高器件性能的有效方式。问题在于连接晶体管的互连工艺,随着尺寸按比例缩小以匹配晶体管尺寸,金属的电阻率呈指数增加。

因此,总信号处理延迟,主要是来自互连的电阻-电容resistance-capacitance (RC)延迟,而不是来自晶体管开关速度的延迟。这一技术瓶颈,需要探索替代材料和颠覆性器件结构。

近日,韩国三星电子综合技术院(Samsung Advanced Institute of Technology)Joon-Seok Kim,Jeehwan Kim,Sang Won Kim等,在Science上发表综述文章,从材料和器件两个方面,提出了互连技术中,RC电阻-电容延迟的提升策略。

Addressing interconnect challenges for enhanced computing performance.

解决互连难题,以增强计算性能。

互连电阻-电容resistance-capacitance ,RC延迟是器件性能的瓶颈。

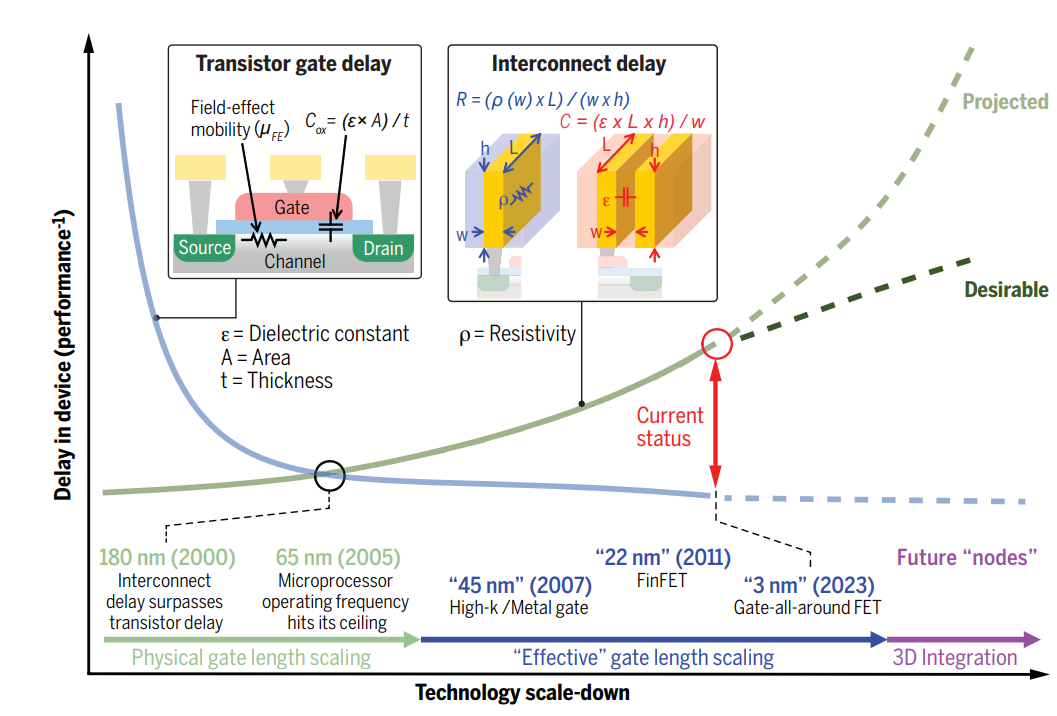

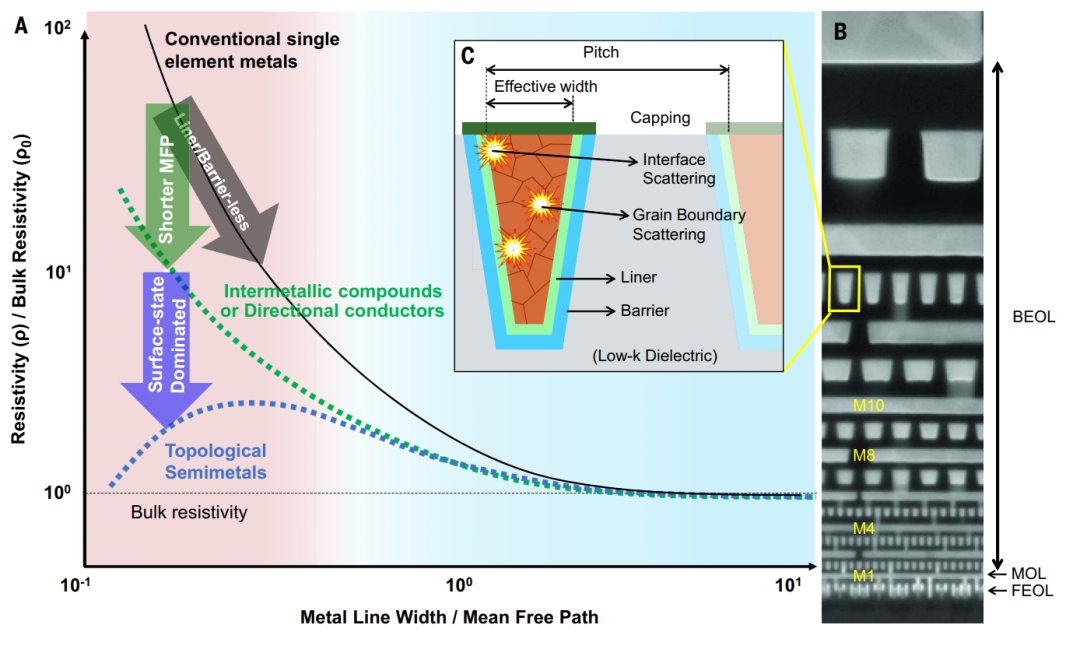

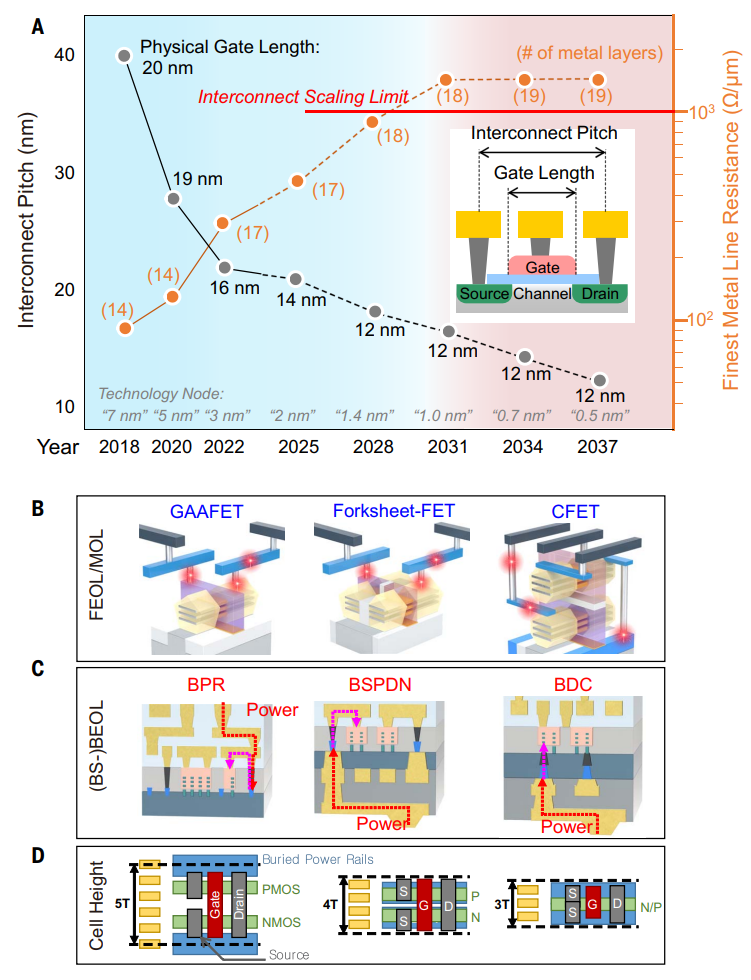

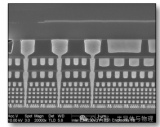

图1. 电阻率增加的原因。

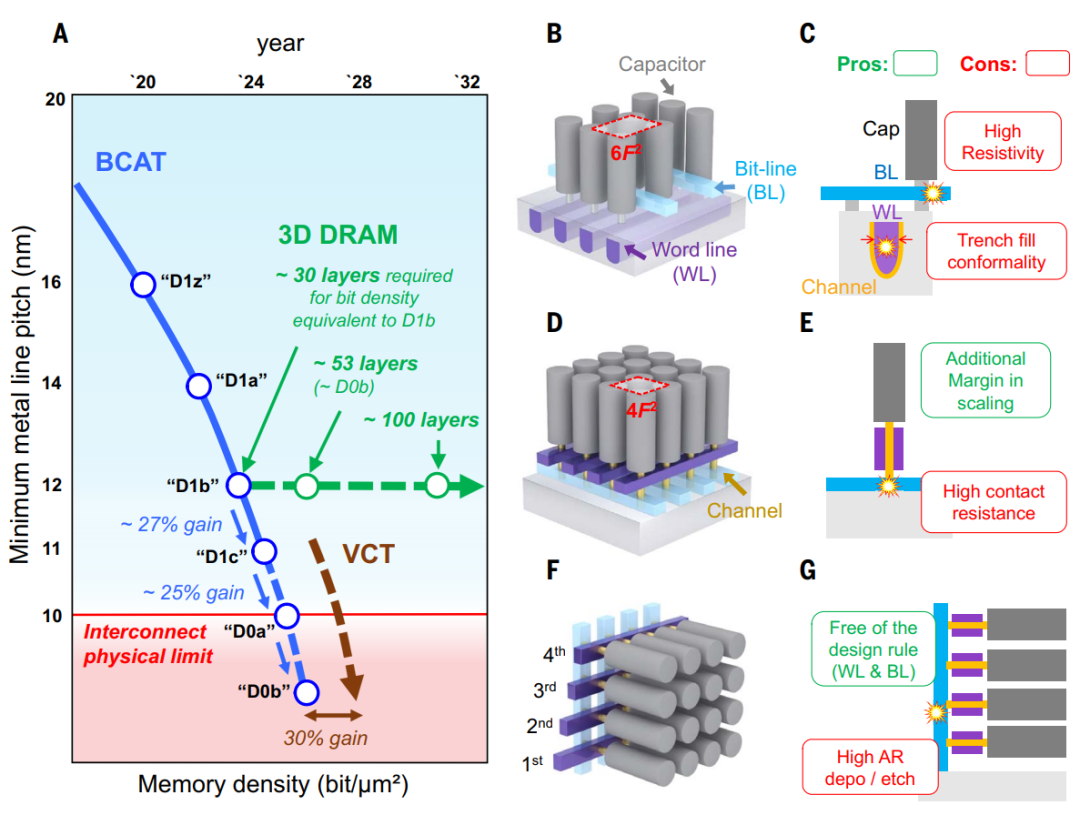

图2. DRAM架构结构变化的扩展挑战和进展。

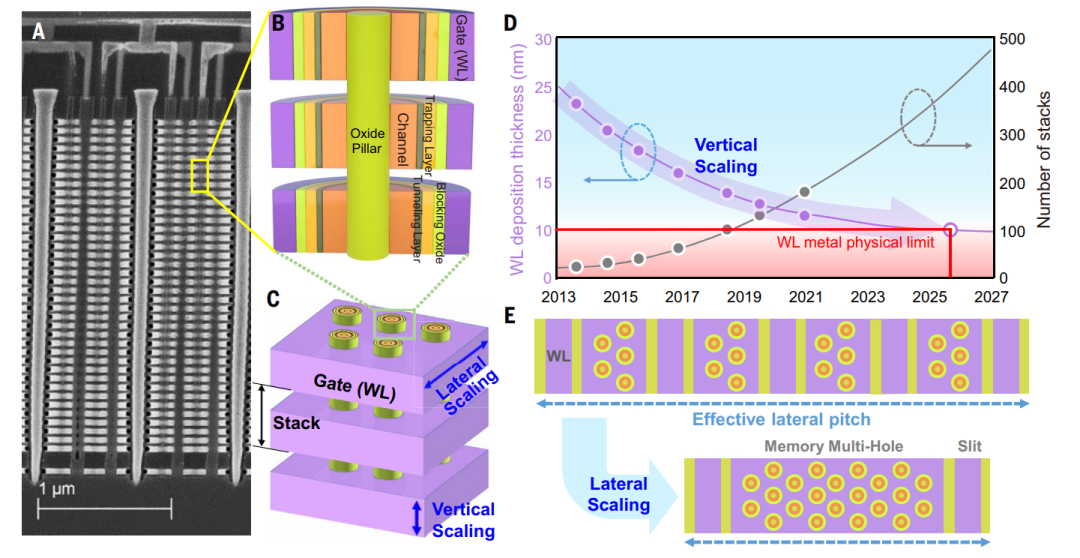

图3. NAND闪存的扩展挑战。

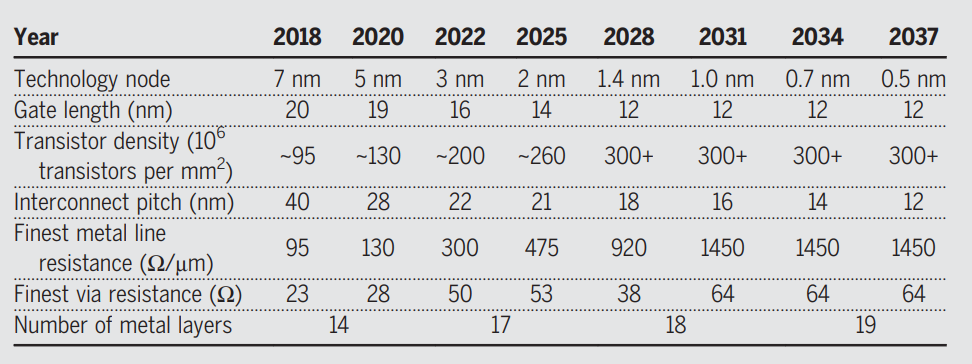

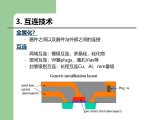

图4. 逻辑器件的互连缩放和结构挑战。

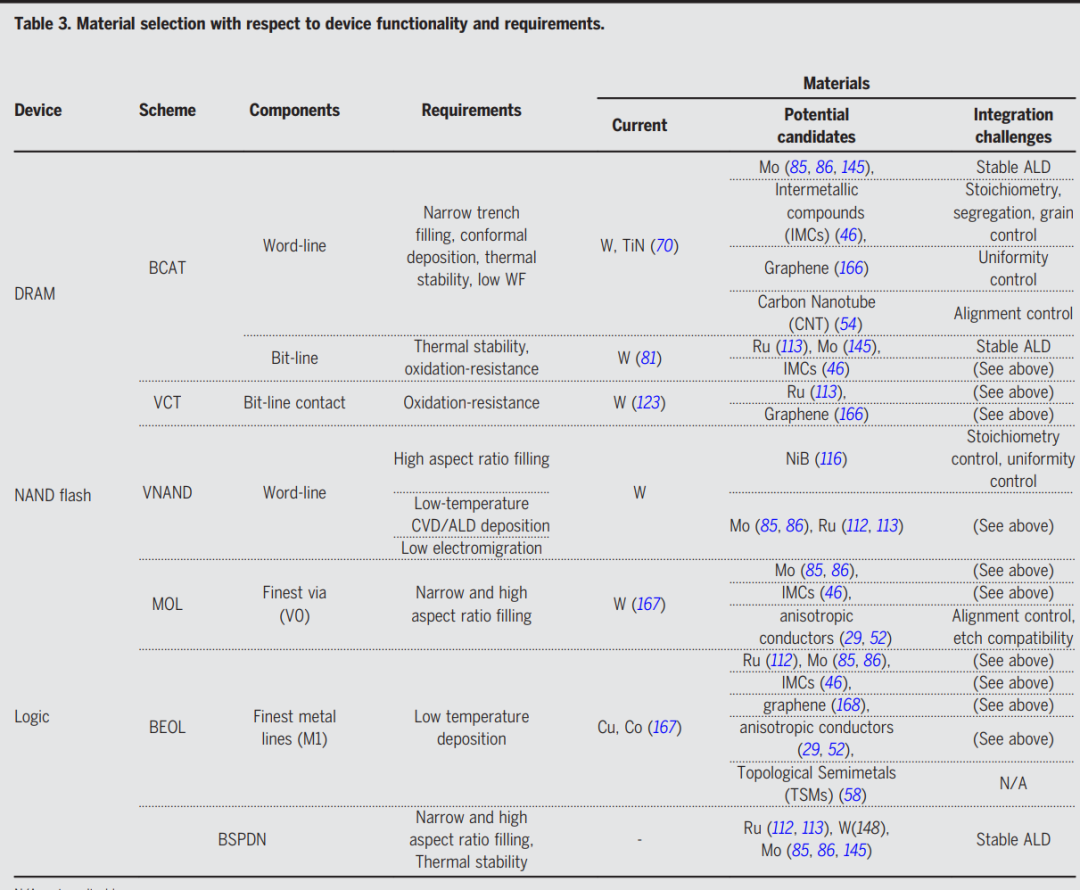

表2. 逻辑互连规范及其对技术节点的预测和要求。

研究进展

晶体管栅极延迟,取决晶体管栅极氧化物电容和沟道载流子迁移率,而互连RC延迟,则取决于金属线电阻和电容决定。据报道,互连RC延迟已超过约180-nm节点时代的晶体管栅极延迟,并具有65-nm节点时代所能达到工作频率上限。物理缩放之外的有效器件缩放方案,即高k/金属栅极的引入和沟道结构的改变,增加了晶体管的密度,并提高晶体管的开关速度,但也导致互连RC延迟呈指数增长。随着最近引入的垂直堆叠多个芯片策略,互连RC延迟,预计将以更快的速度增加,并对指数增长的计算需求,造成更严重的瓶颈。

晶体管和存储单元的横向按比例缩小,迫使互连也按比例缩小到这样的尺寸,其中导体的表面和晶界决定着电子散射,并导致电阻率的指数增加。未来互连的理想候选材料,应具有较短的平均自由程,从而使散射表现出较小的缩放效应,不需要衬层和势垒层,并且具有表面态主导的导电性。就存储器和逻辑器件的结构变化而言,由于朝着垂直集成结构的发展,以使面密度最大化,制造变得更具挑战性。未来互连材料的研究,还应考虑兼容于最近开发的制造工艺。

在这篇综述中,讨论了当前互连技术的材料和器件挑战,并讨论了学术界和工业界未来研究的潜在方向。介绍了用于确定互连应用的合适材料,并评估其基本特性的方法,介绍了各种半导体器件中提出的结构进步,并建议基于器件功能和制造工艺的材料。最后,对半导体三维集成日益增长的重要性,提出了前瞻性的展望。

展望未来

用于互连的互补金属氧化物半导体complementary metal-oxide semiconductor (CMOS)兼容导电材料的研究,业界通常是去优先化的,主要重点是提高半导体性能和增强高k电介质。这已经导致互连材料开发受挫,并且相比于半导体技术的其他方面,也受到较少的关注。在学术研究中,互连研究,通常强调选择材料特性,而没有全面考虑在实际器件架构中的适用性。为了解决这一关键差距,需要一种系统和协作的研究方法,建立一个强大的平台,用于发现、合成、表征和实际验证与下一代半导体技术兼容的互连材料。学术界和工业界之间这种共同努力,将促进互连解决方案的可行性开发,这些解决方案不仅在理论上很有前景,而且在功能与新兴电子设备的苛刻性能和集成要求兼容。

文献链接

Joon-Seok Kim et al. , Addressing interconnect challenges for enhanced computing performance. Science 386, eadk 6189 (2024)。

DOI:10.1126/science.adk6189

https://www.science.org/doi/10.1126/science.adk6189

本文译自Science。

-

芯片

+关注

关注

462文章

53535浏览量

459139 -

集成电路

+关注

关注

5446文章

12467浏览量

372687 -

半导体

+关注

关注

336文章

29985浏览量

258280

原文标题:研究透视:芯片-互连材料 | Science

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于硅基异构集成的BGA互连可靠性研究

基于碳纳米材料的TPU导电长丝制备与性能研究

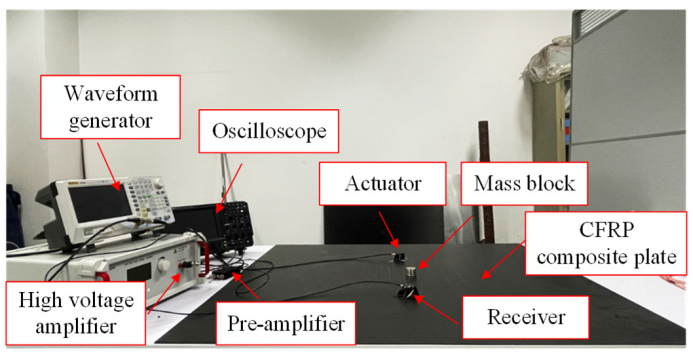

高压放大器在材料领域的研究与应用

XSR芯片间互连技术的定义和优势

为什么芯片需要低介电常数材料

TSV硅通孔填充材料

Low-K材料在芯片中的作用

背接触(BC)太阳能电池组件封装损失研究:从材料选择到工艺优化

芯片互连技术深度解析:焊球、铜柱与微凸点的奥秘

研究透视:芯片-互连材料

研究透视:芯片-互连材料

评论