半导体行业长期秉持的摩尔定律(该定律规定芯片上的晶体管密度大约每两年应翻一番)越来越难以维持。缩小晶体管及其间互连的能力正遭遇一些基本的物理限制。特别是,当铜互连按比例缩小时,其电阻率急剧上升,这会减少它们可承载的信息量并增加能耗。 该行业一直在寻找替代的互连材料,以让摩尔定律的发展进程延续得更久一点。从很多方面来说,石墨烯是一个非常有吸引力的选择:这种薄片状的碳材料具有优异的导电性和导热性,并且比金刚石还坚硬。

然而,研究人员在将石墨烯纳入主流计算应用方面一直举步维艰,主要有两个原因。首先,沉积石墨烯需要高温,这与传统的互补金属氧化物半导体(CMOS)制造工艺不兼容。其次,未掺杂的宏观石墨烯片的载流子密度相对较低。

现在,位于美国加利福尼亚州米尔皮塔斯(Milpitas)的一家初创公司Destination 2D声称已经解决了这两个问题。Destination 2D的团队展示了一种在300°C的温度下将石墨烯互连沉积到芯片上的技术,这个温度足够低,能够通过传统的互补金属氧化物半导体(CMOS)技术来实现。他们还开发了一种掺杂石墨烯片的方法,据Destination 2D的联合创始人兼首席技术官Kaustav Banerjee称,这种方法可使电流密度达到铜的100倍。

“人们一直在尝试将石墨烯用于各种应用,但在主流微电子领域,也就是本质上的CMOS技术中,到目前为止人们还未能使用(石墨烯)。”Banerjee说道。

Destination 2D并非唯一一家致力于石墨烯互连技术的公司。台积电(TSMC)和三星(Samsung)也在努力使这项技术达到标准。然而,Banerjee声称,Destination 2D是唯一一家展示了直接在晶体管芯片顶部沉积石墨烯的公司,而不是先单独制备互连部件,然后再将其附着到芯片上。

低温沉积石墨烯

石墨烯于2004年首次被分离出来,当时研究人员用胶带从石墨块上剥离出石墨烯薄片。这种材料被认为非常有前景,以至于在2010年这一成果获得了诺贝尔奖。(诺贝尔奖共同获得者Konstantin Novoselov现在是Destination 2D的首席科学家)。

然而,用胶带小心地从铅笔芯上剥离石墨烯绝不是一种可大规模生产的方法。为了可靠地制造石墨烯结构,研究人员已经转向化学气相沉积法,即将碳气体沉积到受热的基底上。这通常需要的温度远高于CMOS制造中大约400°C的最高工作温度。

Destination 2D

Destination 2D使用了一种在加州大学圣巴巴拉分校Banerjee实验室开发的压力辅助直接沉积技术。Banerjee称这种技术为压力辅助固相扩散,它使用一种牺牲金属膜,如镍。牺牲膜被放置在晶体管芯片的顶部,碳源沉积在其上方。然后,使用大约410到550千帕(60到80磅每平方英寸)的压力,碳被迫穿过牺牲金属,并在下方重新结合成干净的多层石墨烯。然后简单地去除牺牲金属,将石墨烯留在芯片上进行排列。这项技术在300°C下工作,温度足够低,不会损坏下方的晶体管。

提高石墨烯的电流密度

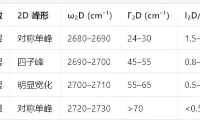

在石墨烯互连排列之后,对石墨烯层进行掺杂以降低电阻率并提高其载流能力。Destination 2D团队使用一种称为插层(intercalation)的掺杂技术,即将掺杂原子扩散到石墨烯片层之间。 掺杂原子可以有多种,例如氯化铁、溴和锂。一旦注入,掺杂剂就会向石墨烯片层提供电子(或者说材料中的对应物,电子空穴),从而实现更高的电流密度。“插层化学是一个非常古老的学科,”Banerjee说,“我们只是将这种插层技术应用到石墨烯中,这是一种创新。”

这项技术有一个很有前景的特点——与铜不同,随着石墨烯互连尺寸缩小,其载流能力会提高。这是因为对于更细的线路,插层技术变得更加有效。Banerjee认为,这将使他们的技术能够在未来支持多代半导体技术。

Destination 2D已经在芯片层面展示了他们的石墨烯互连技术,并且他们还开发了可在制造工厂中应用的晶圆级沉积工具。他们希望与代工厂合作,将他们的技术用于研发,并最终用于生产。

-

摩尔定律

+关注

关注

4文章

640浏览量

81154 -

石墨烯

+关注

关注

54文章

1615浏览量

85394

原文标题:石墨烯互连技术:延续摩尔定律的新希望

文章出处:【微信号:DT-Semiconductor,微信公众号:DT半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

用于氧化石墨烯的多模态表征与激光还原图案化的共聚焦显微技术

基于四点探针法测量石墨烯薄层电阻的IEC标准

高精度TLM测量技术:在金属-石墨烯接触电阻表征中的应用研究

石墨烯超低方阻的实现 | 霍尔效应模型验证

当摩尔定律 “踩刹车” ,三星 、AP、普迪飞共话半导体制造新变革新机遇

EastWave应用:光场与石墨烯和特异介质相互作用的研究

一文了解什么是石墨烯拉曼光谱表征技术

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

晶心科技:摩尔定律放缓,RISC-V在高性能计算的重要性突显

人工合成石墨片与天然石墨片的差别

电力电子中的“摩尔定律”(2)

跨越摩尔定律,新思科技掩膜方案凭何改写3nm以下芯片游戏规则

电力电子中的“摩尔定律”(1)

石墨烯互连技术:延续摩尔定律的新希望

石墨烯互连技术:延续摩尔定律的新希望

评论