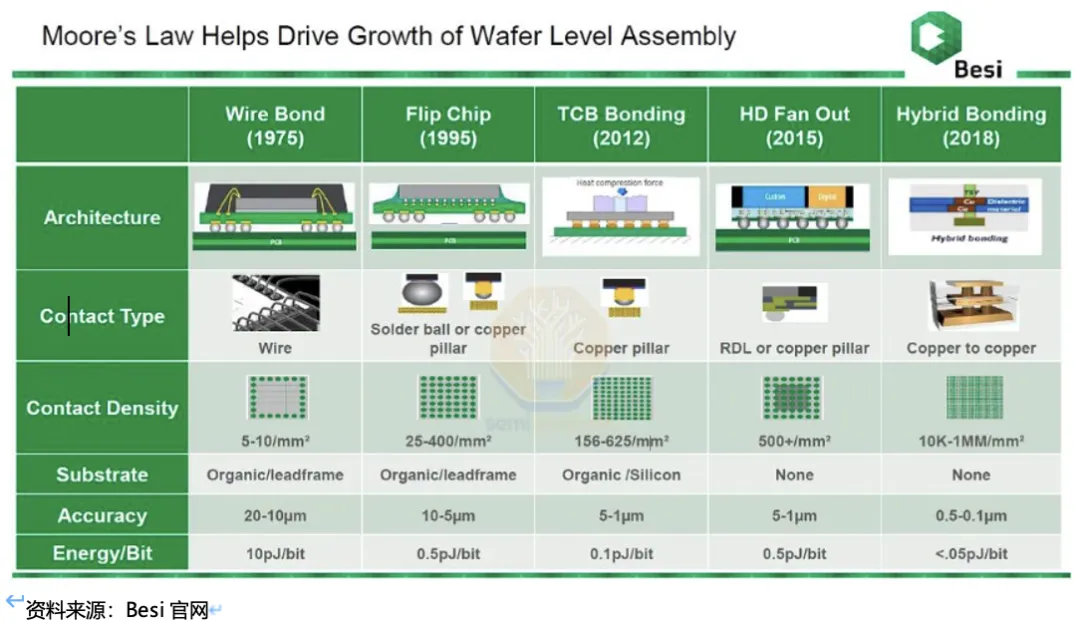

随着电子设备向小型化、高性能化发展,芯片封装技术也在不断演进。高密度芯片封装是满足现代电子产品需求的关键技术之一,而芯片互连技术作为封装的核心环节,经历了从焊球到铜柱再到微凸点的技术革新。本文将从高密度芯片封装的发展历程出发,解析焊球、铜柱及微凸点三种互连技术的定义、材料、制作工艺、适用范围、用途及典型案例,并将这些技术融入芯片封装发展的历史背景中,展现其在不同阶段的作用与意义。

芯片封装发展历程与互连技术的演进

1. 早期阶段:20世纪90年代——焊球技术的兴起

背景:随着集成电路(IC)复杂度的提升,传统的引线键合技术已无法满足高密度封装的需求。焊球技术(Ball Grid Array, BGA)应运而生,成为主流互连技术。BGA通过将焊球阵列排列在芯片底部,实现了更高的引脚密度和更短的信号传输路径。

焊球技术

·定义:通过将焊球排列成阵列形式,实现芯片与基板互连的技术。

·材料:通常采用锡铅(Sn-Pb)合金或无铅合金(如Sn-Ag-Cu)。

·制作工艺:在芯片底部制作焊盘,通过丝网印刷或电镀技术形成焊球,再通过回流焊实现连接。

意义:焊球技术解决了传统引线键合技术的引脚密度和信号传输瓶颈,推动了高密度封装的发展。

2. 中期阶段:20世纪90年代——铜柱技术的引入

背景:随着芯片尺寸的缩小和I/O数量的增加,焊球的尺寸和间距逐渐接近物理极限。铜柱技术(Copper Pillar)因其更高的机械强度和更小的间距优势,逐渐在高性能芯片封装中得到应用。

铜柱技术

·定义:通过铜柱实现芯片与基板互连的技术,具有更高的机械强度和更小的间距。

·材料:纯铜或铜合金,顶部涂覆锡银(Sn-Ag)合金。

·制作工艺:在芯片底部制作铜柱,通过热压焊将铜柱与基板连接。

·适用范围:高密度封装,适用于高性能计算、服务器等领域。

·典型案例:NVIDIA的高性能GPU封装、高端服务器处理器封装。

意义:铜柱技术进一步提升了封装密度和性能,满足了高性能计算和服务器领域的需求。

3. 现阶段:2010年代至今——微凸点技术的突破

背景:随着摩尔定律的延续,芯片特征尺寸进一步缩小,传统的焊球和铜柱技术已难以满足超高性能和超小尺寸封装的需求。微凸点技术(Micro Bump)通过更小的尺寸和更高的密度,成为3D封装和异构集成的主流选择。

微凸点技术

·定义:通过微米级凸点实现芯片与基板或芯片与芯片互连的技术。

·材料:锡银(Sn-Ag)合金或铜镍(Cu-Ni)合金。

·制作工艺:在芯片表面制作微凸点,通过热压焊或回流焊实现互连。

·适用范围:超高密度封装,适用于3D封装、异构集成等领域。

·典型案例:AMD的3D V-Cache技术、苹果M系列处理器的异构集成。

意义:微凸点技术推动了3D封装和异构集成的发展,为芯片性能的进一步提升提供了技术支持。

焊球、铜柱及微凸点技术对比

| 技术特性 | 焊球技术 | 铜柱技术 | 微凸点技术 |

| 定义 | 焊球阵列互连 | 铜柱互连 | 微米级凸点互连 |

| 材料 | Sn-Pb或Sn-Ag-Cu | 纯铜或铜合金 | Sn-Ag或Cu-Ni合金 |

| 制作工艺 | 丝网印刷、回流焊 | 电镀、热压焊 | 光刻、热压焊 |

| 适用范围 | 中等密度封装 | 高密度封装 | 超高密度封装 |

| 用途 | 芯片与基板互连 | 高性能芯片互连 | 3D封装、异构集成 |

| 典型案例 | Intel早期处理器 | NVIDIA GPU | AMD 3D V-Cache |

| 历史发展 | 1990年代兴起 | 2000年代引入 | 2010年代突破 |

| Pad节距 | 0.5 mm - 1.0 mm | 0.2 mm - 0.5 mm | 0.05 mm - 0.2 mm |

总结

焊球、铜柱及微凸点技术分别代表了芯片互连技术在不同发展阶段的核心突破。从20世纪90年代的焊球技术到21世纪初的铜柱技术,再到2010年代至今的微凸点技术,每一种技术都在特定的历史阶段解决了封装密度和性能的瓶颈问题,推动了芯片封装技术的不断演进。焊球技术适用于中等密度封装,Pad节距为0.5 mm - 1.0 mm;铜柱技术适用于高密度封装,Pad节距为0.2 mm - 0.5 mm;微凸点技术则适用于超高密度封装,Pad节距为0.05 mm - 0.2 mm。未来,随着3D封装和异构集成的进一步发展,微凸点技术将继续引领芯片互连技术的创新潮流,为电子设备的小型化和高性能化提供更强大的支持

-

芯片

+关注

关注

463文章

54432浏览量

469384 -

焊球

+关注

关注

0文章

11浏览量

6217

原文标题:芯片互连技术解析:焊球、铜柱及微凸点

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

激光微植球赋能光通信:超窄间距凸块的微加工突破

从手工到自动:焊球剪切测试的技术演进与科学原理

晶圆级封装(WLP)中Bump凸点工艺:4大实现方式的技术细节与场景适配

LTCC焊球可靠性提升方案:推拉力测试仪的测试标准与失效诊断

芯片互连技术深度解析:焊球、铜柱与微凸点的奥秘

芯片互连技术深度解析:焊球、铜柱与微凸点的奥秘

评论