文章来源:半导体与物理

原文作者:jjfly686

在现代芯片中,数十亿晶体管通过金属互连线连接成复杂电路。随着制程进入纳米级,一个看似“隐形”的问题逐渐浮出水面:金属线之间的电容耦合。这种耦合不仅会拖慢信号传输速度,甚至可能引发数据传输错误。而解决这一问题的关键,正是低介电常数(Low-k)材料。

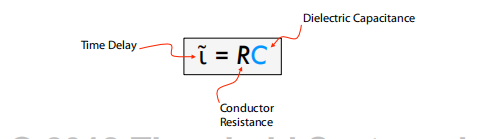

互连延迟

在22纳米制程节点,科学家发现了一个颠覆认知的现象:互连延迟(信号在金属线中的传输延迟)达到了晶体管门延迟的20倍。这意味着,即使晶体管开关速度再快,信号在金属线中的“堵车”也会严重拖累整体性能。

为什么会有如此大的延迟?

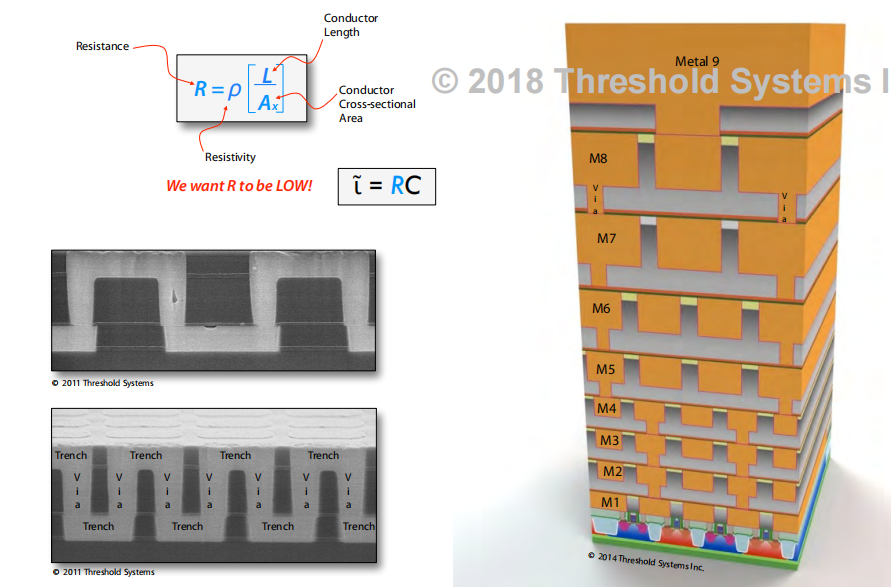

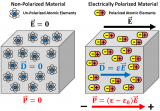

电阻(R)与电容(C)的博弈:信号传输速度由RC时间常数决定。铜(Cu)虽然电阻率低,但金属线间的绝缘介质若介电常数(k值)过高,会大幅增加电容(C),导致RC值飙升。电容耦合效应:相邻金属线通过绝缘介质形成“隐形电容”,信号变化时会相互干扰,进一步加剧延迟。

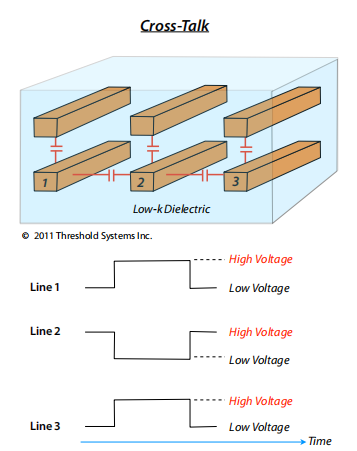

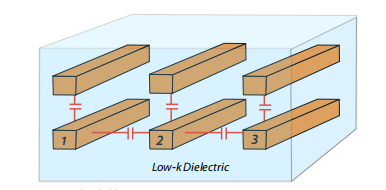

电容耦合:从“串扰”到数据错误的连锁反应

当两条金属线平行排列时,它们之间的绝缘介质会形成电容。这种电容会导致两种问题:信号延迟:电容需要充放电时间,拖慢信号跳变速度。串扰:一条线的电压变化会通过电容耦合干扰相邻线路。

最危险的场景:

假设一条线试图从高电压(如1 V)切换到低电压(0 V),而两侧的线同时从低电压切换到高电压。此时,两侧的高电压会通过电容耦合“拉扯”中间线的电压,导致其无法正常降至低电平,最终引发数据传输错误。

Low-k材料的救赎:如何打破电容困局?

低介电常数材料(Low-k Dielectric)通过降低绝缘介质的*k*值,直接减少金属线间的电容耦合。其核心原理是:降低介电常数:传统SiO₂的k=3.9,而Low-k材料(如碳掺杂氧化物CDO)的*k*可降至2.5-2.8,电容减少30%-40%。抑制电场传播:Low-k材料不易支持电场建立,削弱相邻金属线间的电荷相互作用,从而降低串扰概率。

铜与Low-k的组合

尽管铜的电阻率极低,但单独使用无法解决电容问题。铜互连+Low-k介质的组合成为行业标配:铜降低电阻(R):铜的电阻率(1.68 μΩ·cm)仅为铝的60%,减少信号传输损耗。Low-k降低电容(C):通过减少k值,RC时间常数同步优化,芯片速度提升20%-30%。

未来展望

随着制程进入3纳米以下,行业开始探索k<2.0的超低介电常数

空气隙(Air Gap)技术:在金属线间引入真空孔隙(k=1.0),进一步减少电容。

-

芯片

+关注

关注

463文章

54416浏览量

469203 -

晶体管

+关注

关注

78文章

10439浏览量

148584 -

低介电常数

+关注

关注

0文章

4浏览量

5416

原文标题:为什么芯片需要低介电常数(Low-k)材料

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

低介电常数材料在超大规模集成电路工艺中的应用

介电常数怎么测试_介电常数测试方法

相对介电常数和介电常数的关系

介电常数的定义及应用 不同材料的介电常数比较

介电常数对电子设备的影响

介电常数与频率的关系 影响介电常数的因素有哪些

如何测量材料的相对介电常数

不同材料的相对介电常数比较

材料介电常数会影响电子元器件哪些性能

低介电常数与高介电常数的高分子材料:从机理、结构到应用的全面解析

为什么芯片需要低介电常数材料

为什么芯片需要低介电常数材料

评论