射频收发机早已融入现代人的生活,每天都有海量的数据通过无线方式传输到用户端。您是否对其架构产生过好奇?射频发射机是怎么将庞大的数字信息发射到空气中?射频接收机又是怎么将接收到的信息进行处理?射频收发机里面蕴藏什么关键性技术?本文将随着信号流动的方向带领您领略人类科技的结晶。同时在文章最后,作者将抛砖引玉的分享自己对于射频收发机发展的一些愚见供大家思考。

1. 射频收发机的构成

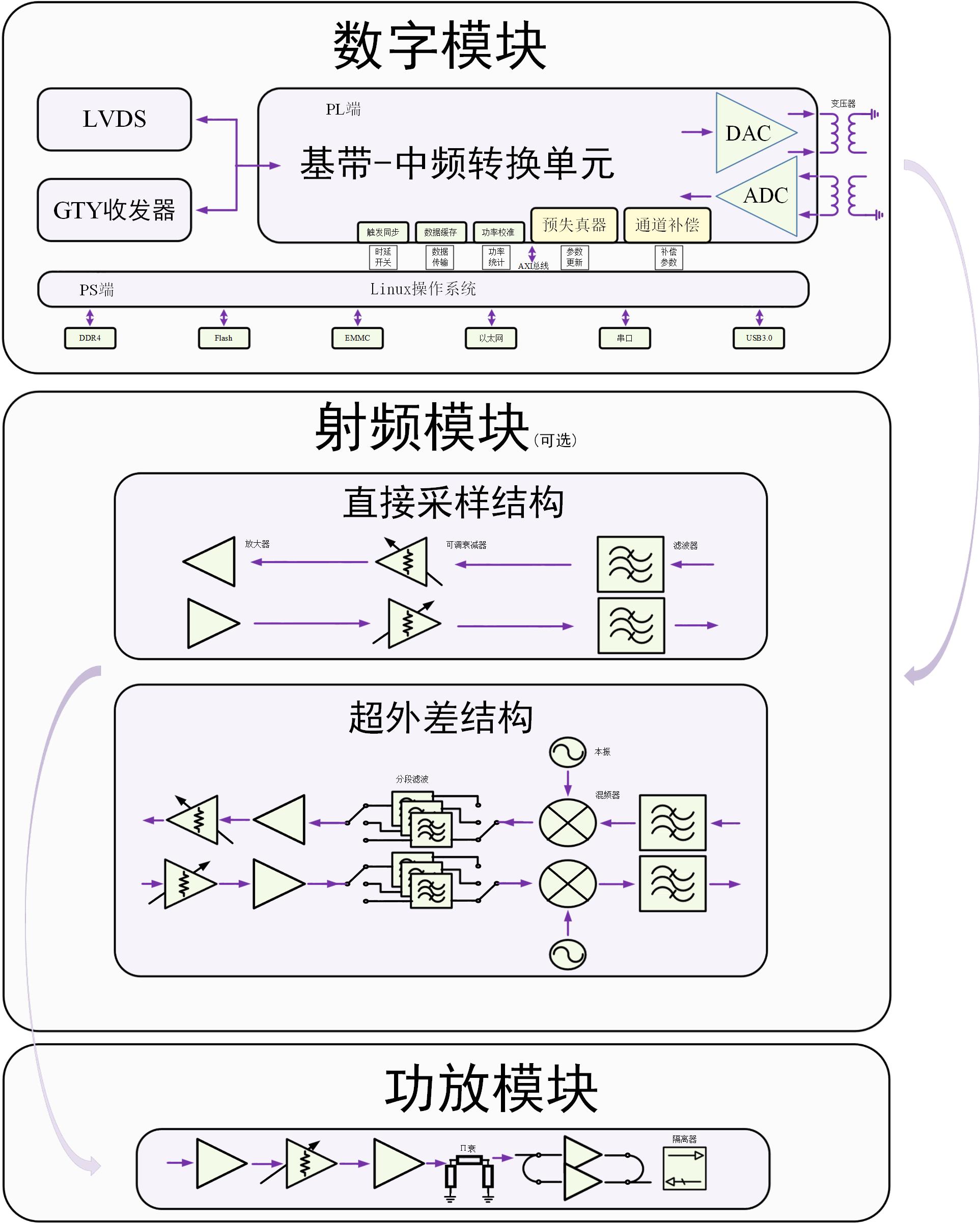

射频收发机是一个很复杂的系统,包含了数据处理、数模转换、频率变换、放大滤波、隔离发射众多步骤。其主要的目的便是将通信专业同学研究的原本只能存在电子设备中的编码波形,变成脱缰的电磁波发射出去;并在其他的地方进行接收并提取信息。射频收发机有源系统部分框图如下图所示

这篇文章将从信号的流动开始,讲述承载信号的硬件模块。为了不让整篇文章显得冗杂且晦涩难懂,笔者会忽略掉每个模块的技术细节,在以后的文章中单独讲解。

2. 信号的流动方式

信号如水流,她不会凭空出现,亦不会突然消失,不论她是什么样的形态都需要一个载体。比如我们发出的声音需要振动的介质,看的文字需要显示的介质,数字世界中的信号传输需要电路。

信号的本质是携带着0或1编码的水流,但水流的大小却受限于接纳她的入口,入口越大,水流越快,大就是好。然而水能载舟,亦能覆舟,大意味着施工难度大,材料需求高,人员成本高,维护难度大,故在不同需求中采用的方案也有所区别。

信号的流动有两种方式,一种是缓存式信号流,另一种是实时式信号流。顾名思义,缓存式信号流是将信号先缓存到存储设备中,如DDR中,再进入信号处理模块;实时信号流则是直接通过GTY收发器、LVDS等接口实时的将外部信号流导入信号处理模块。

为什么会出现两种不同的处理方式呢?对于FPGA本身,内部在不考虑资源消耗的情况下,进行信号流动处理时几乎没有速度限制,他就如一片汪洋的大海。然而信号流的传入接口却需要和外部进行的连接,这样的连接好比汪洋大海的入口只有一个水渠,大大限制了水流大小。下表给出了不同连接协议之间信号传输的速率

| 序号 | 设备 | 速率 |

| 1 | 串口 | 10Mbps |

| 2 | USB2.0/USB3.0 | 480Mbps/5Gbps |

| 3 | 百兆网/千兆网/万兆网 | 100Mbps/1Gbps/10Gbps |

| 4 | SFP+/QSFP+/QSFP28光模块 | 10Gbps/40Gbps/100Gbps |

可以看出,若想要实时传输40Gbps及以上的信号时,只能采用QSFP+和QSFP28光模块;但若想要在未搭载这些接口的硬件设备中,实现更高点数信号的处理,则可以用缓存的方式,以打包的方式来进行传输。就好比点点滴滴汇入星辰大海,理论上串口也可以传输包含千万个数据点的信号,当然其缺点也很明显,需要等待亿点点时间。

3. 信号的处理过程

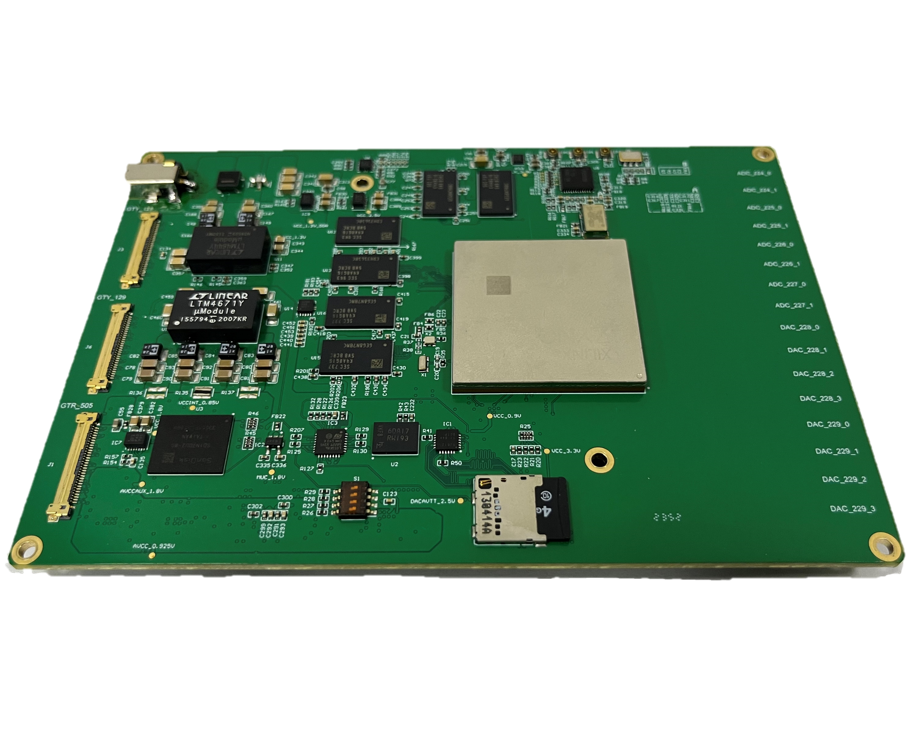

数字模块中数字部分主要由两个部分构成,一个是信号实时流动的路径,另一个则是针对信号流动的参数计算,即FPGA+处理器架构。而处理器架构又分为单片机、ARM、DSP、CPU等等,我们这篇文章不讲很细节的区别。因为本质上,数字模块也都是由一个个逻辑门构成,都和FPGA没有本质区别,而不同的架构本质上可以理解为根据需求不同,其承载不同开发者的社区文化,所分享的软件不同而已。目前国际上一种趋势是将FPGA+处理器同时在同一个芯片中进行实现,如Zynq结构,这样可以将它们之间的数据互通问题更简单的解决掉。

信号在主干道上是不停流动的,其数据处理模块都是并行处理,只能由FPGA来担任。如触发同步、功率校准、预失真器、通道补偿、谐波抑制等模块都是需要例化出实际的电路,信号需要在物理上真实的“流”过这些模块。主干道的模块中有大大小小的开关,这些开关需要在不同的情况下进行切换,将信号导向不同的路段进行传输。

这些开关的控制则需要处理器来实现,而处理器中的指令是逐条实现的,因此速率会相较信号流低很多,其胜在灵活性和统一性。不同算法可以在同样的架构上进行不同的尝试,同时有很多现成的协议。处理器运行操作系统,需要一些外设,包括存储设备Flash、EMMC、SD卡,主要将系统和应用文件放在里面,多种存储设备共存可以互为备份提高整个系统的稳定性;内存设备DDR,开机后的系统文件缓存在其中运行,提高系统稳定性和运行速率;指令传输设备串口/JTAG,可方便开发者进行指令传输和调试;数据传输设备以太网/USB,进行大数据量的交互。

数字模块中数模转换部分主要是DAC和ADC。为什么要进行数模转换呢?这是因为我们需要建立电路到世界的桥梁,电路是人为制造的产物,0和1无法在茫茫空间中传播。除非将人造线缆连接到世界的各个角落,终端,空间站,信号才能进行传输。想要在广袤的空间乃至星海中进行传播,那就必须回归世界本身的规则,产生模拟信号进行传输。事实上,在人类出现前,空间就弥漫着各种电磁波,人类从来都没有发明电磁波,只是发现并利用了它。

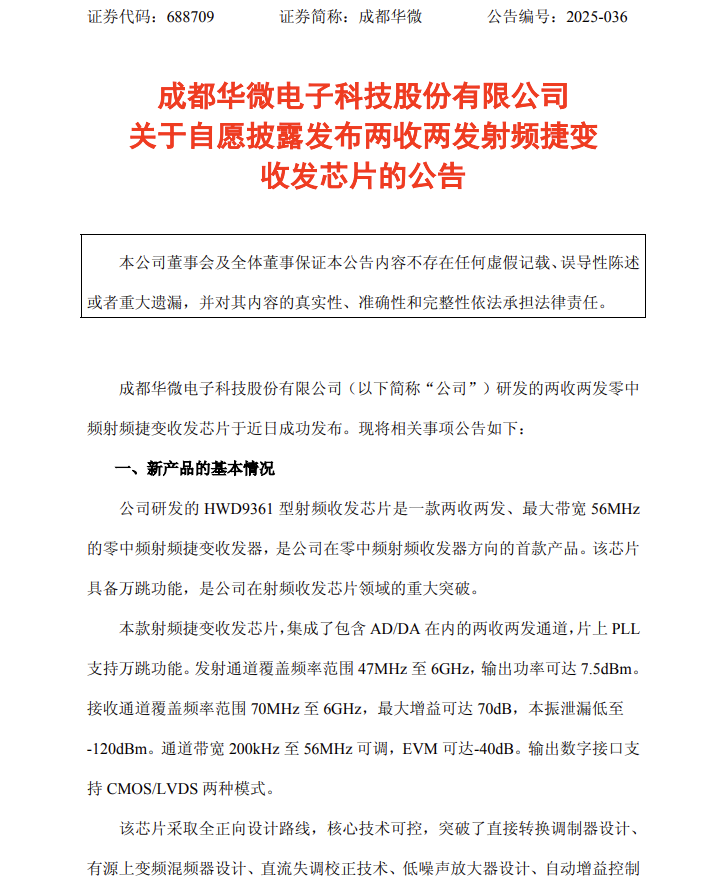

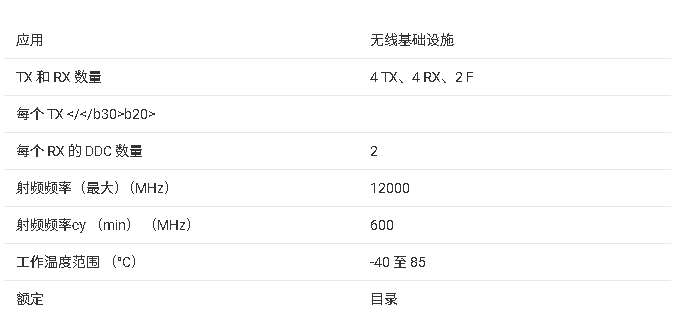

射频模块根据结构主要分为直接采样结构和变频结构。直接采样即不通过变频方式直接处理射频信号,该结构主要是对于技术和工艺的突破,使得DAC和ADC的采样率能超过实际射频频率。如赛灵思的RFSoC ZU47DR芯片中便集成了数字模块和采样率5.0 GSPS的ADC和9.85GSPS的DAC,使得直接发射一个射频频率3.5 GHz,带宽1.2 GHz的宽带信号也绰绰有余。变频结构,不管是零中频架构还是超外差架构,本质都是一种成本和技术上的妥协。如果说直接采样结构是硬骨头扛鼎,那么变频结构则是四两拨千斤。混频器作为杠杆,本振作为支点,将原本低频的信号通过该杠杆变为高频信号方便传播。

功放模块功能则更加简单,信号在空间中传播是存在衰减的,介质会不停的汲取传播过程中的能量。如何将信号传播的更远,那需要将功率增加,一级不够就两级,两级不够就三级,直到功率够格为止,最终放大后的信号便可通过天线发送到空气中进行传播,等待远方同胞进行接收。

4. 射频收发机的关键性技术

前面梳理了射频收发机的构成和运行原理,本节希望对射频收发机中的一些笔者认为的关键技术进行分享。我们目前的研究水平如何?和国际水平存在差异吗?差异要怎么进行弥补?

基础层级下,是射频收发机中各个关键性芯片的突破。从处理高速数据流的FPGA芯片,到高分辨率高采样率的AD/DA;从低相噪低杂散的宽带锁相环,到高频宽带的混频器芯片;从高线性的GaAs射频芯片,到高功率的GaN芯片等等都是需要进行突破的,但这个层面对于普通设计者来说太过遥远。笔者愚见,除了芯片本身的突破之外,目前核心在于观念的突破,系统化的思维的培养。

射频收发机的模块看似不多,但实际上涉及到了许多学科之间的壁垒,每一科进行深入研究都能支撑大大小小独立企业的发展。就如木桶效应中所述的,一个系统的整体效能不是由其最强部分决定,而是最弱部分决定的。笔者主要是研究大功率大带宽矢量收发器这一方向,在这方面,国际顶尖仪器供应商基本都是国外厂商,如罗德与施瓦茨,是德科技,恩艾科技等等。这几年国内仪器厂商如雨后春笋冒出,但在金字塔尖的高端仪器领域还有不少的路需要走。

笔者愚见,其中一个问题在于国内的研究聚焦于独立的专业领域。设计数字模块的仅关注数字编码、采样率、中频频率、DA/AD;设计变频模块的仅关注频段、杂散、相噪、动态;设计功放模块的仅关注增益、功率、线性度;设计射频算法的人才更是寥寥无几,大部分也仅关注IQ不平衡、校准等。虽然也有研究系统的团队,但对于系统间关键性技术还需要进一步探索。最后会陷入一个怪圈,将各个模块进行极致性能打磨后,却最终实现了一个相对平庸的性能。

个人觉得,真正的系统设计理念不应该是这样的。其一,这个世界是公平的,而高端射频收发机中几乎所有指标都是相互制衡的,无法同时达到最佳,无法既要又要;其二,不能让各个模块仅各司其职,而是相互扶持,真正实现数字增强射频,射频创造系统的理念。这里阐述一些笔者认为的关键性技术,相对成熟的方法便不再本文讨论,本文主要是我们射频系统专栏的一个架构性总览文章。工程实现、技术细节、前沿研究等将在以后文章独立分享,敬请期待。

从数字模块开始,FPGA和Linux操作系统可以实现射频算法,其中可形成通道补偿、数字预失真、谐波抑制等IP。通道补偿针对所有射频电路进行补偿,一般采用带记忆项的滤波器组进行补偿,在不同的条件下需要更新补偿条件。数字预失真针对系统非线性进行补偿,谐波抑制针对系统谐波特性进行改善。数字改善确定性,射频改善随机性。比如增益/相位波动、部分杂散、功放基波/谐波非线性特性等属于确定性特性,发挥数字端高精度的特点可事半功倍;而射频则需要解决随机性和提高可改善性,随机性如噪声系数、相噪、部分杂散等。提高可改善性便需要进行比较深入的研究了,需要探索数字电路和射频电路的磨合极限与其平衡点。

射频模块也有很多新的研究点,细心的朋友已经发现我这里使用的是射频模块而不是变频模块。因为变频并不是必须的,DA/AD性能如此强大的如今,混合结构是未来发展的前景,针对不同射频频率采用不同的架构。通过数字模块强大的精确度引入本振对消、杂散对消、时钟对消等技术;通过切换采样率更换中频使得变频结构从二次变频简化为一次变频、一次变频简化为直接采样。在实现相同功能的情况下,越简约的架构,性能和稳定性越高,但简约不意味着简单,相反这需要整个系统的协同配合。

功放模块同样也有很多研究点,功放的前沿研究一直围绕着更宽的带宽、更高的效率进行。功放作为射频收发机系统的功耗大户,除了运营成本之外,更重要的是低能效意味着高热量和低稳定度。晶体管的寿命是受温度影响的,过高的热量会损坏器件,通常一个手指粗细的晶体管消耗的热量需要数十倍于其体积的铝块加上风冷/水冷才能保持系统正常运行。采用电源调制、负载调制等结构均是为了提高其效率,但其又会带来非线性恶化等新的问题,这时数字模块中嵌入射频算法进行联合设计是解决这些问题的办法。

5. 小结

本文针对射频收发机架构进行了简单的分享。同时笔者认为,数字模块、射频模块、功放模块需要联合设计构成一个整体才能发挥其实力,真正做到“聚是一团火,散是满天星”。

www.amplustech.com

审核编辑 黄宇

-

FPGA

+关注

关注

1664文章

22502浏览量

639051 -

移动通信

+关注

关注

10文章

2749浏览量

72160 -

数字模块

+关注

关注

0文章

5浏览量

6406 -

射频收发机

+关注

关注

0文章

28浏览量

6141

发布评论请先 登录

AD9988:4T4R 直接射频收发器的卓越之选

AD9986:4T2R直接射频收发器的卓越之选

AFE77xxD系列射频收发器:5G时代的高性能之选

CC1021单芯片窄带系统低功耗射频收发器深度解析

CC1020:窄带系统低功耗射频收发器的卓越之选

CC1125超高性能射频窄带收发器:设计与应用指南

CC1121高性能低功耗射频收发器:技术剖析与应用展望

CC1120高性能窄带系统射频收发器的深度解析

CC110L:低成本亚1GHz射频收发器的卓越之选

CC1200低功耗、高性能射频收发器:特性、应用及设计要点解析

国内唯一,对标ADI!这家芯片公司发布零中频射频捷变收发器

一文浅谈射频收发机

一文浅谈射频收发机

评论