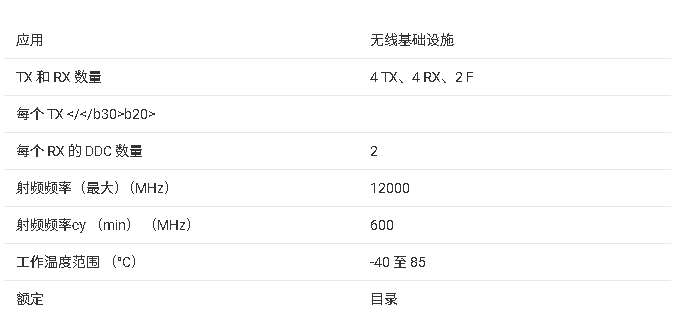

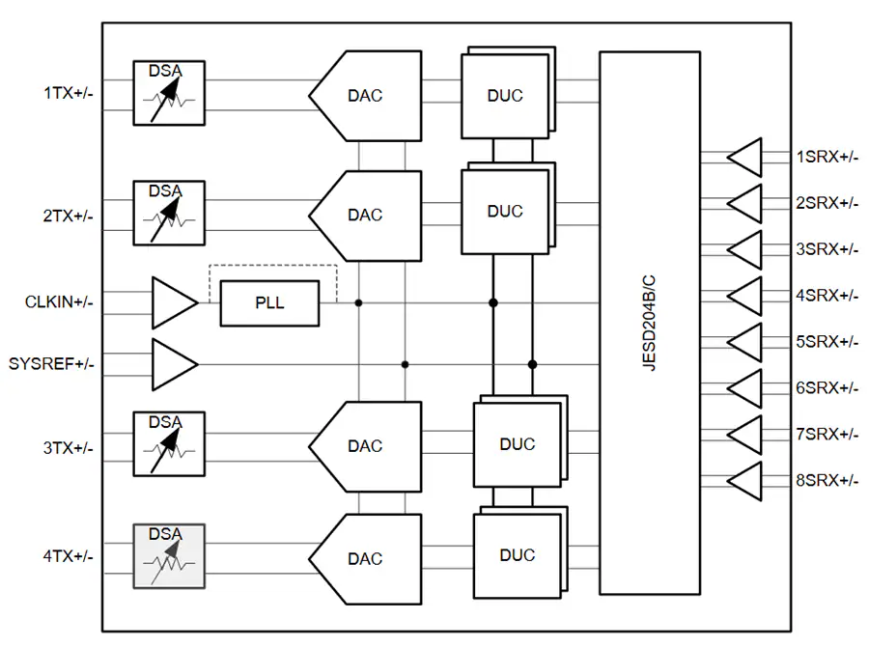

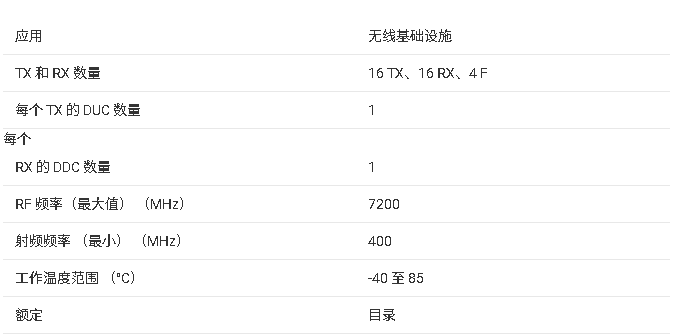

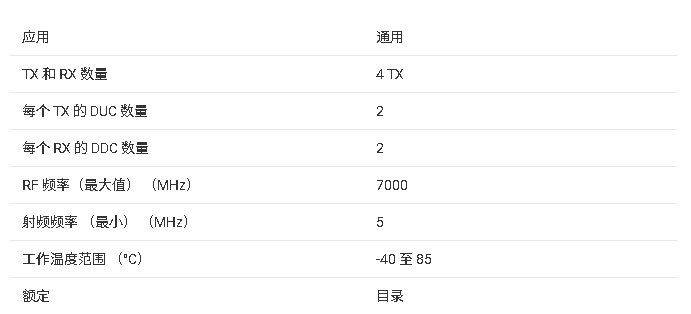

高性能、宽带宽的多通道收发器,集成了四个射频采样发射器链、四个射频采样接收器链和两个射频采样数字化辅助链(反馈路径)。发射机和接收机链的高动态范围使设备能够从无线基站生成和接收 3G、4G 和 5G 信号,而该设备的宽带宽能力专为多频段 4G 和 5G 基站而设计。

*附件:afe7952.pdf

每个接收器链包括一个 25 dB 范围的 DSA(数字步进衰减器),然后是一个 3GSPS ADC(模数转换器)。每个接收器通道都有一个模拟峰值功率检测器和各种数字功率检测器,以辅助外部或内部自主自动增益控制器,以及用于器件可靠性保护的射频过载检测器。单或双数字下变频器 (DDC) 在双 DDC 模式下提供高达 600 MHz 的组合信号带宽,在单 DDC 模式下提供高达 1200 MHz 的组合信号带宽。在TDD模式下,接收器通道可以配置为在流量接收器(TDD RX)和宽带反馈接收器(TDD FB)之间动态切换,并能够将相同的模拟输入重用用于这两个目的。

每个发射器链都包括一个单或双数字上变频器 (DUC),支持高达 2400 MHz 的 2TX 或 1200 MHz 带宽的 4TX 组合信号带宽。DUC 的输出驱动 12GSPS DAC(数模转换器),具有混合模式输出选项,以增强 2 次或 3 次奈奎斯特作。DAC输出包括一个可变增益放大器(TX DSA),具有40 dB范围和1 dB模拟步长和0.125 dB数字步长。

反馈路径包括一个驱动3GSPS射频采样ADC的25 dB范围DSA,然后是一个带宽高达1200 MHz的DDC。

特性

- 四通道射频采样12GSPS发射DAC

- 四通道RF采样3GSPS接收ADC

- 双射频采样 3GSPS 反馈 ADC

- 最大射频信号带宽:

- TX:2400TX 为 2 MHz,1200TX 为 4 MHz

- FB:1200兆赫

- 接收:1200 MHz(无 FB);600 MHz(带 FB)

- 射频频率范围:高达 12 GHz

- 数字步进衰减器 (DSA):

- TX:40 dB 范围,1 dB 模拟步进和 0.125 dB 数字步进

- RX:25 dB 范围,0.5 dB 步长

- 用于 TX 和 RX 的双频 DUC/DDC

- 用于快速频率切换的双 NCO

- 支持 TDD作,可在 TX 和 RX 之间快速切换

- 内部PLL/VCO,用于生成DAC/ADC时钟

- 可选的DAC或ADC速率的外部CLK

- SerDes 数据接口:

- 符合JESD204B和JESD204C标准

- 8 个高达 29.5 Gbps 的 SerDes 收发器

- 8b/10b 和 64b/66b 编码

- 12 位、16 位、24 位和 32 位分辨率

- 子类 1 多设备同步

- 封装:17 mm × 17 mm FCBGA,0.8 mm 间距

参数

方框图

一、产品核心定位与基础参数

AFE7952 以 “多通道集成 + 宽频覆盖 + 高速信号处理” 为核心优势,通过射频直接采样架构、灵活衰减控制与高稳定性时钟设计,满足多频段、多标准无线通信系统的信号收发需求,适配宏基站、小基站、中继器等场景。

1. 核心基础参数总览

| 类别 | 关键指标 | 说明 |

|---|---|---|

| 核心规格 | 通道数 / 分辨率 / 采样率 | 4 路发射(TX)+4 路接收(RX)+2 路反馈(FB);12 位 DAC(TX)/12 位 ADC(RX/FB);TX DAC 最高 12 GSPS,RX/FB ADC 最高 3 GSPS |

| 可靠性特性 | 工作温域 / 封装 / ESD 防护 | 商用温域(0℃~+85℃,具体以实际型号为准);17mm×17mm FCBGA(400 球,0.8mm pitch);需遵循 ESD 防护规范(建议静电手环 / 工作台接地) |

| 供电与功耗 | 供电范围 / 功耗(典型值) | 模拟供电(1.8V/2.5V)、数字供电(1.1V/1.8V);典型功耗:TX 模式约 5W,RX 模式约 4W,低功耗模式(关断未用通道)可降低 30% |

| 核心集成模块 | 关键功能集成 | 数字步进衰减器(DSA)、数字上 / 下变频器(DUC/DDC)、双数控振荡器(NCO)、内部 PLL/VCO、JESD204B/C 高速接口、功率检测器 |

| 频率与带宽 | 射频频率范围 / 信号带宽 | 支持 DC 至 12GHz 射频信号;TX 最大带宽:2 路 TX 时 2400MHz、4 路 TX 时 1200MHz;RX 最大带宽:无 FB 时 1200MHz、有 FB 时 600MHz;FB 最大带宽 1200MHz |

二、核心性能参数

1. 发射链路(TX)性能

TX 链路集成高采样率 DAC 与精细衰减控制,适配多频段信号生成,核心指标如下(典型值,TA=25℃,供电正常):

| 类别 | 关键指标 | 说明 |

|---|---|---|

| DAC 性能 | 采样率 / 分辨率 / 动态范围 | 最高 12 GSPS;12 位;无杂散动态范围(SFDR):1GHz 信号时≥65 dBc,5GHz 信号时≥55 dBc;总谐波失真(THD):-60 dBc(1GHz,-1dBFS 输入) |

| 衰减控制 | DSA 范围 / 步进精度 | 40dB 可调范围;支持 1dB 模拟步进与 0.125dB 数字步进,衰减误差 <±0.5dB(全量程),适配不同功率等级信号输出需求 |

| 信号处理 | DUC 与 NCO 特性 | 每通道集成单 / 双 DUC,支持频率上变频与插值(最高 8x 插值);双 NCO 支持快速频率跳变(跳变时间 < 1μs),频率分辨率 0.1Hz,适配多频段信号切换 |

| 输出特性 | 输出阻抗 / 功率范围 | 差分输出阻抗 50Ω(典型值);最大输出功率:1dB 压缩点(P1dB)≥-5 dBm(1GHz),支持 2nd/3rd 奈奎斯特频段操作 |

2. 接收链路(RX)与反馈链路(FB)性能

RX 与 FB 链路侧重高动态范围与信号保真度,适配弱信号接收与功率闭环控制,核心指标如下:

| 类别 | RX 链路关键指标 | FB 链路关键指标 | 说明 |

|---|---|---|---|

| ADC 性能 | 采样率 3 GSPS,SFDR≥60 dBc(1GHz,-10dBFS) | 采样率 3 GSPS,SFDR≥58 dBc(1GHz,-10dBFS) | 均为 12 位分辨率,噪声谱密度(NSD)≤-150 dBFS/Hz(1kHz 带宽),保障弱信号采集纯净度 |

| 衰减控制 | DSA 范围 25dB,0.5dB 步进,误差 <±0.3dB | DSA 范围 25dB,0.5dB 步进,误差 <±0.3dB | 支持自动增益控制(AGC)联动,避免强信号过载或弱信号失真 |

| 信号处理 | 单 / 双 DDC,支持 1x~32x 抽取,最大带宽 1200MHz | 单 DDC,支持 1x~16x 抽取,最大带宽 1200MHz | DDC 阻带衰减≥-120 dB,减少镜像信号干扰;FB 链路用于功率闭环,优化 TX 输出稳定性 |

| 保护与检测 | 射频过载检测器(阈值可调)+ 峰值功率检测器 | 射频过载检测器(阈值可调) | 过载时自动关断前端电路,避免器件损坏;功率检测器精度 ±1dB,适配 AGC 算法 |

3. 时钟与同步特性

内置高精度时钟管理与多设备同步机制,减少外部时钟器件依赖,适配复杂系统的时序协同需求:

(1)时钟输入与生成

- 内部时钟 :集成 PLL/VCO,支持生成 DAC/ADC 采样时钟,频率范围 1GHz~6GHz,相位噪声≤-110 dBc/Hz(10kHz 偏移,1GHz 输出);

- 外部时钟 :支持外部 CLKIN± 输入(差分,50Ω 阻抗),频率范围 200MHz~3GHz,需 AC 耦合,建议时钟抖动 < 50 fs rms;

- 同步功能 :支持 SYSREF± 差分同步信号,适配 JESD204C 子类 1 多设备同步,同步误差 < 100 ns,满足多通道 MIMO 架构的时序一致性要求。

三、关键功能模块详解

1. 射频链路与信号处理

(1)发射链路(TX)

每路 TX 链路包含 “DUC→DAC→DSA→输出缓冲” 架构,适配多频段信号生成:

- DUC 模块 :支持单 / 双 DUC 配置,双 DUC 模式下可合并 2 路信号(总带宽 2400MHz,2 路 TX 时),单 DUC 模式单路带宽 1200MHz(4 路 TX 时);支持频率上变频(DC 至 12GHz)、插值滤波(最高 8x),减少 DAC 输出杂散;

- DAC 模块 :12 位分辨率,最高 12 GSPS 采样率,支持混合模式输出(优化 2nd/3rd 奈奎斯特频段性能),输出摆幅可调(0.5VPP~2VPP 差分),适配不同功率放大器(PA)输入需求;

- DSA 模块 :40dB 衰减范围,1dB 模拟步进(粗调)+0.125dB 数字步进(细调),通过 SPI 寄存器实时控制,衰减响应时间 < 10ns,适配动态功率调整场景。

(2)接收链路(RX)

每路 RX 链路包含 “输入缓冲→DSA→SHA→ADC→DDC” 架构,保障弱信号接收精度:

- DSA 模块 :25dB 衰减范围,0.5dB 步进,衰减误差 <±0.3dB,支持 AGC 自动控制(外部 MCU 或内部算法),避免强信号过载(ADC 满量程电压 1VPP 差分);

- SHA 与 ADC 模块 :采样保持放大器(SHA)带宽≥12GHz,减少高频信号失真;12 位 ADC 最高 3 GSPS 采样率,支持欠采样(最高 5th 奈奎斯特),适配 12GHz 以下射频信号直接采样;

- DDC 模块 :单 / 双 DDC 配置,双 DDC 模式合并带宽 600MHz(有 FB 时),单 DDC 模式带宽 1200MHz(无 FB 时);支持 1x~32x 抽取,输出数据率降低至 93.75 MSPS(3 GSPS/32),减少后端处理压力。

(3)反馈链路(FB)

2 路 FB 链路架构与 RX 一致(DSA→ADC→DDC),核心用于 TX 功率闭环控制:

- 采样 TX 输出信号(通过耦合器),ADC 采样率 3 GSPS,DDC 带宽 1200MHz,实时监测 TX 功率;

- 输出数据反馈至基带芯片,调整 TX DSA 与 DAC 增益,保障输出功率稳定性(误差 <±0.5dB),适配多天线功率一致性要求。

2. JESD204B/C 高速数据接口

采用 JESD204B/C 高速串行接口实现基带与射频链路的数据传输,支持高带宽、低延迟与多设备同步,适配 FPGA / 基带处理器的高速数据交互需求:

(1)接口特性

- ** lanes 与速率 **:8 路 SerDes 收发器,单 lane 最高速率 29.5 Gbps;支持 8B/10B(兼容 JESD204B)与 64B/66B(JESD204C)编码,64B/66B 模式提升带宽效率(减少编码开销);

- 数据分辨率 :支持 12 位、16 位、24 位、32 位数据格式,适配不同精度需求;例如 TX 模式 12 位 DAC 数据,采用 32 位格式传输(含校验位),提升数据可靠性;

- 同步与测试 :支持子类 1 多设备同步(SYSREF 信号触发),同步误差 < 100 ns;内置 PRBS 测试模式(7/15/23 位),便于链路误码率(BER)验证。

(2)数据交互流程

- TX 方向 :基带芯片通过 JESD204C 接口发送数字基带信号→器件内部 DUC 上变频→DAC 转换为模拟射频信号→DSA 衰减→输出至 PA;

- RX/FB 方向 :天线接收信号→DSA 衰减→ADC 采样→DDC 下变频 / 抽取→JESD204C 接口传输至基带芯片;

- 带宽匹配 :TX 最大数据率:12 GSPS×12 位 = 144 Gbps(8 路 SerDes 均分,单 lane 18 Gbps);RX 最大数据率:3 GSPS×12 位 ×4 路 = 144 Gbps,接口带宽完全匹配信号处理需求。

3. 时分双工(TDD)与频率切换

适配 TDD 系统(如 5G NR TDD)的快速收发切换需求,核心特性如下:

- 切换速度 :TX 与 RX 模式切换时间 < 1μs,支持动态通道复用(如 RX 通道可切换为 FB 通道),适配 TDD 帧结构(最短时隙 100μs);

- 频率捷变 :双 NCO 设计,支持 TX/RX 频率独立调整,跳变时间 < 1μs,频率分辨率 0.1Hz,适配多频段切换(如 Sub-6GHz 与毫米波频段);

- 干扰抑制 :切换时自动关断未用链路前端,减少 TX 到 RX 的泄漏(隔离度≥60 dB),避免接收端过载。

四、典型应用场景与设计建议

1. 核心应用场景

AFE7952 的核心价值在于 “多通道集成 + 宽频覆盖”,典型应用包括:

- 5G 宏基站远程射频单元(RRU) :4 路 TX+4 路 RX 支持 4T4R MIMO,12GHz 频率覆盖 Sub-6GHz 与毫米波频段,JESD204C 接口连接基带单元(BBU),FB 链路保障多天线功率一致性;

- 有源天线系统(AAS) :多器件级联(通过 SYSREF 同步),实现大规模 MIMO(如 32T32R),DSA 精准控制每路天线增益,适配波束赋形需求;

- 5G 毫米波 radio :支持 12GHz 以下毫米波信号直接采样,TX DAC 12 GSPS 保障 2400MHz 带宽,适配毫米波宽 band 信号收发;

- 分布式天线系统(DAS) :小尺寸封装(17mm×17mm)适配紧凑型远端单元,低功耗模式降低部署功耗,支持多频段信号中继。

典型应用电路示例(5G 宏基站 RRU)

- 电路结构 :4 路 TX 通道连接 4 个功率放大器(PA),输出至天线;4 路 RX 通道连接 4 个低噪声放大器(LNA),接收天线信号;2 路 FB 通道采样 PA 输出(耦合器),JESD204C 接口连接 FPGA(如 Xilinx UltraScale+),CLKIN± 输入 5GHz 外部时钟;

- 关键器件 :时钟采用低抖动晶振(<50 fs rms),电源端并联 1μF 钽电容 + 0.1μF 陶瓷电容滤波,射频输入 / 输出串联 50Ω 匹配电阻;

- 性能指标 :TX 输出功率 20 dBm(1GHz),SFDR 65 dBc;RX 噪声系数(NF)2.5 dB,SFDR 60 dBc,满足 5G NR 100MHz 带宽信号收发需求。

2. 关键设计建议

(1)电源与时钟设计

- 电源隔离 :模拟电源(TX/RX 前端)与数字电源(JESD204C / 控制逻辑)独立布线,单点连接至地平面;模拟电源路径采用宽铜皮(≥2mm),减少压降;

- 时钟优化 :CLKIN± 采用差分微带线布线(特性阻抗 100Ω),长度 < 100mm,避免与数字线平行;外部时钟建议加缓冲器(如 TI CDCL6208),降低相位噪声;

- 接地设计 :AGND(模拟地)与 DGND(数字地)单点连接,FCBGA 暴露焊盘(Thermal Pad)连接 AGND,降低热阻(RθJA≈25℃/W)。

(2)射频与 PCB 布局

- 射频布线 :TX/RX/FB 射频端口采用差分微带线(特性阻抗 100Ω),长度 < 50mm,减少信号损耗;射频线与数字线间距≥3mm,避免串扰;

- 衰减控制 :DSA 控制信号(SPI)采用屏蔽布线,靠近器件引脚,减少干扰导致的衰减误差;

- 测试点设计 :在 TX/RX 输出端预留测试点,便于射频性能(功率、SFDR)调试;JESD204C lanes 预留误码率测试点。

(3)校准与可靠性

- 校准周期 :建议每上电或温变 10℃后,执行一次增益 / 偏移校准(通过 SPI 写入校准值),保障全温域精度;

- ESD 防护 :射频端口建议加 TVS 管(如 SMBJ5.0CA),避免雷击或静电损坏;

- 通道关断 :未使用的 TX/RX/FB 通道通过寄存器关断,降低功耗并减少干扰。

-

收发器

+关注

关注

10文章

3794浏览量

110555 -

发射器

+关注

关注

7文章

916浏览量

55124 -

无线基站

+关注

关注

0文章

68浏览量

12682 -

射频采样

+关注

关注

0文章

56浏览量

4711 -

宽带宽

+关注

关注

0文章

46浏览量

1329

发布评论请先 登录

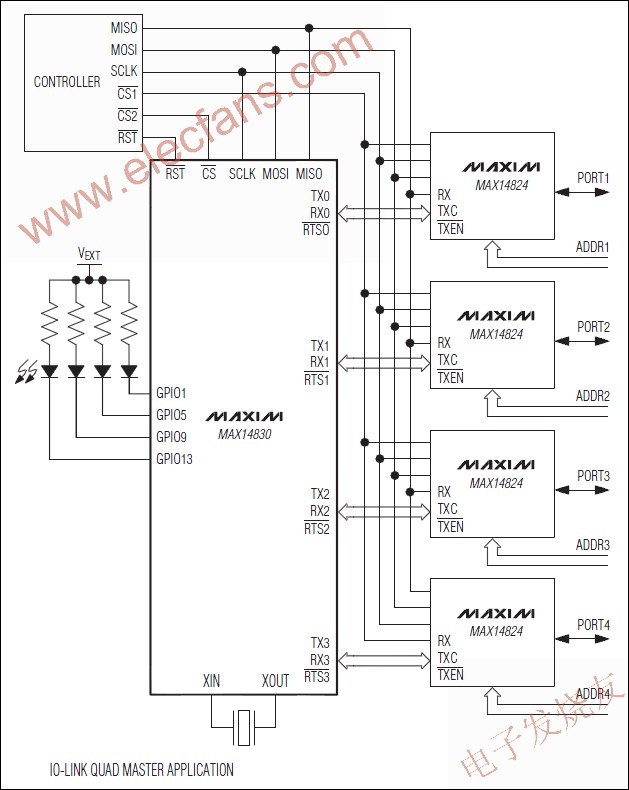

MAX14830 四通道通用异步收发器(UART)

TI推出业内首款集成四通道和双通道射频采样收发器,实现多天线宽带系统

四通道异步收发器TL16C554芯片特点、工作原理及实现应用设计

DS25BR400四通道2.5 Gbps CML收发器数据表

DS42BR400四通道4.25 Gbps CML收发器数据表

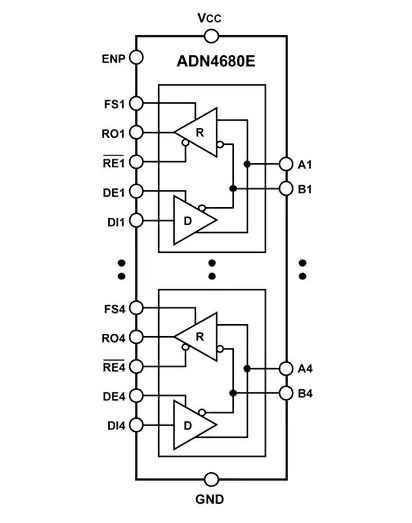

Analog Devices Inc. ADN4680E四通道M-LVDS收发器数据手册

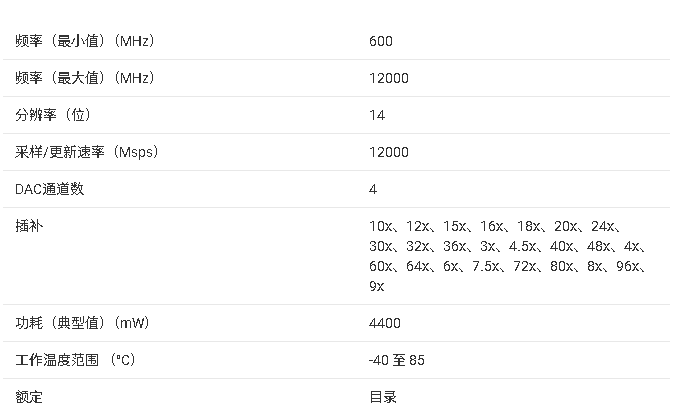

AFE7954 四通道射频采样 12 GSPS 数模转换器(DAC)技术总结

AFE7952 四通道射频收发器技术文档总结

AFE7952 四通道射频收发器技术文档总结

评论