作者:刘松,文章来源: 松哥电源微信公众号

美国计划禁止用于Gate-all-around GAA新技术制造芯片所必需的EDA软件出口到中国大陆,GAA(环绕栅极)是GAA FET,那么,什么是GAA FET(环绕栅极场效应晶体管)?

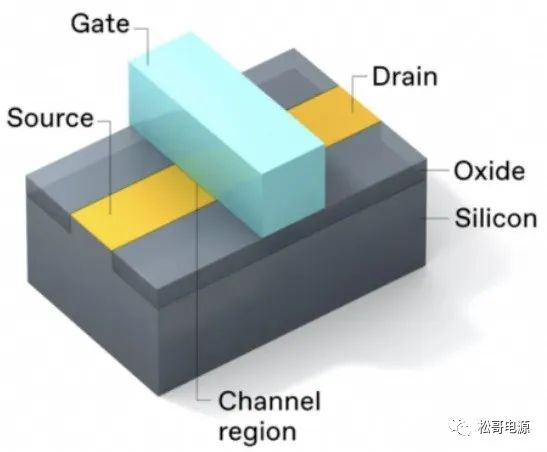

数字芯片最基本单元是MOSFET,其工艺发展到7nm、3nm、2nm,这个半导体工艺尺寸是MOSFET栅极(沟槽)宽度。早期MOSFET使用平面结构,沟槽宽度越小,漏极到源极距离越小,载流子流动跨越沟道导通时间减小,工作频率越高;同时,沟道完全开通所加栅极电压越低,开关损耗越低;而且,沟道导通电阻降低,导通损耗也降低。

但是,工艺尺寸越低,短沟道效应越明显。短沟道效应就是晶胞单元漏极到源极间距不断减小,栅极下部接触面积越来越小,栅极难以耗尽沟道载流子,其对沟道控制力不断减弱;因此,器件处于截止状态时漏电流会急剧增加,恶化其性能,静态功耗增加。

图1:平面MOSFET结构

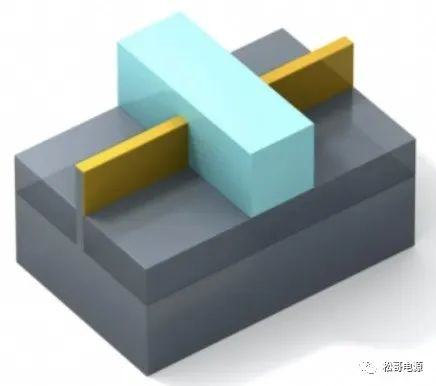

如果采用立体结构,增加栅极和沟道接触面积,如新的FinFET鳍型三维结构,就是将栅极包裹三个侧面沟道,就可以解决上述问题,如图2所示。

图2 FinFET鳍型结构

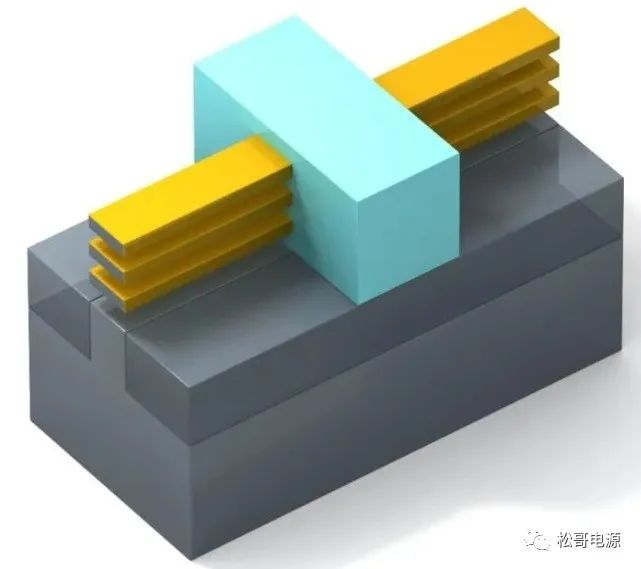

为了进一步提高栅极对沟道控制能力,缩小单元尺寸,降低电压,GAA栅极环绕结构被开发出来,如图3所示。

图3 栅极环绕结构

GAA栅极环绕晶体管结构的栅极在垂直方向被分成几个条带RibbonFET,在其沟道区域,大幅增强对载流子控制,从而实现更好性能,同时也更容易优化工艺。

免责声明:本文为网络转载文章,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除。

审核编辑 黄宇

-

eda

+关注

关注

72文章

3143浏览量

183785 -

栅极

+关注

关注

1文章

188浏览量

21749

发布评论请先 登录

工艺升级是否必要性,EUV和GAAFET技术解读

三星推GAAFET技术 将基于它打造3nm芯片

三星将EUV与10nm工艺结合推出LPDDR5内存芯片

硬创早报:三星全球首秀3nm!电压只需0.23V

GAAFET,是什么技术?

GAAFET,是什么技术?

评论