文章来源:十二芯座

原文作者:MicroX

本文图解介绍了GAAFET(Gate-All-Around FET)的制造流程。

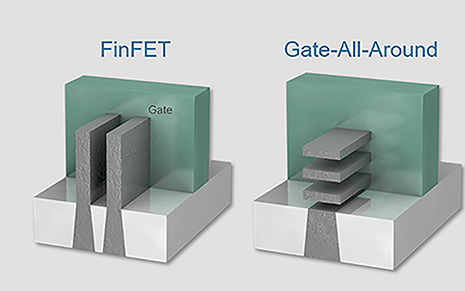

随着集成电路制程迈向3nm及以下节点,FinFET(鳍式场效应晶体管)由于三面栅控能力的局限,难以抑制严重的短沟道效应。

GAAFET(Gate-All-Around FET)通过将栅极完全包裹在纳米片(Nanosheet)通道四周,实现了近乎完美的电子控制。

超晶格生长(Superlattice Epitaxy)

制造始于在硅衬底上交替生长Si(硅)和SiGe(硅锗)的多层外延结构。

工艺细节:使用化学气相沉积(CVD)精确控制每层厚度。

逻辑:SiGe层仅作为“牺牲层”,为后续腾出空间;Si层则是最终的电子通道。

鳍片刻蚀与浅沟槽隔离(Fin Etch & STI)

与FinFET类似,通过光刻和干法刻蚀将超晶格结构切割成条状。

挑战:刻蚀必须保持极高的垂直度,确保多层Si/SiGe堆叠结构的侧壁平整。

Dummy Gate 形成

内侧墙形成(Inner Spacer Formation)

这是GAA工艺中最独特的一步。在沉积 Dummy Gate 后,需要侧向刻蚀掉一部分SiGe层,并填充介电材料形成内侧墙。

作用:内侧墙将源/漏极(Source/Drain)与金属栅极隔离开,极大降低了寄生电容(Cgs/Cgd)。

技术难点:必须使用极高选择比的各向同性刻蚀,确保只移除预定深度的SiGe,而不损伤Si层。

源漏区外延

SiGe/ SiP EPI

纳米片释放(Channel Release)

在替换金属栅(RMG)工艺中,通过高选择比的湿法或干法刻蚀彻底清除所有的SiGe层,使Si纳米片如同“悬空的桥”一般悬挂在源漏之间。

物理瓶颈:此时纳米片极其脆弱,表面张力可能导致纳米片塌陷粘连(Stiction)。

高K金属栅(HKMG)沉积

最后,利用原子层沉积(ALD)技术,将高K电介质和金属栅极材料“塞进”纳米片之间的极小缝隙(通常小于10nm)。

均匀性要求:ALD必须保证在纳米片的顶面、底面和侧面均匀成膜,实现全环绕包裹。

Contact 形成

-

集成电路

+关注

关注

5463文章

12667浏览量

375607 -

晶体管

+关注

关注

78文章

10434浏览量

148540 -

FinFET

+关注

关注

12文章

262浏览量

92353

原文标题:GAAFET(全环绕栅极晶体管)制造流程图解

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

应用材料公司以技术助力极紫外光和三维环绕栅极晶体管实现二维微缩

下一代高速芯片晶体管解制造问题解决了!

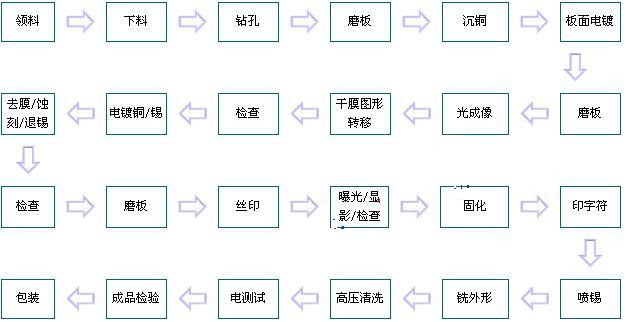

双面板制作流程及镀金、喷锡和FPC板流程图解

镀金、喷锡和FPC板流程图解

三星推GAAFET技术 将基于它打造3nm芯片

如何生产3纳米以下全环绕栅极晶体管?

全环绕栅极晶体管将如何改变半导体行业

鳍式场效应晶体管制造工艺流程

GAAFET全环绕栅极晶体管制造流程图解

GAAFET全环绕栅极晶体管制造流程图解

评论