来源;《半导体芯科技》杂志

作者:黄泰源、罗长诚、钟兴进,广东鸿浩半导体设备有限公司

摘要

扇出晶圆级封装广泛应用于手机、车载等电子产品上。制造过程中需要使用到暂时性基板,而移除暂时性基板最适当的方式为激光解键合。鸿浩半导体设备所生产的UV激光解键合设备具备低温、不伤晶圆等技术特点,并且提供合理的制程成本,十分适合应用于扇出晶圆级封装。

01

扇出晶圆级封装简介

扇出晶圆级封装(Fan Out Wafer Level Packaging, FOWLP,简称扇出封装)是一种新型的晶圆级电子封装技术。与标准的晶圆级封装(Wafer Level Packaging, WLP)或称为扇入晶圆级封装(Fan In WLP)相比,可以扩大封装面积,因而容纳更多的输入/输出引脚(I/O),同时实现更薄、更扁平的封装形貌,并且能以较低的成本来生产具有良好电器特性的电子组件。

由英飞凌与意法半导体和星科晶朋共同开发的eWLP是第一个商业化的扇出封装。当时的发展背景即是为了应对愈来愈多的输出入引脚的需求。解决方式是加大扇出空间来容纳更多的引脚。eWLB于2009年中量产,并且开始应用于手机芯片上。

自2010年代以来,已有多家包括半导体晶圆厂、封测厂开发各式的扇出封装技术,如台积电的InFO、三星的FOSiP、安靠的SWIFT、日月光的FOEB等等。并且往系统级封装、堆栈封装发展,成为整合度更高、互连速度更顺畅的电子构装组件。扇出封装目前大规模应用于智能手机、穿戴装置、电源管理、射频组件、车用电子等领域,由于易于进行异质整合,加上具有高性价比的优势,使用量与应用范围有愈来愈扩大的趋势。

02

扇出晶圆级封装制造流程

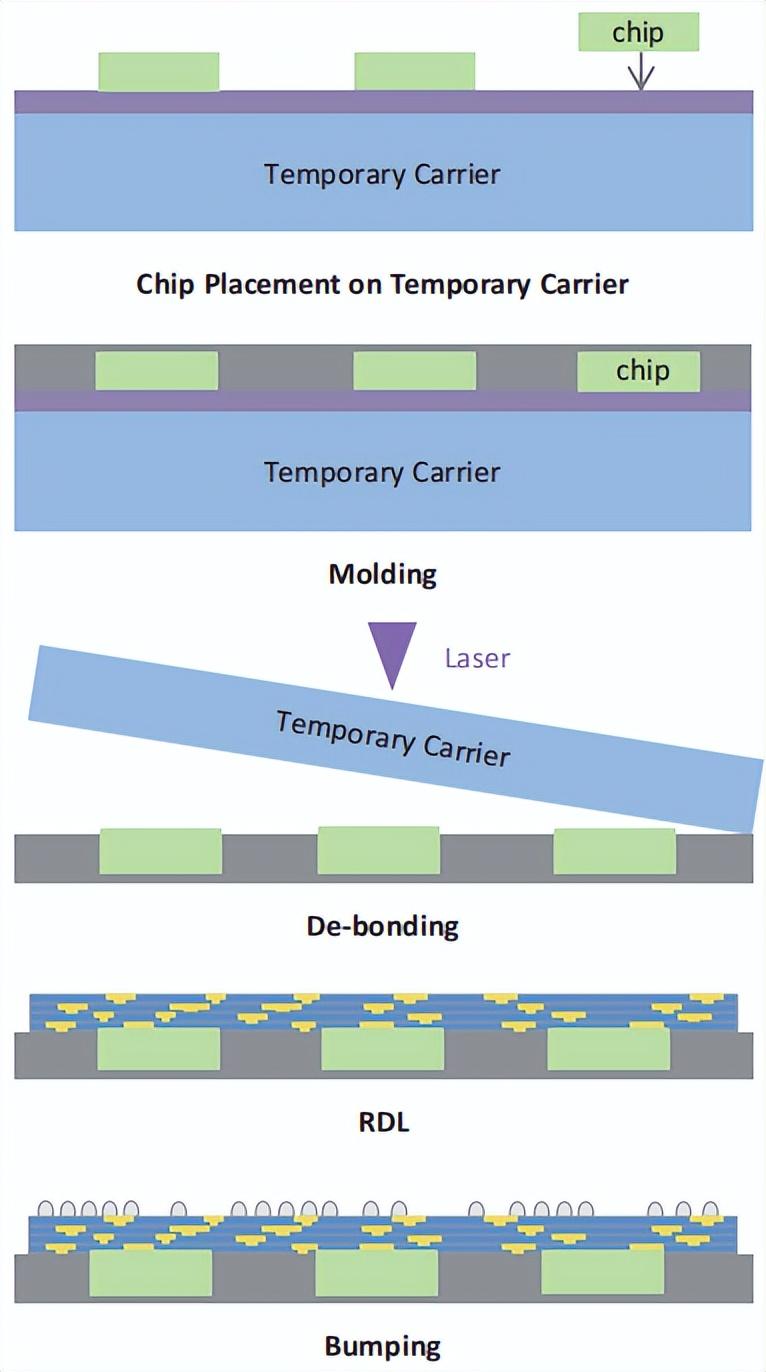

传统的晶圆级封装是在已完成前段制程的晶圆片上针对晶圆片上的芯片来进行,芯片封装面积大小取决于原本在晶圆上针对芯片所预留的间距。扇出封装则可藉由——重组晶圆(Reconstitutional Wafer)来决定芯片的封装尺寸。重组晶圆是依托在暂时性基板(Temporary Carrier)上,这个暂时性基板最终经过解键合(De-bonding)的工艺技将其从重组晶圆上移除。扇出封装首先藉由重新排列芯片形成一个重组晶圆。芯片先从原本的晶圆片上切割下来,然后根据设计依一定的间距进行芯片的排列。

接下来在晶圆片上进行重新布线(RDL)、塑封与形成引脚。以上工艺流程称为Mold First扇出技术。也有先进行重新布线再进行固晶(Die Bonding),称为RDL First扇出技术。

暂时性基板仅是做为承载芯片的载体,在完成芯片塑封后,需要将其除去。这个去除暂时性基板的工艺即称为剥离或解键合(De-bonding)。典型的FOWLP的工艺制作流程如图1。

△图1:扇出晶圆级封装的工艺流程

03

激光解键合技术

解键合的方式从早期的化学解键合方式、机械解键合方式、热滑移等方式,进展到激光解键合。其中,激光解键合技术是新近发展出来的技术,目前已有涵盖紫外到红外数种不同波长的激光解键合技术。

化学解键合方式采用浸泡在化学溶剂中的方式,将胶材慢慢地溶解,最终将暂性基板和晶圆片分离。为了增加化学溶剂溶解胶材的效率,会先在暂性基板上均匀地开上数十至上百个孔。即使如此,化学解键合方式的效率仍然很低。

机械解键合的方式是透过边缘的受力点,藉由施力让胶材接口产生劈裂,然后沿着劈裂面持续施力,最终使晶圆片与暂时性基板分离。在施力时,晶圆片无可避免会承受应力,因而增加了破片的风险。

热滑移方式是先将胶材加热致使其软化,然后施加一剪切力让暂时性基板与晶圆片产生相对的滑移,使得暂时性基板分离。该方式所使用的胶材通常不能承受高温的制程,因而限制其应用范围。

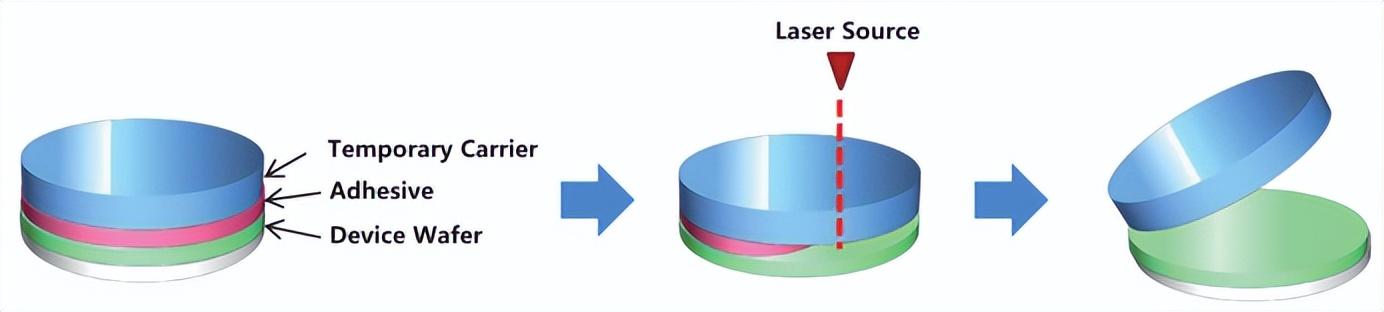

△图2:激光解键合工艺意的流程图

激光解键合则是藉由快速将激光能量照射在胶材上,使胶材产生部分解离,藉此将暂时性基板与晶圆片分离。采用激光解键合工艺,首先会在暂时性基板上涂布或贴合一层激光解键合专用的胶材(Laser Release Layer),接下来的制程工艺都是在这个基板上进行。完成封装制程后,通过激光作用在胶材上,将晶圆片与暂时性基板分离。在这个过程中,激光会穿过透明的玻璃片,到达胶材表面,以扫描的方式均匀地将激光能量施加在胶材上,快速地将胶材和玻璃分开。图2为激光解键合的流程图,激光解键合机的工作示意图见图3。

由于激光是无应力的解键合方式,相当大幅度地降低破片的风险,因此可以大幅提升解键合过程的成功率,提高良率。当晶圆片厚度愈来愈薄、线宽线距持续缩小,激光解键合的优势将更加明显。

解键合技术主要的要求为:

1.低应力,不能造成破片

2.对芯片的热冲击愈小愈好

3.激光能量不能损伤芯片

4.产出的速度要快

5.合理的制程成本

6.足够的技术成熟度以及客户采用

7.对于未来技术应用延伸的潜力

根据以上的需求,表1给出了各种解键合方式的比较。其中可以发现,使用紫外固态激光解键合技术在各项指标大体都十分优良,并具有最佳的技术延伸的潜力。

△表1.各种解键合技术的比较

04

鸿浩激光解键合设备

广东鸿浩半导体设备有限公司(以下简称“鸿浩”)所选用的解键合技术即为紫外固态激光技术,率先成功量产紫外激光解键合设备,并首先应用于扇出晶圆级封装制造工艺,该设备(如图4所示)具有以下特点:

1.激光是针对胶材进行解键合,对晶圆片的分离产生的应力极低。

2.采用短脉冲激光,作用时间短,所产生的热效应低。

3.选用的波长绝大部分作用于胶材,不会有击伤芯片的风险。

4.采用高速激光,具有高产出速度的优点。

5.设备维护费用低廉,可以提供合理的制程成本。

6.鸿浩自有应用技术实验室,已经验证多种胶材,适用于多种应用场域。

△图4:鸿浩激光解键合设备外观图

鸿浩的紫外激光解键合设备已经打入包括先进封装、第三代半导体、Micro-LED等各领域主要客户。鸿浩也期待能与更广大的客户进行交流、服务更多的客户。

苏州会议

雅时国际(ACT International)将于2023年5月,在苏州组织举办主题为“2023-半导体先进技术创新发展和机遇大会”。会议包括两个专题:半导体制造与封装、化合物半导体先进技术及应用。分别以“CHIP China晶芯研讨会”和“化合物半导体先进技术及应用大会”两场论坛的形式同时进行。详情点击链接查看:https://w.lwc.cn/s/7jmaMn

审核编辑黄宇

-

激光

+关注

关注

21文章

3707浏览量

69820 -

晶圆

+关注

关注

53文章

5449浏览量

132762 -

封装

+关注

关注

128文章

9330浏览量

149047

发布评论请先 登录

什么是晶圆级扇入封装技术

激光解键合在扇出晶圆级封装中的应用

激光解键合在扇出晶圆级封装中的应用

评论