来源:先进封装技术与工艺

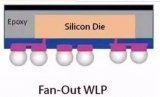

在后摩尔时代,扇出型晶圆级封装(FOWLP) 已成为实现异构集成、提升I/O密度和缩小封装尺寸的关键技术路径。与传统的扇入型(Fan-In)封装不同,FOWLP通过将芯片重新排布在重构晶圆上,利用塑封料(EMC) 扩展芯片面积,从而在芯片范围之外提供额外的I/O连接空间。根据工艺流程的差异,FOWLP主要分为三大类:芯片先装(Chip-First)面朝下、芯片先装面朝上以及RDL先制。本文将深入剖析这三种工艺的具体流程、关键技术难点及优劣势对比。

01芯片先装面朝下工艺

这是最早实现商业化量产的FOWLP工艺,以英飞凌的eWLB技术为代表。其核心逻辑是先将芯片贴装在临时载板上,再进行塑封和重布线。

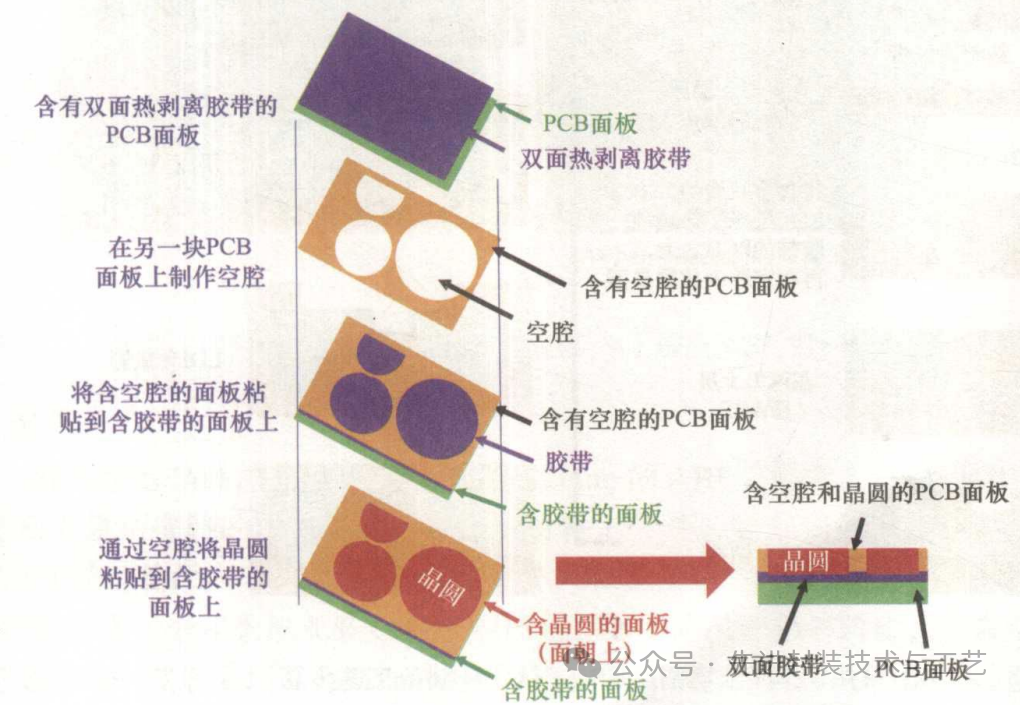

该工艺的典型流程起始于一个临时载板,通常为金属或硅材质。首先,在载板上层压一层热释放胶带。接着,利用高精度的贴片机将经过测试的良品芯片(KGD)以有源面朝下的方式精确放置在胶带上。

随后进行压缩模塑,将塑封料填充在芯片周围,形成重构晶圆。在塑封固化后,通过加热使热释放胶带失去粘性,从而将重构晶圆与临时载板分离(即解键合)。此时,芯片的有源面和塑封料表面处于同一平面。

接下来,通过物理气相沉积(PVD) 溅射Ti/Cu作为种子层,利用光刻和电镀工艺制作重布线层(RDL) 和钝化层。最后,在RDL的末端制作凸点下金属层(UBM) 并植入焊球(Solder Balls),经切割后完成封装。

芯片先装FOWLP工艺流程示意图

技术挑战: 此工艺最大的痛点在于芯片偏移(Die Shift)。在塑封过程中,流动的塑封料会对芯片产生推力,导致芯片位置偏离预设坐标。此外,重构晶圆在固化冷却过程中,由于硅芯片与塑封料的热膨胀系数(CTE) 差异,会产生严重的翘曲(Warpage)。这种位置偏移和翘曲会导致后续光刻对准困难,造成RDL与芯片焊盘连接失效,严重影响良率。

02芯片先装面朝上工艺

为了应对面朝下工艺中的部分局限性,面朝上工艺应运而生。其流程差异主要在于芯片的放置方向和互连方式。

在此流程中,芯片以有源面朝上的方式通过芯片贴装膜(DAF) 固定在载板上。在进行压缩模塑覆盖整个芯片后,不需要立即解键合。相反,必须通过研磨工艺减薄塑封层,直到暴露出芯片表面的铜柱或以其他方式显露电极。

随后,在平整的塑封面上制作RDL,通过电镀通孔连接到芯片电极。这种方式可以通过增加铜柱的高度来适应3D封装的需求。

技术优劣: 面朝上工艺通过铜柱延伸了连接距离,有利于散热和应力缓冲。然而,研磨过程控制精度要求极高,一旦研磨过度损伤芯片电路,或者研磨不足导致连接开路,都会导致报废。此外,芯片背部贴装在载板上,虽然减少了部分水平偏移,但垂直方向的共面性仍是挑战。

03RDL先制工艺

随着高性能计算对I/O密度和多层RDL需求的增加,RDL先制工艺(亦称Chip-Last)逐渐成为高端封装(如台积电InFO技术)的首选。与前两者不同,该工艺先在载板上制作RDL,再贴装芯片。

流程首先在涂有牺牲层(Sacrificial Layer) 的载板上,通过PVD和电镀工艺制作精细的RDL线路和介电层。这一步类似晶圆厂后道工艺,可以实现极小的线宽线距(L/S)。RDL制作完成后,将芯片通过倒装(Flip-Chip) 或直接键合的方式贴装在RDL上。随后进行塑封,并在塑封体背部进行研磨或开孔。最后,去除载板并释放牺牲层,露出RDL的接触焊盘用于植球。

FOWLP上的RDL

核心优势:

良率提升:由于RDL是在平整的载板上预先制作的,若RDL出现缺陷,可以由光学检测剔除,避免了将昂贵的良品芯片(KGD) 贴装在坏的RDL上,从而显著降低了成本风险。

高密度互连:避免了芯片先装工艺中塑封后的表面不平整问题,能在载板上实现更精细的布线(例如2μm/2μm L/S),非常适合高密度集成的应用处理器(AP) 封装。

在上述三种FOWLP工艺中,芯片先装(面朝下) 因其工艺路径短、成本低,依然是中低端市场的主流选择,但必须严格控制芯片偏移和翘曲问题。芯片先装(面朝上) 则在特定的3D堆叠场景中由于铜柱互连的存在占有一席之地。而RDL先制尽管流程较长、成本较高,但凭借其对已知良品载板的筛选能力以及对高密度布线的支持,已确立了其在高性能计算和高端移动终端封装领域的统治地位。

随着板级扇出型封装(FOPLP) 的兴起,这些工艺正逐渐从晶圆级向大尺寸面板级转移,这对光刻设备的焦深、贴片机的速度以及电镀均匀性提出了更严苛的挑战。未来的竞争焦点将集中在如何在扩大面板尺寸以降低成本的同时,通过材料创新和应力模拟来有效抑制翘曲,实现高可靠性的异构集。

-

工艺流程

+关注

关注

7文章

118浏览量

16874 -

晶圆级封装

+关注

关注

5文章

47浏览量

11821 -

FOWLP

+关注

关注

1文章

18浏览量

10199

原文标题:晶圆级扇出型封装(FOWLP):三大核心工艺流程与技术壁垒深度解析

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆级扇出型封装的三大核心工艺流程

晶圆级扇出型封装的三大核心工艺流程

评论