在FPGA设计中,双向IO(输入输出引脚)是一个比较麻烦的东西,但是信号线用作总线等双向数据传输时就要用到inout类型。

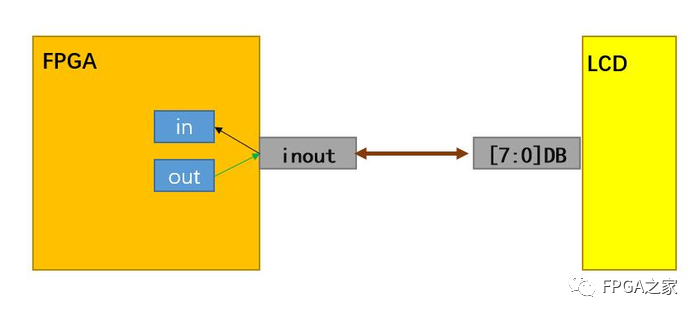

以下用液晶的的数据线用作双向IO示例:

说是双向IO端口,其实输入和输出不是同时进行的,需要有一个控制信号out_en来控制端口什么时候为输出,什么时候为输入。

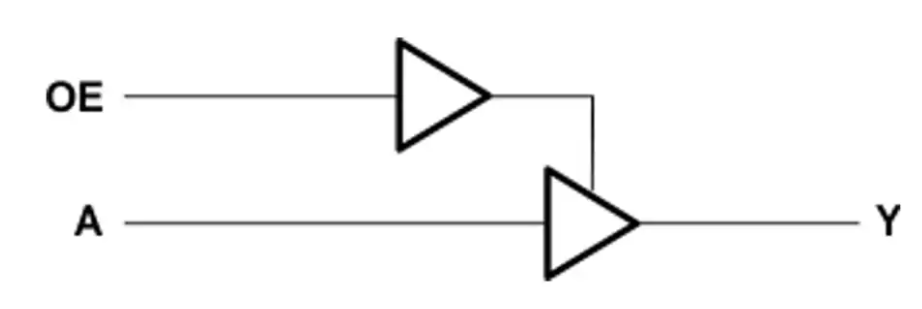

那这里就需要引入一个三态门结构电路。

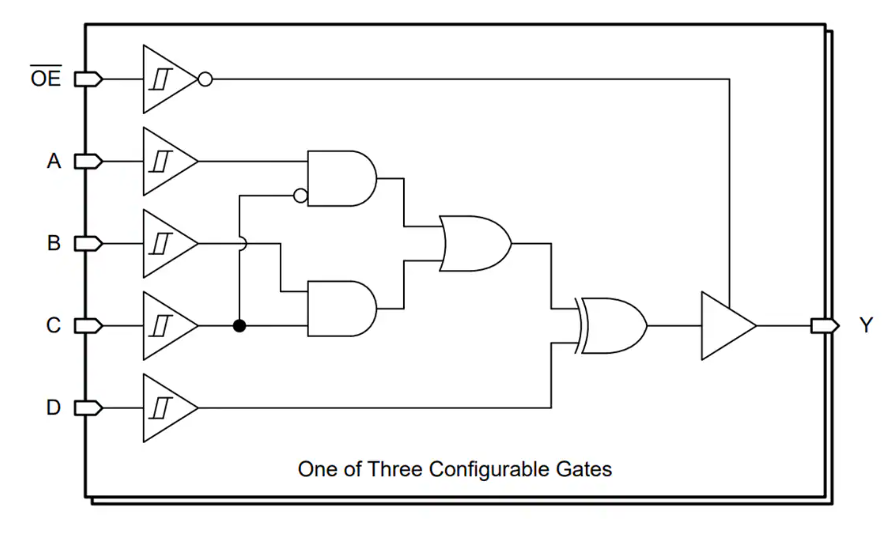

三态门结构

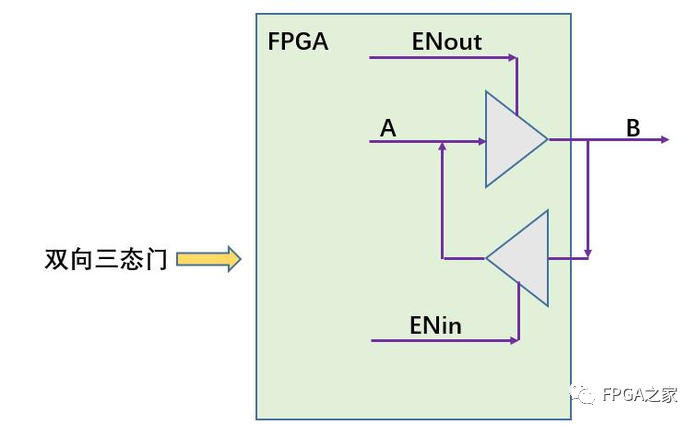

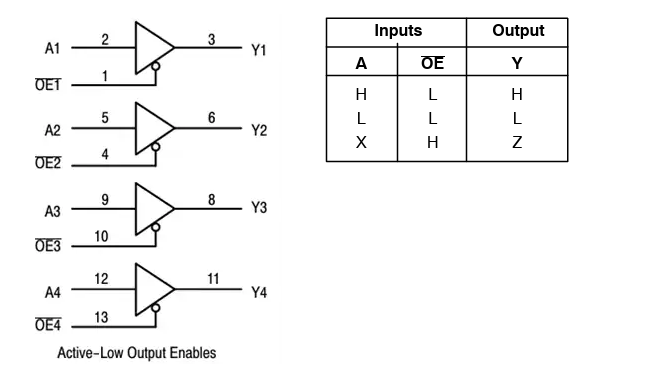

那么三态门的结构是怎样的呢?

三态门电路的输出结构和普通门电路的输出结构有很大的不同,因为它在电路中增加了一个输出控制端EN。

由上图看出,在单相三态门中,当EN=1时,对原电路无影响,电路的输出符合原来电路的所有逻辑关系,即A可以输出到B。当EN= 0时,电路内部的所有输出与外部将处于一种关断状态。

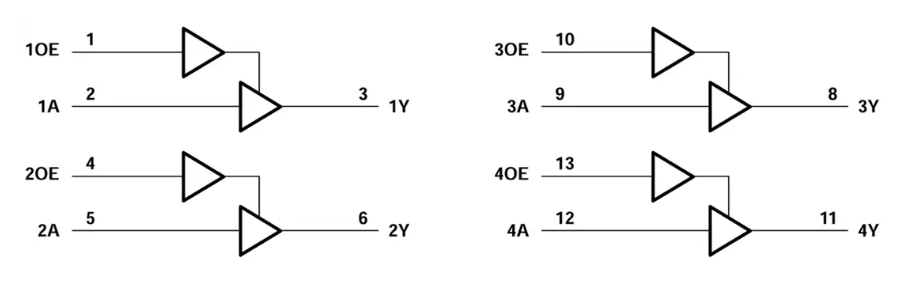

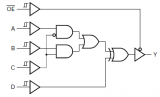

因此,当FPGA的信号线存在双向IO时,可以有两个三态门来控制,一个控制输出,一个控制输入,结构如下:

当ENout=1,ENin=0时,双向三态门的电路传输方向是A->B;

当ENout=0,ENin=1时,双向三态门的电路传输方向是B->A;

模型分析

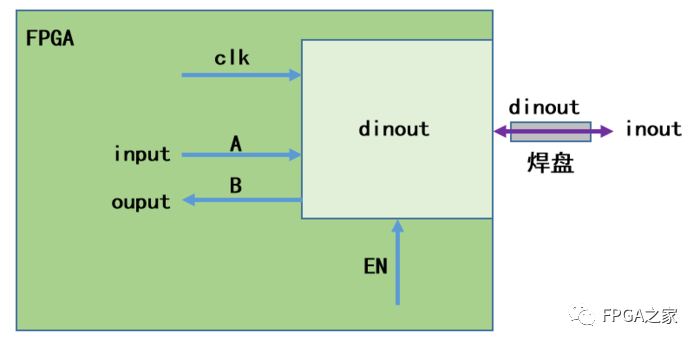

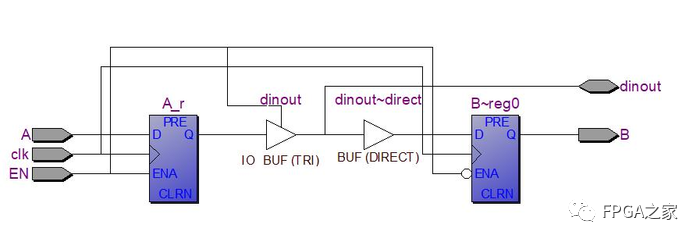

下面简单做个简易模型来说明双向IO如何分别实现作为输入端口和输出端口的功能,模块图如下:

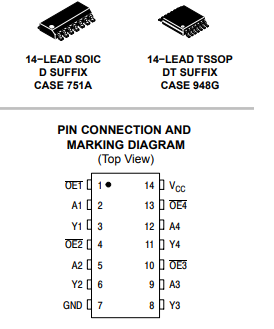

模型引脚定义

(1)输入口A定义:当双向端口dinout作为输出口时,我们将A端口输入数据传到模块中,让数据从dinout口出来。

(2)输出端口B定义:当当双向端口dinout作为输入口时,我们将dinout端口输入数据传到模块中,让数据从B口出来。

(3)EN控制信号定义:当EN=1时,开通三态门,将dinout作为输出口使用,当EN=0时,把三态门置为高阻态,这时dinout作为输入口用。

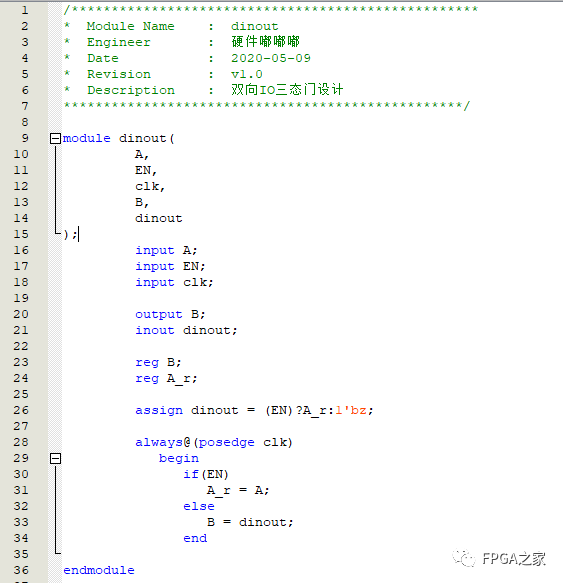

代码展示

编译分析后查看RTL视角逻辑电路,符合原有模型设计。

总结说明

(1)FPGA内部不允许传递双向IO信号,只有FPGA对外部才能定义为双向IO端口,即只有在顶层输出的信号才可以被赋值为高阻态。

(2)在结构化建模的过程中,一个模块一个功能的建模,当涉及到内部模块的端口是双向IO端口时,然后根据一个双向IO对应一个输入,一个输出和一个使能控制,把模块中双向IO的输出用输出端口代替,双向IO的输入用输入端口代替,引出使能信号,并把对应assign中赋值的高阻态z根据实际情况给出0或1,来解决FPGA内部双向IO连接问题。

审核编辑 :李倩

-

FPGA

+关注

关注

1655文章

22283浏览量

630285 -

电路

+关注

关注

173文章

6063浏览量

177476 -

信号线

+关注

关注

2文章

185浏览量

22160

原文标题:FPGA双向IO使用之三态门说明

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

八进制三态同相缓冲器/线路驱动器/线路接收器MC74HC244A和MC74HCT244A详解

MC74VHCT125A三态总线缓冲器技术深度解析与应用指南

SN74LV8T540 具有三态输出的 8 位固定方向电平转换器技术手册

SN74AHC126四路三态总线缓冲门技术解析与应用指南

SN74AHCT1G126 单总线缓冲门技术解析与应用指南

Texas Instruments SN74AC3G99/SN74AC3G99-Q1多功能门特性/应用/框图

中微爱芯推出可配置多功能逻辑门电路AiP74LVC1G99

复位时 FX3 引脚状态是怎样的?

AiP74LVC125带三态控制的4路缓冲器/线驱动器产品说明书

高速光耦在通信行业的应用(五) | 5Mbps通信光耦的特性

FPGA三态门的结构是怎样的呢?

FPGA三态门的结构是怎样的呢?

评论