PCIe 7.0最终版草案发布,传输速率128 GT/s,PCIe 6.0加速商业化

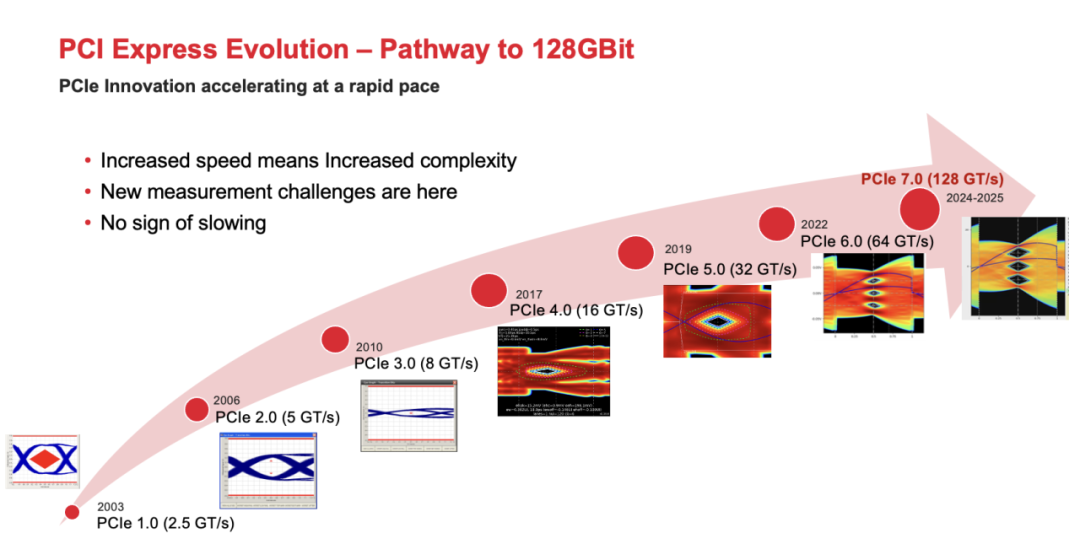

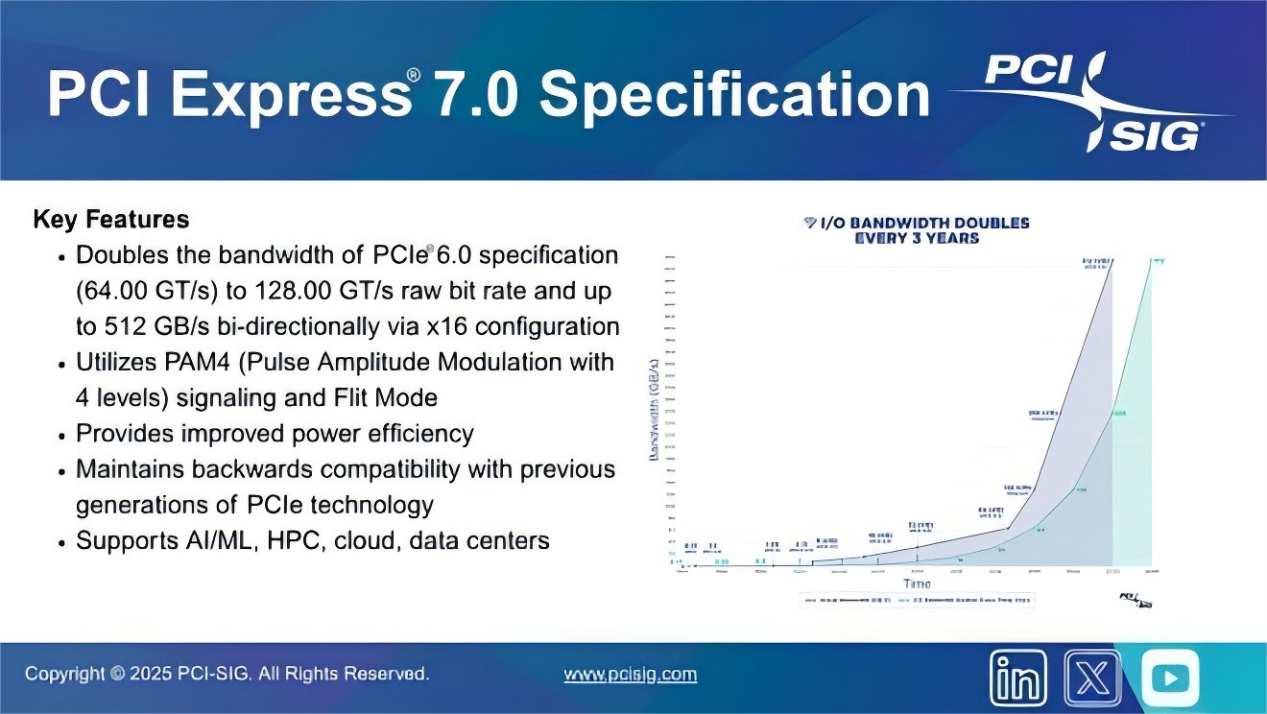

电子发烧友网综合报道,近日,PCI-SIG 组织公布了 PCI Express 7.0 规范的0.9 版草案,这是PCIe 7.0规范正式版本发布前的最后一个草案版本,而正式版将于2025年晚些时候发布。

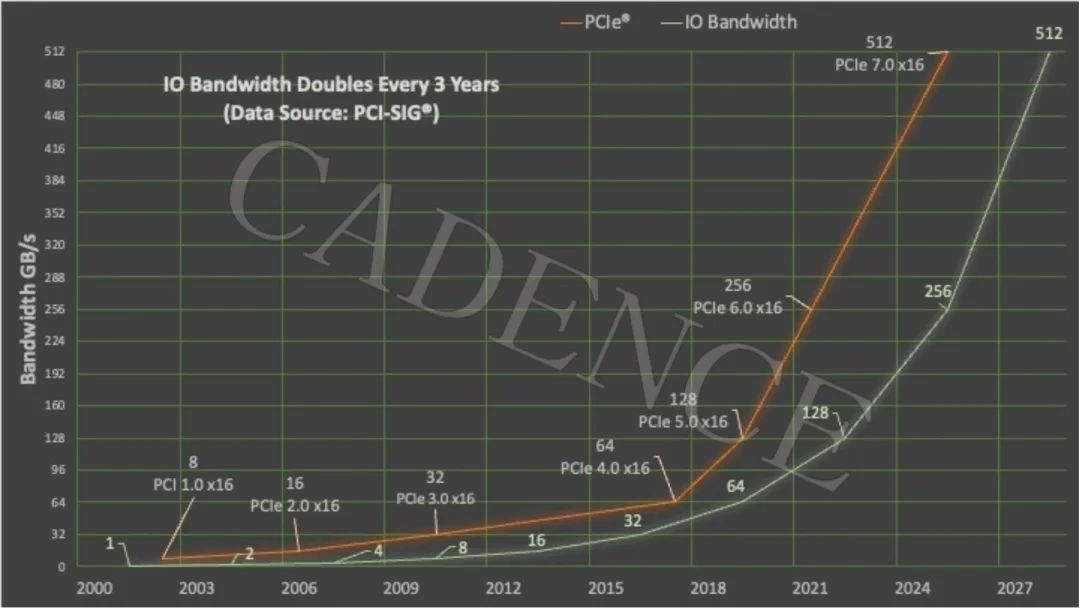

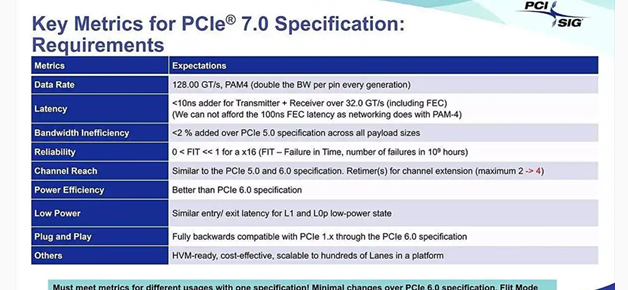

其核心技术参数目标包括:传输速率128 GT/s,x16 配置下双向带宽达 512 GB/s;采用四电平脉冲幅度调制(PAM4)技术;,优化信道设计参数,确保在更长的物理距离下仍能保持高数据传输速率和稳定性;继续改善低延迟性能,并强化系统的鲁棒性和数据传输的准确性,以适应对实时性和数据完整性要求极高的应用场景;优化功耗效率指标;以及继续向下兼容历代 PCIe 版本。

全新的PCIe 7.0 规范旨在支持数据密集型细分市场,例如超大规模数据中心、高性能计算 (HPC) 和军事/航空航天,以及 AI/ML、800G 以太网和云计算等新兴应用。该规范旨在为下一代计算设备提供更高带宽基础,满足日益增长的实时数据处理与高速互联需求。

在PCIG-SIG DevCon 2024开发者大会上,Cadence全球首次展示了PCIe 7.0的全新方向,加入自己独有的光学连接方案,在一个真实、低延迟、无需重定时、线性光学连接的系统中,跑出了128GT/s的收发速率。这就意味着,它的x16双向带宽可达512GB/s。

在PCI-SIG DevCon 2024 上,新思科技展示了全球首个基于光学的 PCIe 7.0 IP,展示了该技术在实际场景中的功能。其中包括使用 OpenLight 光子 IC 以 128 Gb/s 运行的 Synopsys PCI Express 7.0 PHY IP 电-光-电 (EOE) TX 到 RX,以及使用 Synopsys PCIe 7.0 控制器 IP 成功实现根复合体到端点的连接和 FLIT 传输。

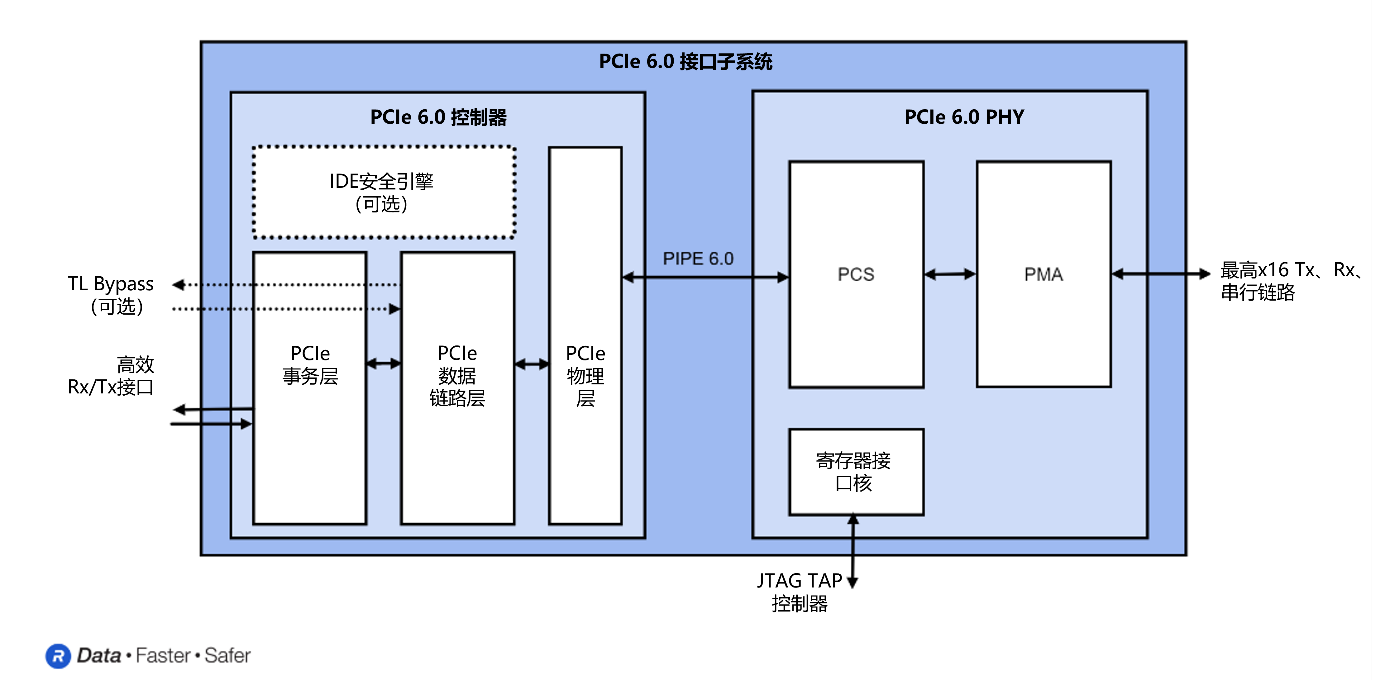

Rambus也在PCI-SIG DevCon上推出PCIe 7.0 IP 产品组合,PCIe 7.0 控制器旨在提供下一代 AI 和 HPC 应用所需的高带宽、低延迟和强大性能。主要特性包括支持 PCIe 7.0 规范,包括 128 GT/s 数据速率;实施低延迟前向纠错 (FEC) 以实现链路稳健性;支持固定大小的 FLIT,可实现高带宽效率;向后兼容 PCIe 6.0、5.0、4.0 等;借助 IDE 引擎实现最先进的安全性;支持 AMBA AXI 互连。此外,PCIe 7.0 重定时器,用于高度优化、低延迟信号再生数据路径;PCIe 7.0 多端口交换机具有物理感知能力,可支持多种架构。

随着数据传输速率的不断提高,传统的电气信号传输面临着信号衰减、干扰等问题,难以满足高速数据传输的需求。而光信号具有传输速度快、损耗低、抗干扰能力强等优点,因此将光学技术引入 PCIe 7.0 成为了解决高速数据传输问题的关键。早前,PCI-SIG组织就成立了专门的光学工作组,研究基于光学接口的PCIe新标准,但尚未确定PCIe 7.0是否一定采用光学方案。

当然从市场端来看,当前PCIe 5.0逐渐成为市场主流,PCIe 6.0的研发成果陆续推出,但落地商用还需要一段时间。

例如,去年在FMS 上,美光展示其领先的 PCIe 6.0 SSD 技术,其顺序读取带宽超过 26GB/s,为推动生态系统发展而设计。美光将向合作伙伴提供此项技术,以加速 PCIe 6.0 生态系统的发展。

在DesignCon2025大会上,Astera Labs演示了业界首个PCIe 6.0交换机与PCIe 6.0 SSD端点之间的互操作性,展示了其PCIe交换机与美光SSD配合使用时的能力。演示中使用的美光PCIe 6.0数据中心SSD实现了高达27GB/s的性能,远超 PCIe 5.0 的 14.5 GB/s,展示了 PCIe 6.0 在存储领域的巨大潜力。

PCIe 7.0最终版草案发布,传输速率128 GT/s,PCIe 6.0加速商业化

相关推荐

热点推荐

PCIe 6.0最新草案0.71版本发布,带宽翻倍,采用全新PAM4调制技术

每隔三四年都会更新一个版本。到目前为止,已经更新到了PCIe 6.0。 7月2日,PCI-SIG公布了最新的PCIe 6.0最新的草案0.71版本。与PCIe 5.0 相比,PCIe 6.0 再次实现了

2021-07-05 09:33:58 7082

7082

7082

7082硬盘开启PCIe 5.0时代

2019年年初,PCI-SIG组织对外发布PCIe 5.0 0.9版规范。随后,2019年5月29日,PCI-SIG正式宣布完成PCIe 5.0规范,传输速率达到32GT/s,带宽可达128GB/s

2021-09-29 08:48:07 6147

6147

6147

6147PCIe 5.0产品测试验证火热进行中,为未来引领消费者市场做好准备

/s ;到了刚发布的PCIe 6.0,实现了带宽速率全面翻倍,而且PCIe 6.0对底层信令进行了改进。 是德科技刚刚发布了针对PCIe 5.0/6.0的完整测试方案,至此能够提供全方位的物理层测试

2022-04-28 16:43:31 2505

2505

2505

2505

PCIe简介及引脚定义

2010年,PCIe 3.0 将数据速率提高到了 8.0 GT/s ,并采用了新的 128b/130b 编码机制,使每个引脚的带宽比 PCIe 2.0 翻了一番。新的编码机制通过采用三个随机位翻转检测的故障模型确保了高可靠性

2023-01-04 11:17:04 13155

13155

13155

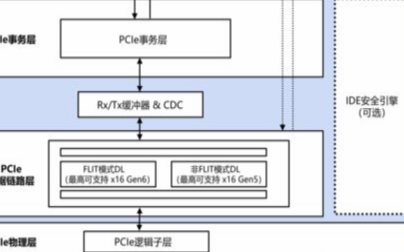

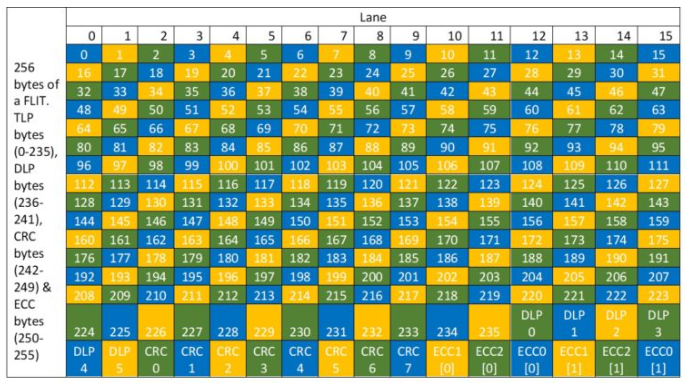

13155详解PCIe 6.0中的FLIT模式

PCIe 6.0 规范于 2021 年发布,采用 PAM4 调制(即 4 电平脉冲幅度调制),使数据传输速度翻倍,达到 64GT/s。同时,PCIe 6.0 规范使用 FLIT(流量控制单元)作为新的数据传输单元,显著提高了传输效率。

2025-02-27 15:44:34 3140

3140

3140

3140

是德科技PCIe 6.0发射机合规性测试解决方案

随着 PCIe 6.0 标准刚刚进入市场,PCI-SIG 组织已着手推动下一代标准——PCIe 7.0,预计将在 2025 年正式发布,持该标准的设备预计将在 2026 年问世,而大规模商用

2025-03-06 11:29:42 1520

1520

1520

1520

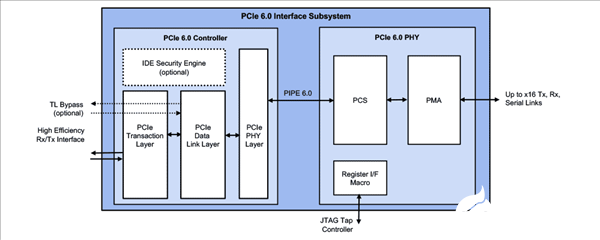

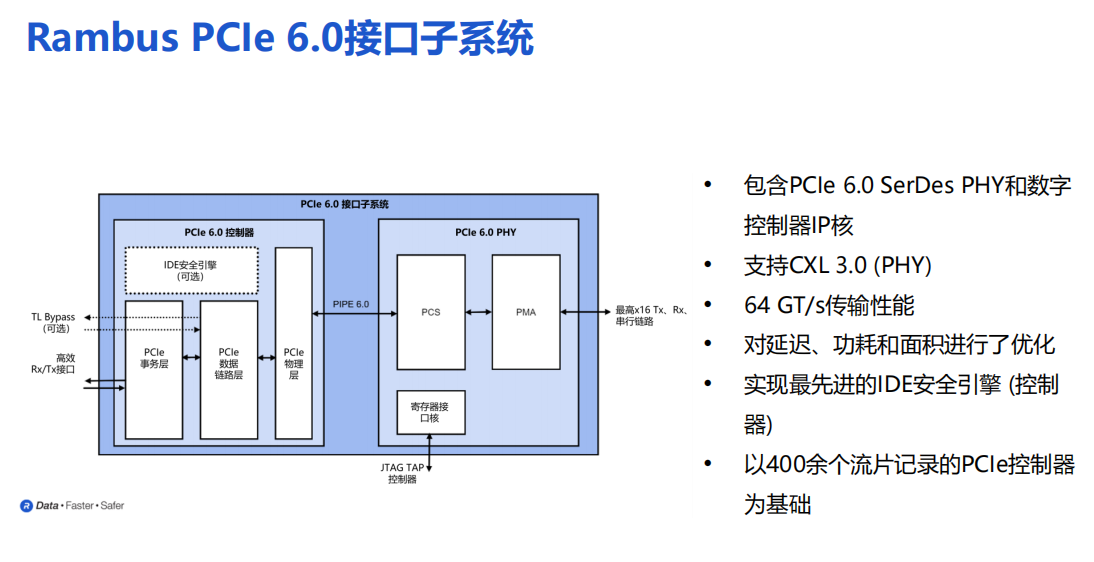

Rambus推出面向高性能数据中心和人工智能SoC的PCIe 6.0接口子系统

将高性能工作负载的数据传输速率提升至最高64 GT/s 支持PCIe 6.0的全功能,提供对CXL 3.0的PHY支持 对延迟、功耗和面积进行优化,提供完整的IP解决方案 提供最先进的安全性,保护

2022-12-01 13:39:25 832

832

832

832

解密PCle IP方案,让SoC集成更简单

是PCIe问世近20年来,变化最大的一次。 根据PCI-SIG的介绍,PCIe 6.0主要有三大变化:数据传输速率从32GT/s翻倍至64GT/s;编码方式从NRZ 信令模式转向PAM4信令模式;从

2023-01-31 09:23:22 3361

3361

3361

3361Samtec技术前沿 | 多重原因促使PCIe® 6.0采用了PAM4

,最新版本将PCIe® 5.0规范的 数据速率提高了一倍 ,并保持了 向后的兼容性 。 最新的PCIe® 6.0规范的主要特点包括: 01 64 GT/s数据速率,通过x16配置可达到 256Gbps;

2023-05-11 10:30:39 1453

1453

1453

1453

PCIe 6.0元年,AI与HPC迎来新速度

电子发烧友网报道(文/周凯扬)2022年1月,PCI-SIG发布了PCIe 6.0规范,正式拉开了接口带宽大幅升级的序幕。然而,在规范公布的两年时间里,也已经更新了6.0.1和6.1版本,PCIe

2024-01-31 09:02:24 4011

4011

4011

4011PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

将使速率在 PCIe 7.0 的基础上翻倍至 256.0 GT/s,通过 x16 配置实现 1TB/s 的双向带宽。 从 PCI-SIG 目前公布的细节来看,PCIe 8.0 首先实现了速度的提升

2025-08-08 09:14:19 7213

7213

7213

7213PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

电子发烧友网综合报道,早在2022年1月,PCI-SIG 组织正式发布了 PCIe 6.0 标准,与 PCIe 5.0 相比带宽再次翻倍,达到64 GT / s。 PCIe 6.0×16

2025-09-07 05:41:00 7946

7946

7946

7946

PCIe 8.0规范开发更新!

的 1.0 版本。 PCI Express 8.0 规范开发计划于今年8月公布,该标准将继续采用PAM4脉冲幅度调制信号技术,并在PCIe 7.0的基础上实现传输速率翻倍,达到每

2025-09-25 09:21:57 5711

5711

5711

5711

PCIe 3.0/4.0的链路均衡的工作原理

的16GT/s数据速率,再到PCIe 5.0的32GT/x。PCI-SIG组织实现了在速率翻倍的同时,仍能保持使用普通的FR4 板材 和廉价接插件,主要源自两个方面的改进,一是使用128b/130b编码来

2020-11-25 06:19:43

PCIe的SmartNIC如何改变方案加速规则

上的速率接近 1.25Gb/s,这种 8 通道(x8)PCIe 总线的诞生恰逢其时。 第一代 PCIe x8 总线在每个方向上的速率为 2GB。当时 16 通道( x16 )的插槽尚未问世,服务器主板一般

2021-01-07 17:31:57

化PCIe应用中的时钟分配方法

具有 16 G 每秒传输 (GT/s) 的比特率。第 4 代的规范预计将在 2014 或 2015 年发布。表 1:各代 PCIe 的数据吞吐量随着数据速率的提升,参考时钟需求也在不断提高。本文将重点

2018-09-17 16:12:25

Banana Pi BPI-W3 RK3588平台驱动调试篇 [ PCIE篇一 ] - PCIE的开发指南

= 2500MT/s = ( 2500 / 10 ) MB/s

PCIe gen3 x1 传输速率 8GT/s = 8000MT/s = ( 8000 / 130 ) x ( 128/8 ) MB/s

2023-11-02 09:31:28

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

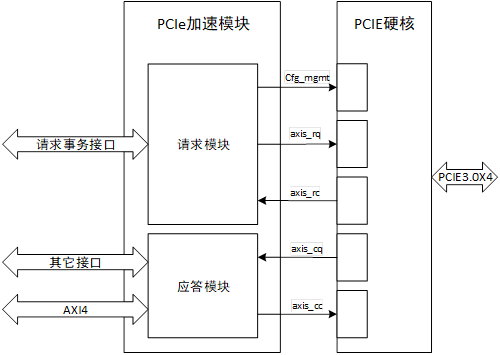

PCIe加速模块负责实现PCIe传输层任务的处理,同时与NVMe层进行任务交互。如图1所示,PCIe加速模块按照请求发起方分为请求模块和应答模块。请求模块负责将内部请求事务转化为配置管理接口信号或

2025-08-07 18:57:55

NVMe高速传输之摆脱XDMA设计之八:PCIe初始化状态机设计

初始化是PCIe总线正常进行数据传输的前提,图1为PCIe配置初始化状态机状态转移图。

图1 PCIe配置初始化状态机状态转移图

各状态说明如下:

IDLE:空闲状态,复位后的初始状态。当检测到初始化

2025-07-05 22:00:48

XCKU115板卡资料:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡

%。 五、散热系统 采用无风扇被动式散热。 六、应用领域 FPGA硬件加速。 七、接口测试软件DDR4 数据速率2400Mb/s IP测试。 PCIe 3.0 x8 IP测试。 程序加载测试。

2019-10-25 16:00:50

体验紫光PCIE之使用WinDriver驱动紫光PCIE

不同系列的PCIE IP并不通用,不同的系列都需要安装不同的PCIE IP包。

(3)参数配置,PCIE 的gen1是2.5GT/s,gen2是5GT/s,芯片集成的是gen2的硬核,所以选5GT/s

2023-11-17 14:35:30

基于PCIe DMA的多通道数据采集和回放IP

to Host)的全双工数据传输6.自适应PCIe链路速率:PCIe 1.0,PCIe 2.0,PCIe3.0和PCIe 4.0和宽度:PCIe x1,PCIe x2,PCIe x4,PCIex8

2020-11-25 22:27:25

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡解决方案

散热。六、应用领域FPGA硬件加速。七、接口测试软件DDR4 数据速率2400Mb/s IP测试。PCIe 3.0 x8 IP测试。程序加载测试。北京太速科技有限公司在线客服:QQ:448468544公司网站:www.orihard.com联系电话:***

2018-07-27 16:49:30

基于Xilinx XCKU115的半高PCIe x8硬件加速卡

。 支持PCIe x1、x4、x8模式。 支持2x72bit(数据位宽64bit+ECC)DDR4存储,数据传输速率2400Mb/s。 DDR4单簇容量4GB,总容量为8GB。 板载4个用户可编程LED

2018-08-22 17:31:55

如何优化PCIe应用中的时钟分配

(见表 1)。第 3 代 PCIe 引入了全新的编码方案,其可在不增加数据速率一倍的情况下,将数据吞吐量提升一倍。PCI-SIG 近期宣布推出的第 4 代 PCIe 具有 16 G 每秒传输 (GT/s

2022-11-22 08:04:25

嵌入式接口通识知识之PCIe接口

了显著提升。例如,PCIe 5.0版本的理论传输速率可达32 GT/s(每条信号槽传输32个Gbit/s)。PCIe接口具有向下兼容性,这意味着新版本的PCIe设备可以插入到旧版本的插槽中,并以较低

2025-08-21 16:51:24

请问GEN1 PCIE最高可配置2.5Gbps,这里说的最高传输速率是根据PCIE的协议制定的吗?

传输速率是根据PCIE的协议制定的吗?2.如果我设置的速率超过5.0Gbps可以吗?是否会出现数据的传输错误等现象?3.不太理解PCIE中关于x1和x2的含义,文档说PCIE是one single interface link,那么对于单个端口而言,x2的含义仅仅是代表速率是x1速率的一倍吗?

2018-06-19 04:36:26

力科PCIE 3.0系列文章之一——PCIE 3.0的发射机物理层测试

PCIE 3.0相对于它的前一代PCIE 2.0的最主要的一个区别是速率由5GT/s提升到了8GT/s。为了保证数据传输密度和直流平衡以及时钟恢复,PCIE 2.0中使用了8B/10B编码,即将每8位有效数据编码为10位

2012-12-03 11:45:13 57

57

57

57如何加速你的PCIe 4.0系统设计

的可靠性传输,热插拔以及服务质量(QOS)等功能。目前PCIe规范已经发布到3.0版本,并且在行业内得到了广泛采用,但是其功能特性还可以进一步提升。PCIe 4.0规范将于2017年初发布,其总线带宽是3.0版规范的2倍,数据传输速率将大幅提高,由8GTps增长

2017-02-08 04:18:09 1342

1342

1342

1342转向32GT/s速度的PCIe设计所面临的挑战

历史上,PCIe系统设计人员把通用低成本FR4 PCB材料和引线键合(wirebond)封装用于 高达 8GT/s 数 据 速率(Gen3)的大多数应用,这种做法已被证明是成功的。但是,在32GT/s的数 据速率下 使用 这 种材料 和封装并不可行。

2018-05-04 16:13:34 8301

8301

8301

8301

OSS发布业界首款五路PCIe4.0背板

去年10月底,PCIe 4.0标准正式诞生,传输速率翻番为16GT/s,x16规格可提供多达64GB/s的双向带宽。

2019-03-26 14:06:18 1441

1441

1441

1441PCIe 6.0将于明年发布最终正式版 I/O带宽再次加倍来到64GT/s

PCIe无疑是最为流行的传输总线标准,这几年的更新换代也十分频繁:PCIe 3.0目前还是最普及的,PCIe 4.0正在快速崛起,PCIe 5.0即将和大家见面,PCIe 6.0也正在快速推进制定中。

2020-02-24 11:31:25 5417

5417

5417

5417

Microchip发布PCIe5.0与CXL Retimer芯片

美国微芯(Microchip)发布了两款 Retimer 芯片,特点是支持 PCIe 5.0 的 32GT/s 链接速率。两款 XpressConnect 芯片的型号分别为 RTM-C 8xG5

2020-11-12 16:25:54 3215

3215

3215

3215硬盘PCIe 5.0时代即将来临

电子发烧友网报道(文/吴子鹏)2019年年初,PCI-SIG组织对外发布PCIe 5.0 0.9版规范。随后,2019年5月29日,PCI-SIG正式宣布完成PCIe 5.0规范,传输速率达到

2021-10-09 16:46:43 5698

5698

5698

5698楷登电子发布PCIe 6.0规范Cadence IP

中国上海,2021 年 10 月 22 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)宣布发布支持 TSMC N5 工艺的 PCI Express(PCIe)6.0 规范

2021-10-26 14:28:00 5070

5070

5070

5070PCI-SIG®发布PCIe®6.0规范以助力大数据应用

负责制定广为采用的PCI Express® (PCIe®)标准的组织PCI-SIG®今天宣布正式推出PCIe 6.0规范,传输速度达到64GT/s。 PCIe 6.0规范的特点 64GT/s原始数据

2022-01-13 09:32:20 5438

5438

5438

5438泰克提供业界首创的 PCIe 6.0 测试解决方案

在 PCI-SIG工作组发布PCIe 6.0 基本规范和验证要求仅几周后,全球测试与测量领导者泰克公司推出了业界首个基于最新规范PCIe 6.0的发射器测试解决方案。

2022-02-21 10:11:46 1513

1513

1513

1513Rambus PCIe 6.0控制器的主要特性

高性能应用提供高达每秒64GT的数据传输速率。此外,该控制器还提供最先进的安全性,其完整性和数据加密(IDE)引擎可以监控和保护PCIe链路免受物理攻击。

2022-03-10 11:26:20 2345

2345

2345

2345

PCIe 6.0的新变化与新挑战

2022年1月11日,PCI-SIG正式发布了PCI Express(PCIe) 6.0最终版本1.0,标志着各大IP、芯片厂商可以开始着手设计、开发自己技术和产品了。从技术上来说,PCIe 6.0是PCIe问世近20年来,变化最大的一次。

2022-04-13 13:50:55 6305

6305

6305

6305是德科技发布端到端PCIe5.0/6.0测试解决方案

2022年4月14日,北京――是德科技(NYSE:KEYS)发布新款端到端的 PCIe5.0/6.0 测试解决方案,使工程师能够对 PCIe 前沿科技设计进行仿真、研发、评估、验证和一致性测试。

2022-04-14 14:39:08 2316

2316

2316

2316PCIe 6.0规范及它是如何从过去的规范演变而来的

虽然与前几代相比,PCIe 6.0 的变化很大,但业界对其采用有着强大而广泛的支持。PCIe 在每个现代计算架构中无处不在,您应该期望 PCIe 6.0 将在高性能计算和云计算空间、企业存储和网络空间以及新兴应用程序(如 AI/机器学习和汽车。

2022-06-01 17:15:50 3237

3237

3237

3237

使用多代 PCIe 构建高性能互连

®) 已成为参考的高性能互连。利用高速串行通信,PCIe 提供高效的点对点连接,并通过增加通道数和信号传输速率,提供可扩展的接口带宽。 PCIe 1.0 规范于 2002 年发布,以每秒 2.5 千兆传输

2022-07-21 09:59:41 2489

2489

2489

2489

PCIe 7.0发布,速度高达512 GB/s

PCIe 7.0 接口将继续使用 1b/1b flit 模式编码和随 PCIe 6.0 引入的 PAM4 信号技术,这与PCIe 3.0 到PCIe 5.0 规范中使用的 128b/130b 编码

2022-07-28 15:11:54 1865

1865

1865

1865PCIe发展历程与相关概念

传输速率为每秒传输量GT/s,而不是每秒位数Gbps,因为传输量包括不提供额外吞吐量的开销位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b编码方案,导致占用了20% (= 2/10)的原始信道带宽。

2022-08-02 09:45:34 2662

2662

2662

2662PCIe吞吐量(可用带宽)计算方法

PCIe 3.0协议支持8.0GT/s,即每一条Lane上支持每秒钟传输8G个Bit。而PCIe 3.0的物理层协议中使用的是128b/130b编码方案,即每传输128个Bit,需要发送130个Bit。

2022-08-29 16:09:17 4901

4901

4901

4901Rambus推出全球首个PCIe 6.0接口子系统 面向大数据与AI领域

6.0被认为该标准诞生19年来最具革命性的一次飞跃,不仅数据传输率再次翻番最高可达64GT/s,x16单向带宽128GB/s、双向带

2022-10-27 10:06:23 1355

1355

1355

1355

PCIe 5.0:加速云中的数据移动

,并于 2019 年底随着 AMD EPYCTM 7002(罗马)处理器的推出在主流服务器中首次亮相。PCIe 4.0 将车道速度提高一倍,达到 16 GT/s。

2022-11-21 17:08:27 1352

1352

1352

1352PCIe 6.0有啥用?

PCIe 6.0被认为该标准诞生19年来最具革命性的一次飞跃,不仅数据传输率再次翻番最高可达64GT/s,x16单向带宽128GB/s、双向带宽256GB/s,更是升级为1b/1b编码的PAM4脉冲调制。

2022-11-23 15:51:30 2005

2005

2005

2005PCIe传输速率和有效带宽计算方式

受委托让我整理一个关于PCIe的主题分享文章,半月有余实在没办法交差,首先,我自己本身,对PCIe并没有做到胸有成竹,我的PCIe知识也只是停留在理论阶段,我并没有实际做过任何有关PCIe的东西

2022-11-28 10:25:52 8877

8877

8877

8877干货:PCIE6.0技术剖析

关于PCIe6.0 你需要知道的都在这里 从正式发布至今,PCI Express(PCIe)发展迅速,已经成为高性能计算、人工智能/机器学习(ML)加速器、网络适配器和固态存储等应用不可或缺的一项

2022-12-07 07:40:08 7227

7227

7227

7227数据传输速率大幅提升,PCIe 6.0开启数据中心/人工智能新纪元

速率增加幅度也非常显著。每次推出一个全新版本的PCIe,它的数据传输速率对比上一代基本就是翻倍的。比如PCIe 6.0和上一代的5.0是64GT/s到32GT/s每秒的双倍提升。 今年年初,PCIe 6.0的规范和标准已经正式提出,Rambus随及发布了PCIe 6.0控制器的相关产品。现在

2022-12-14 11:22:10 3779

3779

3779

3779

如何破解PCIe 6.0带来的芯片设计新挑战?

本文转载自《半导体行业观察》 感谢《半导体行业观察》对新思科技的关注 PCI Express (PCIe) 6.0规范实现了64GT/s链路速度,还带来了包括带宽翻倍在内的多项重大改变,这也为SoC

2023-01-19 16:50:05 1630

1630

1630

1630如何破解PCIe 6.0带来芯片设计新挑战?

PCI Express (PCIe) 6.0规范实现了64GT/s链路速度,还带来了包括带宽翻倍在内的多项重大改变,这也为SoC设计带来了诸多新变化和挑战。对于HPC、AI和存储SoC开发者来说,如何理解并应对这些变化带来的设计挑战变得至关重要。

2023-02-03 10:23:44 2455

2455

2455

2455FPGA PCIe加速卡开源硬件及例程介绍

基于Xilinx Artix-7系列FPGA芯片设计的M.2 M-Key FPGA加速卡,引出Artix7-484脚芯片的4条高速GT,最高支持PCIE2.0*4速率。

2023-03-24 09:13:17 7086

7086

7086

7086业界首个64 GT/s连接:PCIe 6.0新突破让数据传输再提速

能就会越出色。让这一切成为可能的则是去年发布的PCI Express(PCIe)6.0规范。 与PCIe 5.0相比,PCIe 6.0支持的数据传输速率再次翻倍 ── 64 GT/s。数据传输速率越快,也就意味着高性能计算(HPC)、AI推理引擎、云端软件等应用以及数据中

2023-03-29 02:25:04 1594

1594

1594

1594PCIe 6.0入门之什么是 PCIe 6.0

PCI Express® 6.0 (PCIe® 6.0) 规范由 PCI-SIG® 于 2022 年 1 月发布。最新一代的 PCIe 标准带来了许多激动人心的新功能,旨在提高计算密集型工作负载的性能,包括数据中心、 AI/ML 和 HPC 应用程序

2023-05-22 17:27:51 8967

8967

8967

8967

验证PCIe 6.0中的轻量级前向纠错和强循环冗余校验功能

PCIe 6.0 使用数据速率为 4GT/s 的 PAM-64 信令,而不是以较低数据速率使用的不归零 (NRZ) 信令。这意味着发送和接收的信号现在将在一个单位间隔内具有四个不同的电压电平(2位

2023-05-25 16:06:38 4968

4968

4968

4968

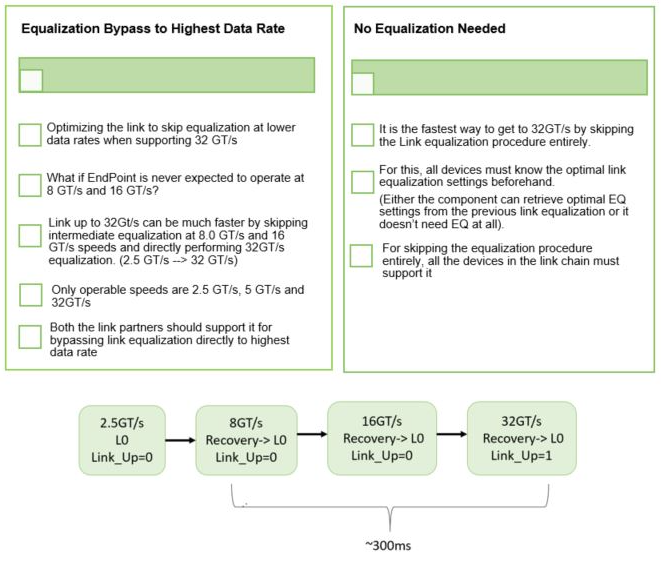

PCIe 5.0均衡模式:缩短链路启动时间

5.0 的传输速率为每秒 32 千兆传输 (GT/s),而 PCIe 16.4 支持的传输速率为 0 GT/s。PCIe 64.5 具有每秒 0 千兆字节 (GB/s) 的单向传输带宽,以 128 GB/s 的双向流量提供数据。

2023-05-26 10:23:14 3219

3219

3219

3219

PCIe 7.0标准新进展,速度达到16GB/秒/单通道

随着PCI Express 6.0 于去年初完成,PCI-SIG 迅速开始着手开发下一代 PCIe 7.0,这在去年的开发者大会上宣布。针对 2025 年的发布,PCIe 7.0 的目标是再次将

2023-06-19 15:24:58 2974

2974

2974

2974

【虹科新品】10 GSample/s速率、12位分辨率和12.8 GByte/s——虹科全新PCIe数字化仪

和12位垂直分辨率,其传输速度更是达到行业领先的12.8GB/s(通过PCIe总线)。为实现最佳流速率,虹科数字化仪融合了16通道、Gen3和PCIe技术。数据采集后

2023-03-30 10:40:48 1665

1665

1665

1665

浅析PCIe标准和布线的开发

PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一个PCIe 7.0 x16通道可以支持512 GB

2023-06-21 11:32:14 1450

1450

1450

1450

PCIe的基础知识整理

PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一个PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 1764

1764

1764

1764

Cadence 于 2023 PCI-SIG 开发者大会期间展示 PCIe7.0-Ready IP

期间,PCI-SIG 宣布,PCI Express(PCIe)7.0 规范已达到 0.3 版。这意味着数据传输速率进一步翻倍并达到 128GT/s。该标准预计将于 2025 年最终确定。 PCIe 标准大约每三年将

2023-06-28 12:20:01 1261

1261

1261

1261

AI和数据中心:PCIe 6.0,你是懂加速的

)6.0在AI、HPC和数据中心中越来越受欢迎。PCIe 6.0运行速度极快,达到64GT/s,是上一代的两倍。目前,网络服务器、固态驱动器、交换机和AI加速器都已率先采用PCIe 6.0,网络接口卡(NIC)和CPU主机芯片也即将采用该标准,但开发者该如何知道PCIe 6.0是否适合进行下一款芯

2023-07-12 17:50:01 7869

7869

7869

7869PCIe®标准演进历史

PCIe 标准之间的主要差异。 PCIe 3.0 PCIe2.0的传输速率为5 GT/s,但由于8b/10b编码方案的开销占比为20%,因此单lane的传输带宽为4Gb/s。PCIe 3.0及以后

2023-07-26 08:05:01 2655

2655

2655

2655

PCIe 6.0的优化设计方案探讨分析

为了实现64GT/s的链路速度,PCIe 6.0采用脉冲幅度调制4级 (PAM4) 信号,在与32GT/s PCIe相同的单元间隔(UI)中提供4个幅度级别(2 位)。图1显示了三眼眼图与此前的单眼眼图的对比。

2023-08-05 09:33:13 1848

1848

1848

1848

新思科技PCIe 6.0 IP与英特尔PCIe 6.0测试芯片实现互操作

:SNPS)近日宣布,新思科技PCI Express(PCIe)6.0 IP在端到端64GT/s的连接下,成功实现与英特尔PCIe 6.0测试芯片的互操作性。这一全新里程碑也将保证,在未来无论是集成

2023-10-12 15:11:45 922

922

922

922新思科技成功实现与英特尔PCIe 6.0测试芯片的互操作性

新思科技PCIe 6.0 IP与英特尔 PCIe 6.0测试芯片实现互操作 在64GT/s 高速连接下成功验证互操作性,降低高性能计算SoC的集成风险 新思科技近日宣布,新思科技PCI

2023-10-16 09:22:56 1536

1536

1536

153611月24日|泰克云上大讲堂—PCIe测试面面观

数据密集型市场的重要且可扩展的标准,其主要进步包括带宽和能效比上一版本提高了一倍,原始数据传输率从5.0的32GT/s提高到6.0的64GT/s。 content 本期直播预告 本期云上大讲堂,将由 泰克高级应用工程师 李煜 为大家带来: ■ PCIe最新进展和6.0介绍 ■ PCIe For

2023-11-16 16:30:01 1050

1050

1050

1050

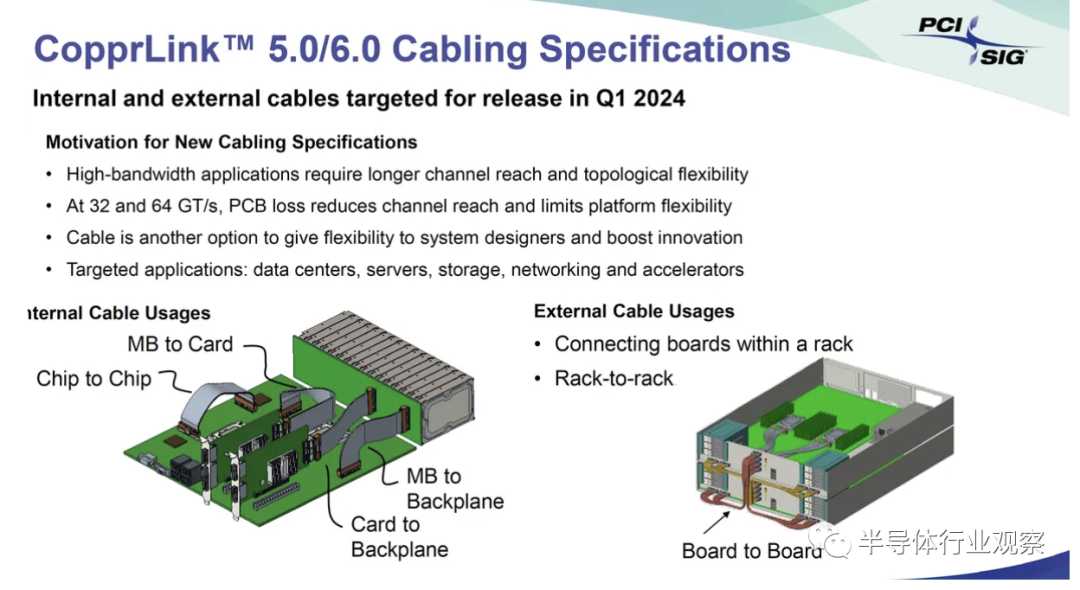

PCIe:用CopprLink取代OCuLink?

PCI SIG 本周表示,它正在开发 PCIe 5.0 和PCIe 6.0接口的布线规范,数据传输速率为 32 GT/s 和 64 GT/s。

2023-11-16 17:43:19 3647

3647

3647

3647

PCIE相关概念和带宽计算方法

传输速率为每秒传输量GT/s,而不是每秒位数Gbps,因为传输量包括不提供额外吞吐量的开销位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b编码方案,导致占用了20% (= 2/10)的原始信道带宽。

2024-01-16 14:42:02 3614

3614

3614

3614

下一代PCIe5.0 /6.0技术热潮趋势与测试挑战

迫切。 一、PCIe 5.0 /6.0技术升级 1)信号速率方面 从PCIe 3.0、4.0、5.0 到 6.0,数据速率翻倍递增,6.0支持64GT/s,16路双向传输带宽可达256GB/s。 图1

2024-03-06 10:35:33 2709

2709

2709

2709

Samtec技术前沿 | 高达128 GT/s :全新概念验证型高速电缆解决方案性能

摘要/前言 即将发布的PCIe® 7.0 规范旨在实现128 GT/s的数据传输速率。它延续了PCIe 每一代产品速度翻番的趋势。根据 PCI-SIG的说法,"PCIe 7.0 技术的目标是为人

2024-03-22 13:42:03 1041

1041

1041

1041

新思科技推出业界首款PCIe 7.0 IP解决方案

PCIe 7.0 IP解决方案,加速万亿参数领域的芯片设计 新思科技推出业界首款完整的PCIe 7.0 IP解决

2024-06-29 15:13:32 1360

1360

1360

1360如何简化PCIe 6.0交换机的设计

由于全球数据流量呈指数级增长,PCIe 6.0 交换机的市场需求也出现了激增。PCIe 6.0 交换机在高性能计算(HPC)系统(尤其是数据中心)中为需要大带宽和超低延迟的应用提供了重要的数据传输

2024-07-05 09:45:18 1455

1455

1455

1455

pcie4.0和pcie3.0接口兼容吗

速率、通道数量、功耗等方面有所不同。 PCIe 3.0是PCIe总线的第三个版本,于2010年发布。它的最大传输速率为8 Gbps,支持最多32个通道。PCIe 3.0在功耗、兼容性等方面进行了优化,使

2024-07-10 10:12:09 15332

15332

15332

15332pcie4.0插在3.0的主板上会怎么样

PCIe 1.0:2003年推出,数据传输速率为2.5 GT/s。 PCIe 2.0:2007年推出,数据传输速率提升至5 GT/s。 PCIe 3.0:2010年推出,数据传输速率

2024-07-10 10:16:23 11448

11448

11448

11448新思科技PCIe 7.0验证IP(VIP)的特性

在近期的博文《新思科技率先推出PCIe 7.0 IP解决方案,加速HPC和AI等万亿参数领域的芯片设计》中,新思科技宣布推出综合全面的PCIe Express Gen 7(PCIe 7.0)验证IP(VIP)解决方案,以支持高性能计算设计中人工智能(AI)应用所需的高速度和低延迟。

2024-07-24 10:11:23 2230

2230

2230

2230

PCIe 5.0 SerDes 测试

的吞吐量较上一代 PCIe 4.0 增加一倍。需要注意的是 PCIe 原始传输速率的单位是 GT/s ,而链路数据速率的单位是 Gb/s。 表 1:五代 PCIe 的对比表 需要注意,编码方案从

2024-08-16 09:33:05 2909

2909

2909

2909

Cadence展示完整的PCIe 7.0 IP解决方案

十多年来,Cadence 对 PCIe 技术的坚定承诺和支持,在业界有目共睹。我们深知强大 PCIe 生态系统的重要性,并感谢 PCI-SIG 提供的平台。在 PCI-SIG 开发者大会迎来 32 周年之际,Cadence 宣布面向 HPC/AI 市场推出完整的 PCIe 7.0 IP 解决方案。

2024-08-29 09:14:57 1716

1716

1716

1716

PCIe 4.0与PCIe 3.0的性能对比

4.0相较于PCIe 3.0,最直观的提升就是带宽的增加。PCIe 3.0的单通道带宽为8 GT/s(Giga Transfers per second),而PCIe 4.0的单通道带宽提升至16 GT

2024-11-06 09:22:07 18935

18935

18935

18935PCIe的最新发展趋势

1. PCIe 5.0和6.0的推出 PCIe 5.0和6.0是最新的PCIe标准,它们提供了更高的数据传输速率。PCIe 5.0的数据传输速率可达32 GT/s,而PCIe 6.0则进一步提升

2024-11-06 09:35:08 2343

2343

2343

2343pcie接口类型及其应用

现代计算机系统中不可或缺的一部分。 PCIe接口的发展历程 PCIe接口自2003年推出以来,已经经历了多次迭代和升级。从最初的PCIe 1.0,到现在的PCIe 5.0,数据传输速率从2.5 GT

2024-11-13 10:22:38 5795

5795

5795

5795如何检查pcie插槽兼容性

不同的版本和通道宽度,这决定了数据传输速率和带宽。以下是一些常见的PCIe插槽规格: PCIe 1.0 :2.5 GT/s 数据传输速率,x1、x4、x8 和 x16 通道宽度。 PCIe 2.0 :5

2024-11-13 10:30:53 9006

9006

9006

9006pcie 4.0与pcie 5.0的区别

发展到了第五代。 一、带宽和数据传输速率 PCIe总线的一个关键特性是其带宽,即数据传输速率。PCIe 4.0的带宽是PCIe 3.0的两倍,达到了每通道16 GT/s(Giga Transfers

2024-11-13 10:35:28 20173

20173

20173

20173PCIe 4.0与3.0的区别 PCIe设备的故障排除方法

规范的第四代,而PCIe 3.0是第三代。它们之间的主要区别如下: 带宽与速率 : PCIe 4.0提供了高达16 GT/s(千兆传输率/秒)的双向吞吐量,这意味着其理论最大带宽为32 GB/s(千兆

2024-11-26 15:12:49 9782

9782

9782

9782如何选择适合的PCIe配置

,帮助您做出合适的选择: 一、了解PCIe版本与性能 PCIe版本 :PCIe 4.0相比PCIe 3.0在带宽方面有了显著提升,提供了高达64GB/s(理论最大值,实际可能因设备差异而有所降低)的传输

2024-11-26 16:10:26 2136

2136

2136

2136PCIe 7.0 互连— PCIe的尽头会是光吗?

批准 Draft 0.5版基础规范,目前0.7版本基础规范正在审核中,预计2025年敲定最终发行版本。 PCIe 7.0 规范包括以下功能目标: 通过 x16 配置提供 128 GT/s 原始比特率和高达 512 GB/s 的双向比特率。 利用 PAM4信令, 以实现更高效的信号传输和更高的数据吞吐量

2025-02-10 10:03:37 790

790

790

790

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

PCIe加速模块负责实现PCIe传输层任务的处理,同时与NVMe层进行任务交互。PCIe加速模块按照请求发起方分为请求模块和应答模块。

2025-08-09 14:38:41 4629

4629

4629

4629

PCIe 7.0 Samtec已为您准备好N种互连解决方案

摘要前言 今年4月,PCIe 7.0 0.9 版本已向 PCI-SIG成员 开放。 PCIe 7.0相比PCIe 6.0 带宽提升一倍 ,原始比特率达到 128 GT/s 。PCIe 7.0满足了

2025-09-04 11:38:29 1547

1547

1547

1547

PCIe 7.0技术细节曝光

6 月 11 日 PCI SIG官宣 PCI Express 7.0(PCIe 7.0)规范最终版已制定完毕,但几乎没有公开任何技术细节。不过,在 7 月 16 日,PCI-SIG 通过 BrightTalk 公开了一些更详细的技术信息,下面就为大家介绍这些内容。

2025-09-08 10:43:13 2510

2510

2510

2510

PCI11010 PCIe交换机技术解析与应用设计指南

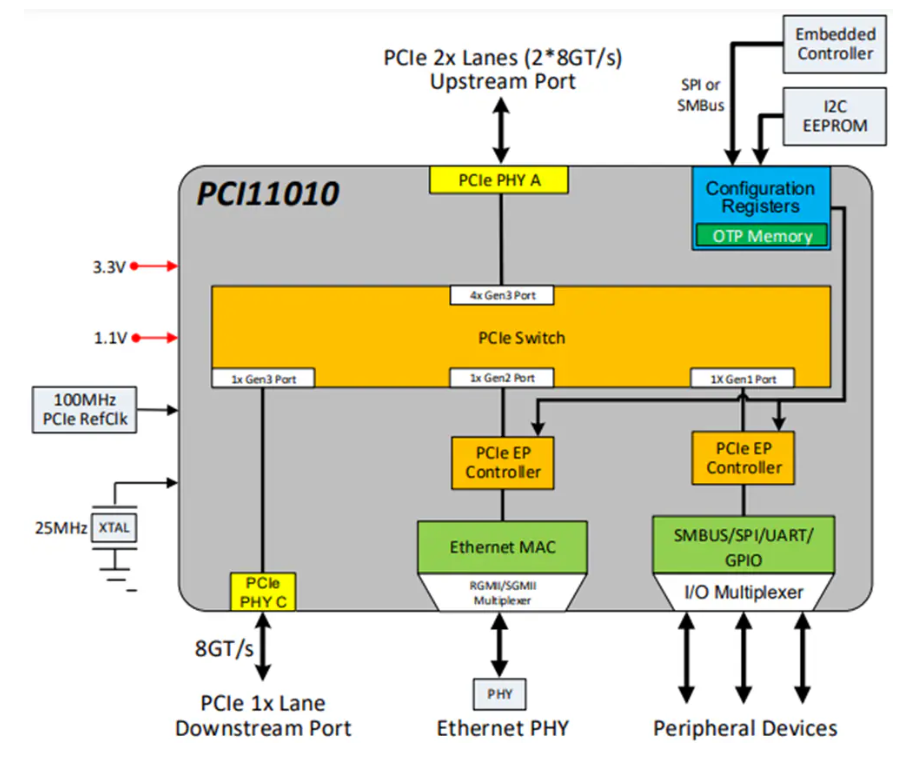

PCI11010具有2通道(2x8GT/s)上行端口和1通道(1x8GT/s)下行端口,最大线路速率为8GT/s。 该器件符合PCIe修订版4.x规范,专为增强嵌入式应用中的PCIe子系统而设计。它支持灵活的PCIe上行配置,并确保所有外部和内部接口的合规性。

2025-10-10 14:03:41 582

582

582

582

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

电子发烧友网报道(文/黄晶晶)PCIe 5.0作为新一代高速接口标准,其带宽大幅提升至32 GT/s,相较于PCIe 4.0翻了一番。这种高效的数据传输能力使得PCIe 5.0在处理高质量图像、游戏

2025-01-27 00:03:00 6473

6473

6473

6473PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

里程碑,其核心目标是通过光纤传输解决铜缆在高速率下的物理限制,同时保持与现有 PCIe 生态的兼容性。 PCIe 7.0 带宽翻倍 2022 年 6 月,PCI-

2025-06-13 00:07:00 7161

7161

7161

7161

电子发烧友App

电子发烧友App

评论