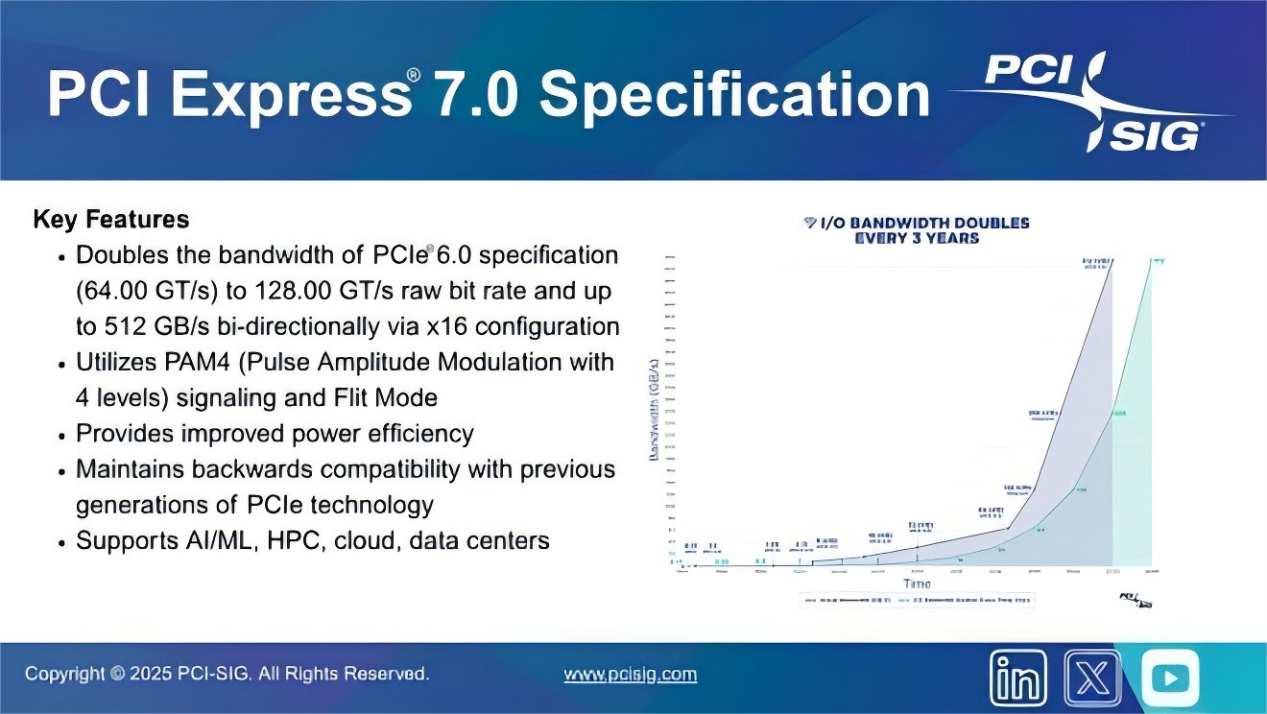

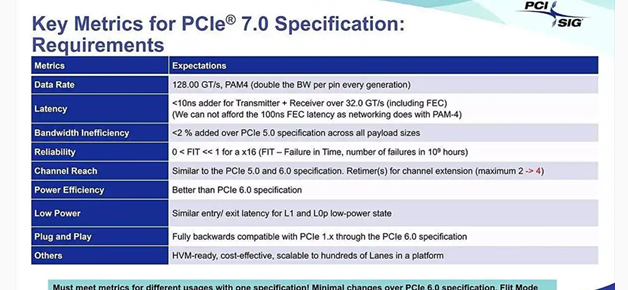

伴随大语言模型和相关训练系统迅猛增长、对非结构化数据处理的需求急剧上升,市场对算力的需求也是呈指数级增加。PCIe作为计算机和服务器中使用广泛的高速数据传输技术发展迅猛,今年4月份PCI-SIG已经批准 Draft 0.5版基础规范,目前0.7版本基础规范正在审核中,预计2025年敲定最终发行版本。PCIe 7.0 规范包括以下功能目标:

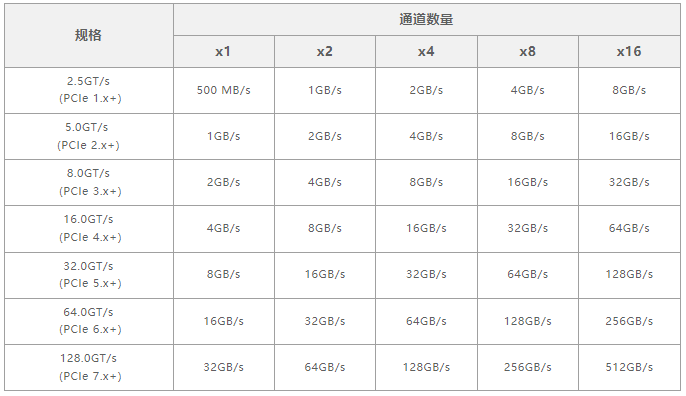

通过 x16 配置提供 128 GT/s 原始比特率和高达 512 GB/s 的双向比特率。

利用 PAM4信令, 以实现更高效的信号传输和更高的数据吞吐量。

关注通道参数和覆盖面, 以优化数据传输的质量和距离。

持续实现低时延和高可靠性的目标。

提高电源效率。

保持与所有前几代 PCIe 技术的向后兼容性。

PART. 01

传输技术的挑战

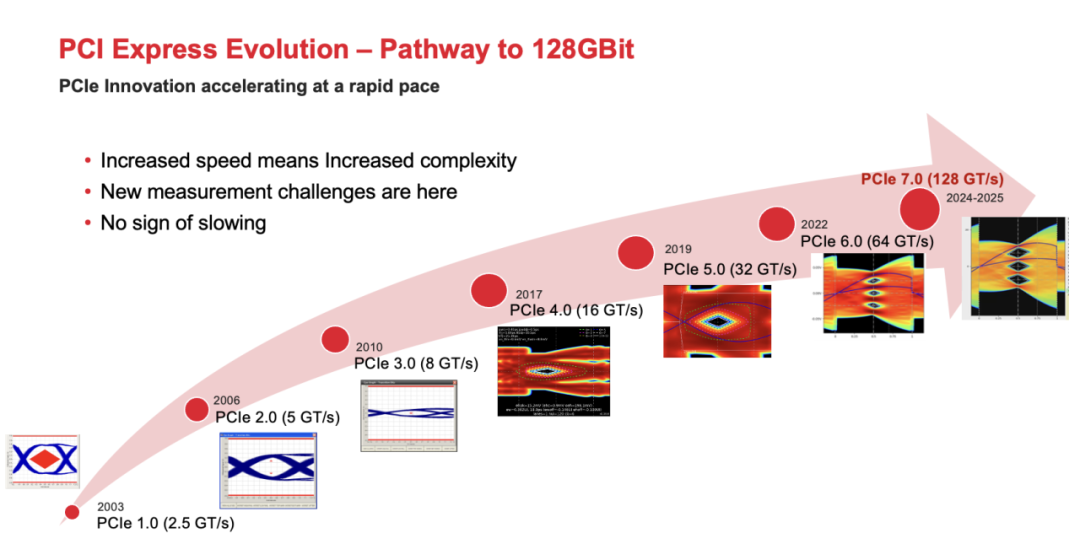

PCIe技术历经Gen1-Gen6,已经发展到单 Lane 128G的传输速率,超高速的传输速率带来了巨大挑战,协会不得不加入越来越多、越来越复杂的辅助机制,控制信号和数据完整性。接下来探讨未来PCIe 7.0 光传输技术的必要性及其挑战。

1

计算资源限制

面向超大集群、超轻边缘的两极分化的数据中心新场景,未来计算将突破冯诺依曼架构瓶颈,计算、存储和通信等模块通过统一总线对等互联,而PCIe作为数据中心服务器间互联的主力,承担着高速数据传输的重任。数据中心中的计算密集型任务,对内存带宽和利用率提出了更高要求。当前,大部分数据中心仍依赖本地内存,这不仅限制了数据处理的速度,还导致内存资源的利用效率低下。光传输方案则可以实现计算资源实现分散化,通过使处理单元能够访问更多分布在不同服务器单元或机架中的内存单元(跨服务器,跨机架访问),进而释放高度本地化且经常未使用的本地内存,使数据中心能够更高效地配置资源。

2

电信号传输距离受限

大语言模型的快速迭代离不开海量GPU集群的强劲支持。目前而言,这个海量已经来到了千卡万卡级别,集群之间的互连通常是基于GPU上原生的PCIe接口。就PCIe 技术而言,PCIe 1.0时,铜缆传输距离为10米,而发展到PCIe 5.0时,这一距离缩短至1-2米;当速率进一步提高到64 GT/s和128 GT/s,也即PCIe 6.0和未来的PCIe 7.0,铜缆传输距离将进一步缩短至几十厘米,几乎无法通过PCIe标准的铜缆实现机架间数十米的传输要求。再加上PCIe技术需考虑到重定时器的使用,其技术复杂、昂贵又耗电。且随着PCIe技术升级,传输距离缩短,所需要的retimer的数量也会越来越多,还会引入更多的功耗和时延。而光连接通过光纤传输信号,可以在极高带宽下保持信号的完整性和稳定性。不仅可以显著提升数据传输速度,还能降低数据传输的延迟。

3

成本衡量

带宽的提升将致使链路中retimer数量上升,在相同的传输距离下,如果采用光传输技术,所需的retimer和SCU(信号调节单元)会更少。此外,光组件的设计制造工艺较为成熟,成本也会变得更加可控,加上光纤所占空间明显小于铜缆,也有机会提升数据中心的整体密度,实现系统成本的降低。

另一方面,单 Lane 128G的传输速率将直接对PCIe 布线层面发起挑战。在Gen5/Gen6布线标准中提供了使用铜电缆在系统内部和系统之间传输 PCIe 的选项。铜电缆比 PCB 走线具有更少的信号损失,能克服高频通信的直接缺点,技术的升级将使得PCIe 7.0采用较粗的铜缆来克服高频通信,相较于前一代技术势必会带来成本的增加。PCIe 7.0技术升级也会对相应的服务器PCB工艺带来挑战,随着信号速率的飙升,PCB产品层数增加,BGA间距缩小,板厚显著增加,厚径比提升明显。这些变化也将导致材料成本和加工工艺难度的大幅增加。

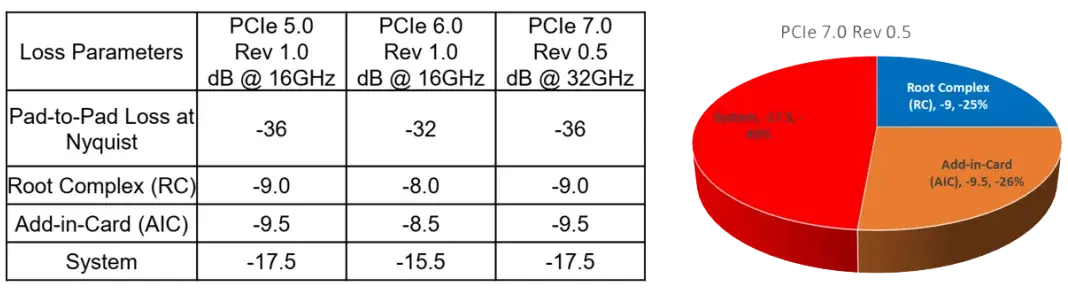

如下图所示,PCIe 7.0 Rev 0.5版本定义的理论损耗和分配,在7.0的奈奎斯特频率点(32GHz),Pad到Pad的损耗要求为-36dB,与6.0和5.0相比,在相同频点(16GHz)的损耗大大收紧。

PART. 02

光传输技术的可实现性

PCI-SIG于去年8月宣布组建PCIe光学工作组,并计划采用多种技术来支持 PCIe,包括可插拔光收发器、板载光学器件、共封装光学器件和光学 I/O。而我们也在今年看到了不同产业链的厂商在开展基于PCIe的光学产品研究,较为实际的例子是某服务器厂商基于PCIe Gen5的光互连方案将信号的传输距离从1.4米扩展到20米。该方案成功体现了光传输的优越性。

然而,短期内实现光传输技术的过渡却是较为困难,最初PCIe的接口并没有考虑过光传输的可能性,这就意味着现有的PCIe技术的架构几乎是基于电信号传输设计。首先我们需要考虑光传输与电气层兼容问题,其次是与PCIe 协议层的适配性,再者是如何通过光纤传输PCIe 信号以及基于光纤的PCIe 外形标准如何制定 、FEC标准如何制定等等问题,小编相信伴随协会的技术完善以及越来越多厂商的加入,我们将能看到更清晰的基于PCIe光传输技术应用的前景。

PART. 03

是德科技PCIe 7.0测试解决方案

在年初的展会上是德科技也与各厂商联合展出了基于Gen7的测试方案预研。下面,我们就一起来看看Gen7基于光电技术测试方案详情。

1

传统电气层解决方案

是德科技联合 ALPHAWAVE SEMI于2024年1月30日-2月1日举办的DesignCon 2024展会上联合展示了128G Gen7 收发端解决方案。

该解决方案由PCI-SIG协会主席Rick Eads演示,方案主要由 UXR系列实时示波器及高性能误码仪M8050A组成。

2

光传输技术解决方案初探究

是德科技于2024年3月24-28日举办的OFC2024展会上展示了低功耗 PCIe 7.0 光互连技术,支持新兴的大型语言模型对更高效信号传输的需求。

该解决方案包括M8050A 高性能误码仪(120G baud)、DCA-M N1092A(光通道)、N7736C光开关和800G DR8 LPO产品。

审核编辑 黄宇

-

PCIe

+关注

关注

16文章

1422浏览量

87554 -

算力

+关注

关注

2文章

1385浏览量

16566

发布评论请先 登录

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

PCIe 8.0规范开发更新!

PCIe 7.0技术细节曝光

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

PCIe 7.0 Samtec已为您准备好N种互连解决方案

嵌入式接口通识知识之PCIe接口

PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

PCIe协议分析仪能测试哪些设备?

PCIe 7.0最终版草案发布,传输速率128 GT/s,PCIe 6.0加速商业化

美光科技推出4600 PCIe 5.0 NVMe SSD

澜起科技推出PCIe 6.x/CXL 3.x Retimer芯片

PCIe 6.0 互操作性PHY验证测试方案

PCIe 7.0 互连— PCIe的尽头会是光吗?

PCIe 7.0 互连— PCIe的尽头会是光吗?

评论