作为致力于使数据传输更快更安全的业界领先芯片和IP核供应商,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布推出PCI Express®(PCIe®) 6.0控制器。PCIe规范是数据中心、人工智能/机器学习(AI/ML)、高性能计算、汽车、物联网、国防和航空航天等众多数据密集型市场领域实现互连的共同选择。Rambus PCIe 6.0控制器在功耗、面积和延迟方面进行了优化,可为高性能应用提供高达每秒64GT的数据传输速率。此外,该控制器还提供最先进的安全性,其完整性和数据加密(IDE)引擎可以监控和保护PCIe链路免受物理攻击。

Rambus首席运营官范贤志表示:“AI/ML和数据密集型工作负载的快速发展要求我们继续提供数据传输速率更高,并且在延迟、功耗和面积方面有最佳表现的解决方案。PCIe 6.0控制器是我们业界领先的接口IP产品组合推出的又一款新品,为客户提供易于集成的解决方案,为先进的SoC和FPGA带来更佳的性能和安全性。”

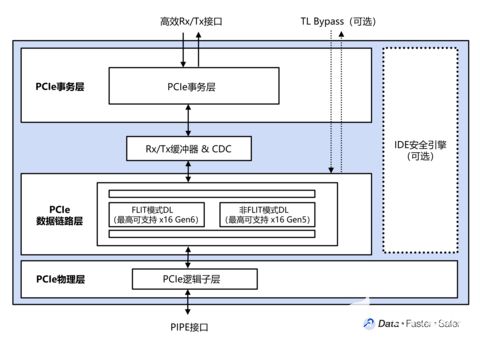

Rambus PCIe 6.0控制器有以下主要特性:

支持PCIe 6.0规范,包括64 GT/s数据传输速率和PAM4调制信号

支持固定尺寸的FLIT,可实现高带宽效率

实现低延迟前向纠错(FEC),保证链路鲁棒性

向后兼容PCIe 5.0、4.0和3.0/3.1

经过性能优化的集成IDE

Rambus PCIe 6.0控制器框图 (图示:美国商业资讯)

审核编辑:汤梓红

-

芯片

+关注

关注

462文章

53539浏览量

459168 -

控制器

+关注

关注

114文章

17646浏览量

190265 -

数据中心

+关注

关注

16文章

5519浏览量

74653

发布评论请先 登录

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

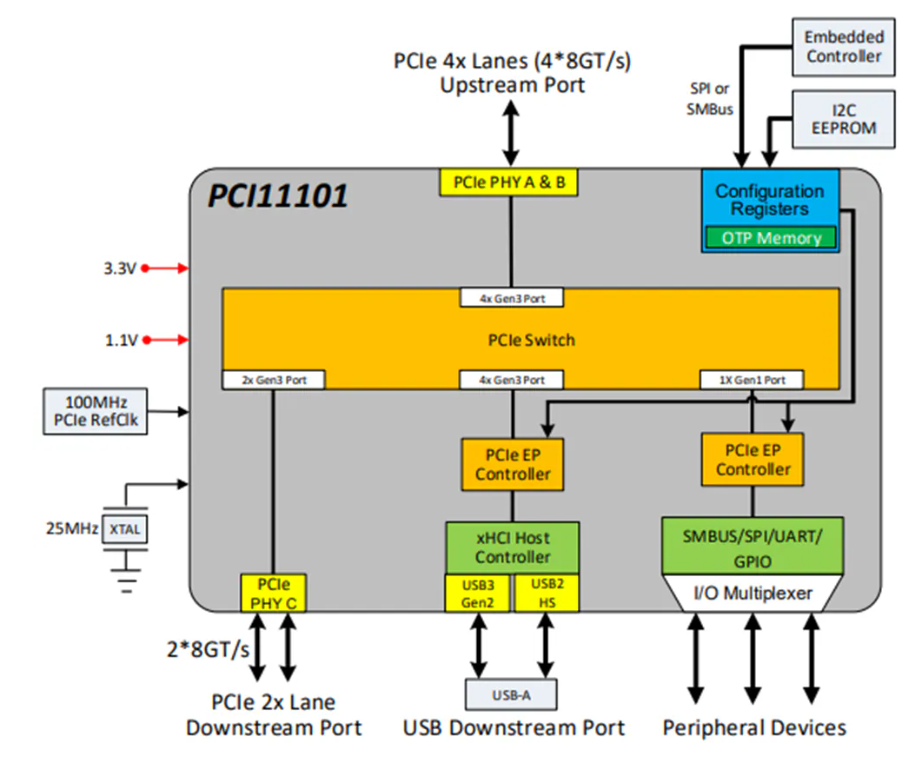

钛金PCIe Gen4控制器的核心特性与技术细节

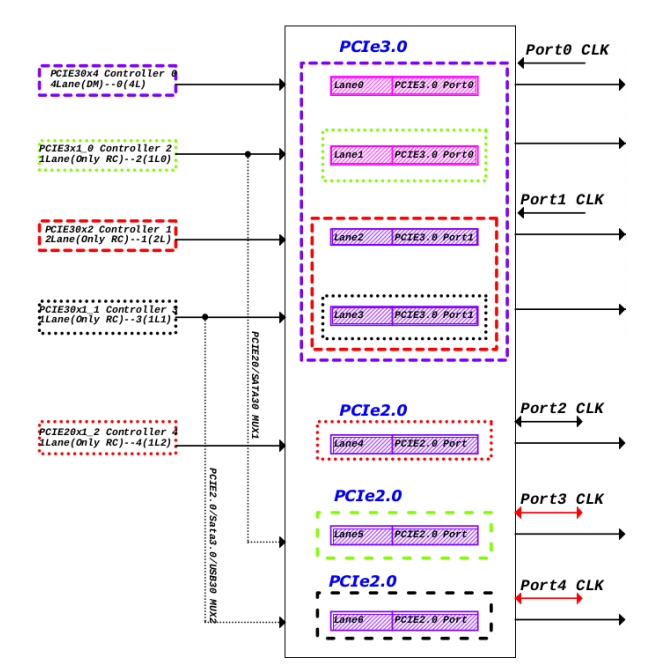

一文搞懂 RK3588 PCIe:从硬件资源到拆分配置 + 避坑指南(含脑图)

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

PCI11101 PCIe交换机集成USB3.2主机控制器技术解析

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

NVMe控制器IP设计之接口转换

Diodes公司PCIe 6.0时钟缓冲器介绍

详解PCIe 6.0中的FLIT模式

PCIe 6.0时代的测试挑战和解决方案

Rambus PCIe 6.0控制器的主要特性

Rambus PCIe 6.0控制器的主要特性

评论