PCIe7.0的测试方案

随着 PCIe 6.0 标准刚刚进入市场,PCI-SIG 组织已着手推动下一代标准——PCIe 7.0,预计将在 2025 年正式发布,持该标准的设备预计将在 2026 年问世,而大规模商用应用可能要到 2028-2029年才会普及。尽管消费级市场短期内不会广泛采用 PCIe 7.0,但对于AI 计算、高性能数据中心和云计算而言,它将成为未来计算架构的关键推动力。

作为新一代高速互连协议,PCIe 7.0 在数据速率、能效优化和新型传输技术等方面实现了重大突破,特别是引入了光学通信连接,这将彻底改变计算基础架构。

PCIe 7.0 的主要特性

1. 带宽翻倍

PCIe 7.0 的核心目标是将数据传输速率提升至 128 GT/s,相比 PCIe 6.0 实现翻倍,相当于 PCIe 5.0 的四倍。在 x16 通道配置下,理论双向带宽可达 512 GB/s,显著提升数据吞吐能力。这一突破对于 AI、高性能计算(HPC)等需要超高速数据交换的应用至关重要,有助于缓解数据传输瓶颈。

2. PAM4 信号编码

PCIe 7.0 继承了 PCIe 6.0 引入的 PAM4(四级脉冲幅度调制)技术,相较于传统的 NRZ(二进制非归零编码),PAM4 在每个时钟周期内传输 2 位数据,无需大幅提高信号频率即可提升数据传输速率。这种编码方式有效提高信号效率,同时优化通道利用率。

3. 低延迟与高可靠性

PCIe 7.0 在提升带宽的同时,进一步优化数据传输延迟和可靠性,确保在高负载环境下依然能够提供稳定的传输体验。这对实时计算、云计算、自动驾驶等对时延敏感的应用尤为关键。

4. 能效优化

在提供更高性能的同时,PCIe 7.0 也注重功耗控制和能效优化。尽管更高的传输速率可能会增加功耗,但单位传输效率(性能/功耗比)预计将显著提升。这对于数据中心、边缘计算等大规模部署场景有助于降低运营成本,并减少碳排放。

5. 向后兼容

PCIe 7.0 保持了与所有前代 PCIe 版本的向后兼容性,无论是旧设备插入 PCIe 7.0 插槽,还是 PCIe 7.0 设备连接至早期版本插槽,系统都会自动协商双方支持的最高速率,确保平稳升级,最大程度保护用户投资。

6. 通道优化与信号完整性增强

面对更高的传输频率,PCIe 7.0 对信号完整性和通道设计进行了深度优化,包括改进信号路径设计、降低噪声、增强误码率(BER)控制,以确保在更远传输距离下仍能保持稳定的数据传输。

PCIe 7.0 的推出标志着数据传输技术的重大突破,同时也是对未来计算需求的前瞻性布局。通过大幅提升带宽、降低延迟、优化能效,PCIe 7.0 为 AI、高性能计算(HPC)、数据中心等关键领域的持续发展提供了强有力的支撑。

尽管消费级市场的普及可能仍需时日,但 PCIe 7.0 在服务器、数据中心等高性能应用领域的前景毋庸置疑。随着光纤互连等前沿技术的进步,PCIe 7.0 有望突破传统铜缆的物理限制,推动计算与互连技术迈向新高度。同时,它确保了 PCIe 生态系统的稳定演进,避免市场碎片化,并为未来更高速互连技术的发展奠定坚实基础。

近期,是德科技也与各厂商联合展出了基于PCIe 7.0的测试方案预研,如需了解更多有关 PCIe 7.0的解决方案,请点击链接:PCIe 7.0 互连— PCIe的尽头会是光吗?

PCIe6.0的测试方案

在数据密集型计算和人工智能(AI)快速发展的推动下,计算机互连技术正经历着前所未有的变革。随着标准的确立和技术的成熟,PCIe 6.0 已经在全球范围内进入商业化落地阶段。2022年1月,PCI-SIG 组织正式发布了 PCI Express 6.0(PCIe 6.0)标准,这次升级堪称该技术自诞生以来变化最大的一次。

相较于前几代标准,PCIe 6.0 不仅继续提升带宽,还在底层架构和功能特性上进行了革命性改进,使其能够满足未来高性能计算、数据中心、人工智能(AI)、汽车、物联网(IoT)等领域的需求。

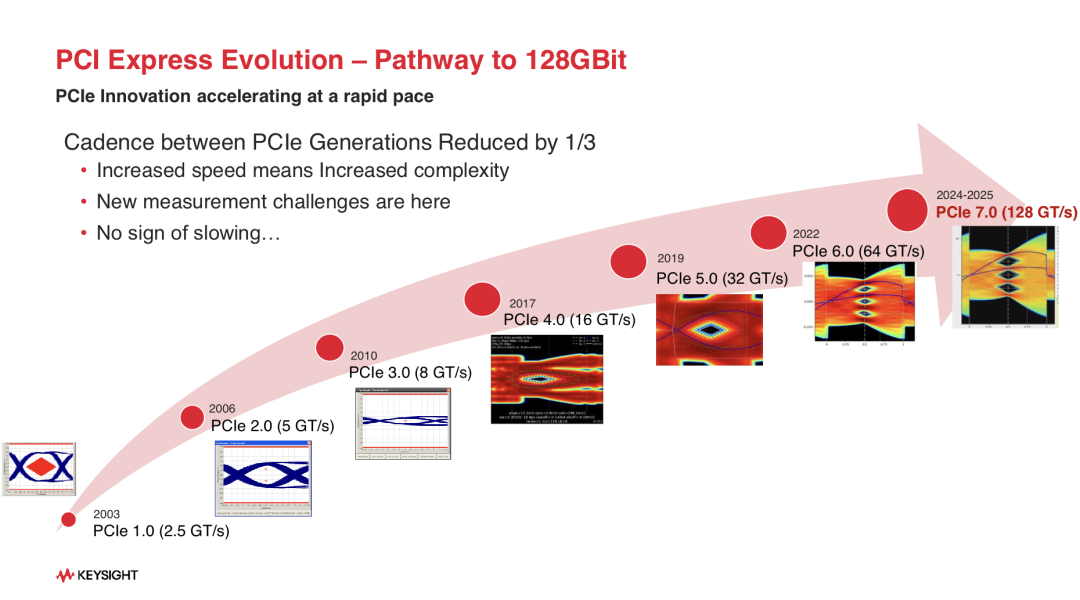

图 1:PCIe 标准的发展

PCIe7.0 正在向高达 128GT/s 和 PAM4 调制的速度发展

PCIe 6.0的带宽是 PCIe 5.0 的两倍,达到 1024 Gb/s,最大通道数仍为 16。每个引脚的数据传输速率将从 PCIe 5.0 的 32 GT/s 提高到 64 GT/s。从 NRZ 到 PAM4 信号的转变带来了新的挑战。PCIe 6.0 还向后兼容前几代 PCIe 产品。PCIe 技术已部署在高性能计算、超大规模数据中心基础设施、人工智能系统、台式机计算、汽车应用和移动设备等各种产品中。

PCIe 6.0 采用 PAM4 信号编码,使数据传输速率达到 64 GT/s,同时在保持向下兼容的前提下实现了更高带宽。然而,这也给发射机测试带来了全新的难题,尤其是在信号完整性和噪声管理方面。

今天我们将带您深入了解 PCIe 6.0发射机合规性测试的关键挑战以及 Keysight 如何通过领先技术和自动化解决方案为工程师保驾护航。

PCIe 6.0 发射机测试(TX)的挑战

PAM4 信号编码带来的噪声问题

相比传统的 NRZ 信号,PAM4 编码固有地引入额外约 9 dB 的信噪比下降,这要求测试仪器必须具有极低的噪声底和高精度测量能力。

高速信号传输中的通道损耗

随着数据速率提升至 64 GT/s,高频信号在传输过程中会遭受更严重的通道损耗和衰减,测试时需要准确捕捉并分析信号衰减与失真情况。

多速率测试要求

PCIe 6.0 不仅要求验证最高速率下的性能,还需要在 64、32、16、8、5、2.5 GT/s 等多个速率下进行测试,确保不同场景下的发射机性能均符合规范。

硅级与系统级验证难度

测试既要关注芯片内部(硅级)的信号质量,又要验证整机系统在实际工作环境下的互联性能,这就需要不同层次的测试方案协同工作。

这些挑战促使测试设备必须具备高带宽、低噪声和自动化测试功能,以确保 PCIe 6.0 发射机能够精确、稳定地运行并顺利通过 PCI-SIG 官方认证。

Keysight 的测试解决方案

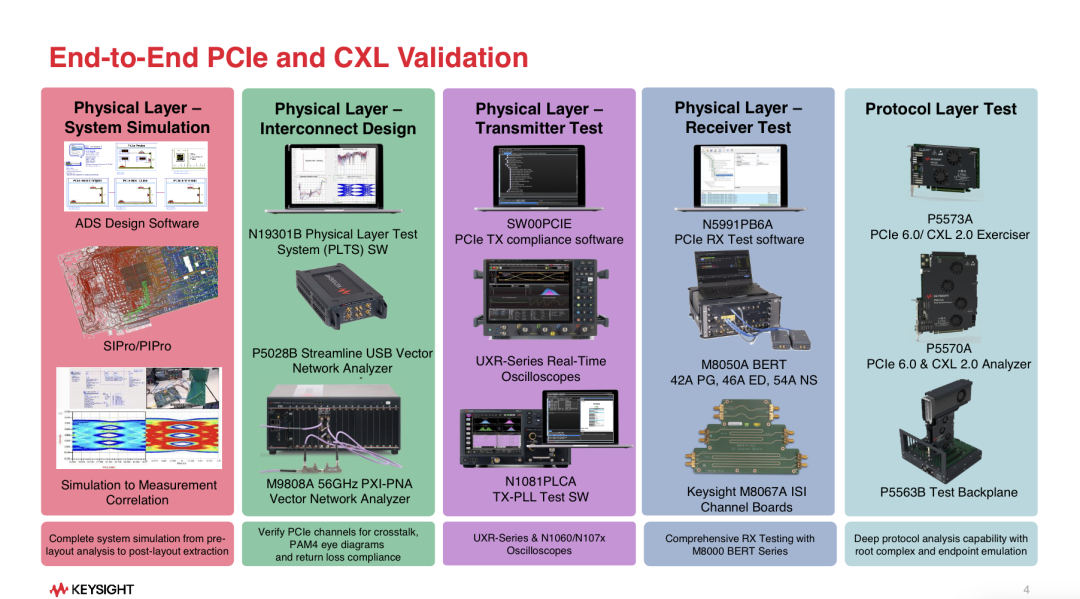

Keysight 提供了一整套覆盖从系统仿真到协议分析的 PCIe 6.0 到 PCIe 7.0测试方案,其中包括针对PCIe 发射机合规性测试的关键技术。

图2:是德科技PCIe解决方案

对 PCIe 6.0 器件进行发射机合规性测试,需要使用示波器测量被测器件(DUT)发送的、数据速率高达 64 GT/s 的 PAM4 信号。研发工程师需要使用大带宽示波器执行物理层测试、数据链路层测试和通用互操作性测试,以确保发射机达到 PCI-SIG 认可的合规性。

图 3:PCIe 6.0 发射端(TX)一致性测试解决方案

Keysight PCIe 6.0 发射机合规性测试解决方案包括 Keysight PCI Express 验证许可证套件、先进信号完整性分析软件、抖动和噪声分析软件,以及脉冲幅度调制分析软件。这些软件均在大带宽的 Keysight UXR 系列示波器上运行。工程师需要使用一台带宽 > 50 GHz、采样率不低于 256 GSa/s 的示波器,以便测试 64 GT/s 信号。开发人员可以借助这些工具自动对 PCIe 6.0 器件进行合规性测试,通过分析器件发送的 PAM4 噪声和抖动性能,从而准确测量被测器件发送的信号,确认其符合 PCI-SIG 标准。

关于是德科技

是德科技(NYSE:KEYS)启迪并赋能创新者,助力他们将改变世界的技术带入生活。作为一家标准普尔 500 指数公司,我们提供先进的设计、仿真和测试解决方案,旨在帮助工程师在整个产品生命周期中更快地完成开发和部署,同时控制好风险。我们的客户遍及全球通信、工业自动化、航空航天与国防、汽车、半导体和通用电子等市场。我们与客户携手,加速创新,创造一个安全互联的世界。

-

带宽

+关注

关注

3文章

1050浏览量

43572 -

发射机

+关注

关注

7文章

531浏览量

49324 -

PCIe

+关注

关注

16文章

1479浏览量

88925 -

发射端

+关注

关注

0文章

53浏览量

8600 -

是德科技

+关注

关注

21文章

1072浏览量

85729

原文标题:Solution Talks | 如何测试 PCIe® 6.0 / 7.0的发射端(TX)一致性

文章出处:【微信号:是德科技KEYSIGHT,微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新应用 | 横扫第四代串行测试(之二)

大功率发射机的水冷散热解决方案

罗德与施瓦茨 SFE100 回收 测试发射机

多标准无线电基站发射机测试

是德科技推出全新的发射机(Tx)和接收机(Rx)综合测试解决方案

泰克提供业界首创的 PCIe 6.0 测试解决方案

是德科技发布端到端PCIe5.0/6.0测试解决方案

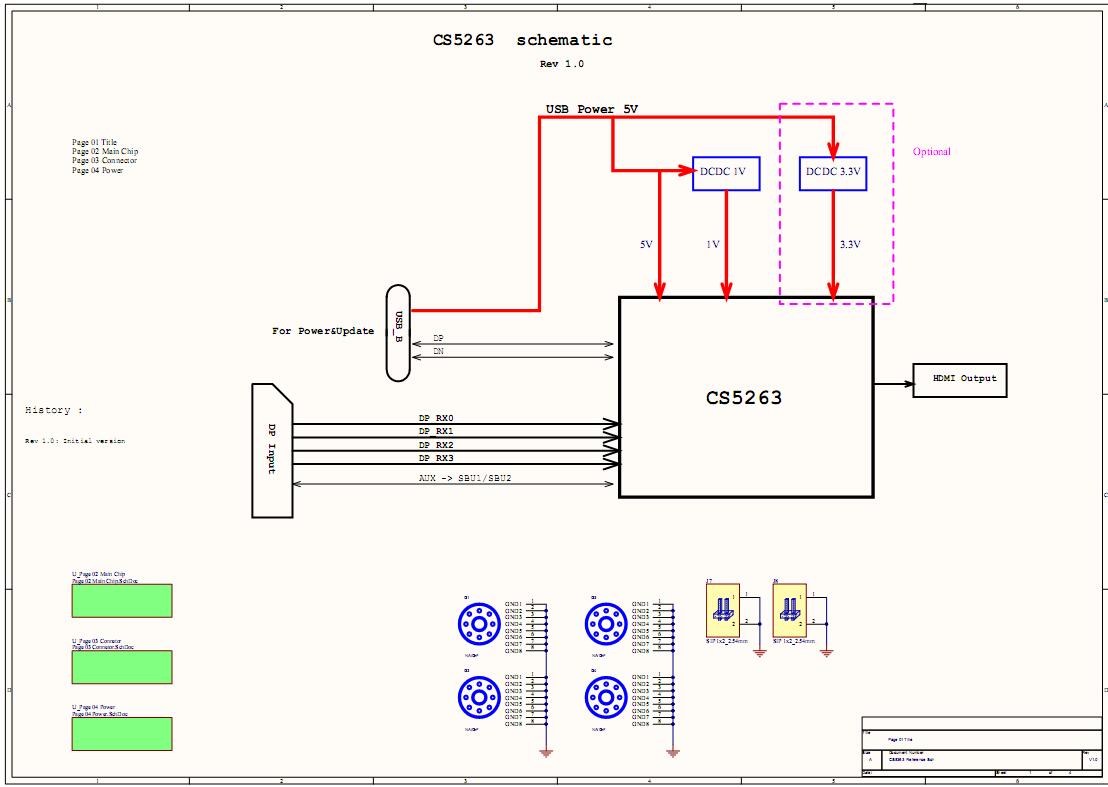

CS5263高性能HDMI 2.0发射机概述及特性

罗德与施瓦茨USB 3.2 Gen 1和Gen 2发射机与接收机一致性测试方案获得USB-IF批准

是德科技推出UALink 1.0发射机测试解决方案

是德科技PCIe 6.0发射机合规性测试解决方案

是德科技PCIe 6.0发射机合规性测试解决方案

评论