PCIe无疑是最为流行的传输总线标准,这几年的更新换代也十分频繁:PCIe 3.0目前还是最普及的,PCIe 4.0正在快速崛起,PCIe 5.0即将和大家见面,PCIe 6.0也正在快速推进制定中。

PCI-SIG组织今天宣布,PCIe 6.0规范已经完成了0.5版本,并提供给组织成员,将在明年按期发布最终正式版。

PCIe每版规范的制定都要经历五个不同版本/阶段:

0.3版本:初步概念,提出新规范的关键特性和架构。

0.5版本:初始草案规范,确定新架构的所有层面,并吸收0.3版本基础上组织成员的反馈意见,并加入成员需求的新特性加的新特性。

0.7版本:完成版草案,新规范的方方面面都完全确定,电气规范也必须通过测试芯片完成验证。之后不会再加入新功能。

0.9版本:最终版草案,组织成员可以据此设计、开发自己的技术和产品。

1.0版本:最终正式版,公开发布。

事实上,0.5版本发布之后,厂商们已经可以开始设计测试芯片,为后续工作提前做好准备。

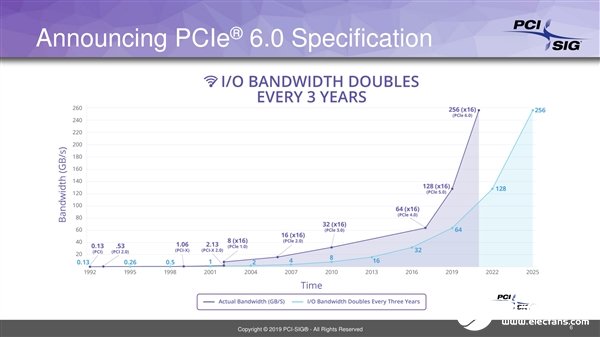

尽管升级速度加快,但是每一代PCIe规范的变化都相当大,尤其是带宽每次都翻一番,并兼容所有前代规范。

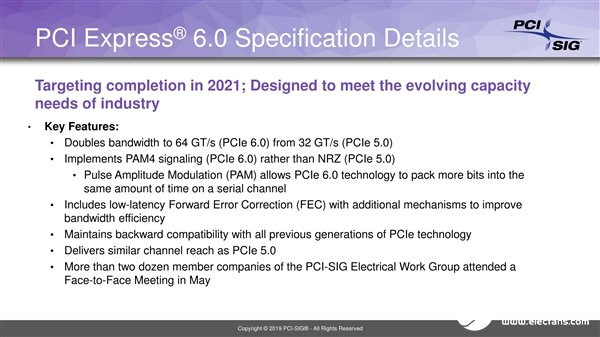

PCIe 6.0也不例外,向下兼容PCIe 5.0/4.0/3.0/2.0/1.0的同时,数据率或者说I/O带宽会再次加倍来到64GT/s,PCIe 6.0 x1单向实际带宽8GB/s,PCIe 6.0 x16单向带宽128GB/s、双向带宽256GB/s。

PCIe 6.0将延续PCIe 3.0时代引入的128b/130b编码方式,但加入全新的脉冲幅度调制PAM4,取代PCIe 5.0 NRZ,可以在单个通道、同样时间内封包更多数据,以及低延迟前向纠错(FEC)和相关机制,以改进带宽效率。

今年的PCI-SIG开发者大会将于6月初举行,届时会有超过25家组织成员对PCIe 6.0规范进行面对面讨论,更多细节也会对外公布。

大家可能会感到疑惑:PCIe规范更新换代如此迅速,我该买哪个版本的产品最好?是不是现在入手PCIe 4.0的很快就会过时呢?

其实大可不必有此担忧,因为任何科技都是在不断发展演进的,永远都会有更好的出现,自己有需要的时候就上,“等等党”是没有尽头的……

责任编辑:wv

-

PCIe

+关注

关注

16文章

1421浏览量

87550

发布评论请先 登录

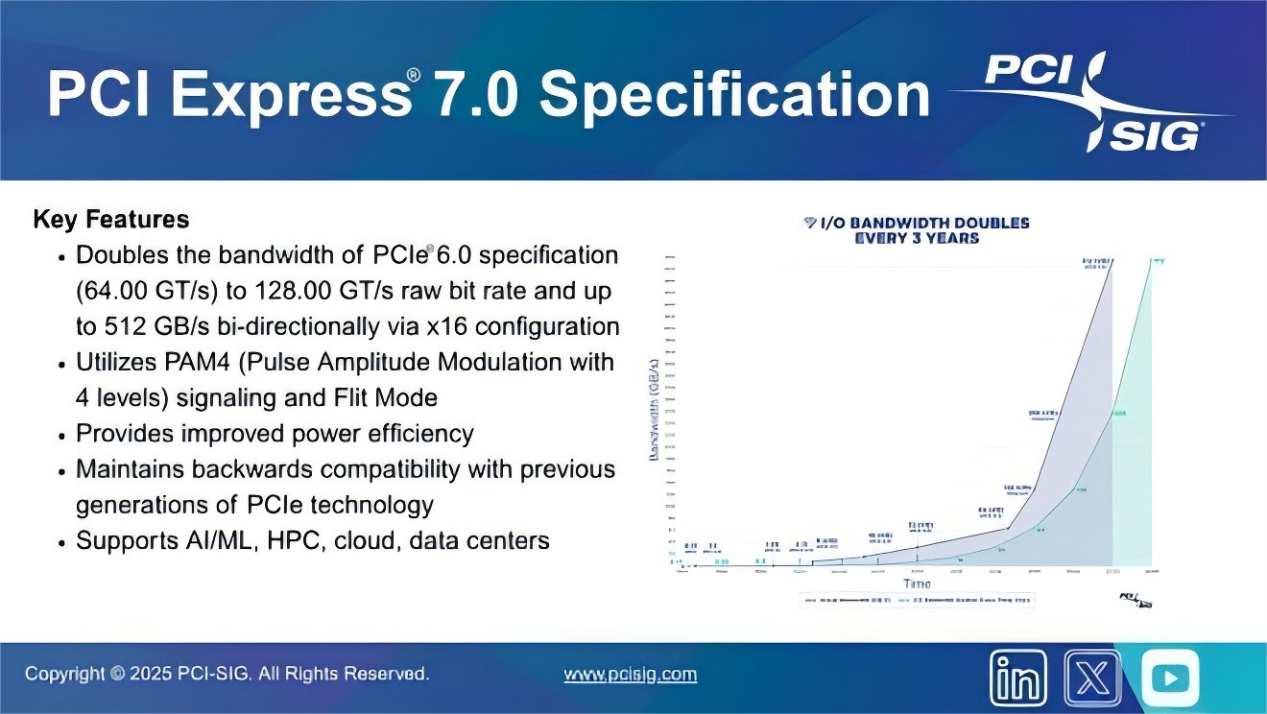

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

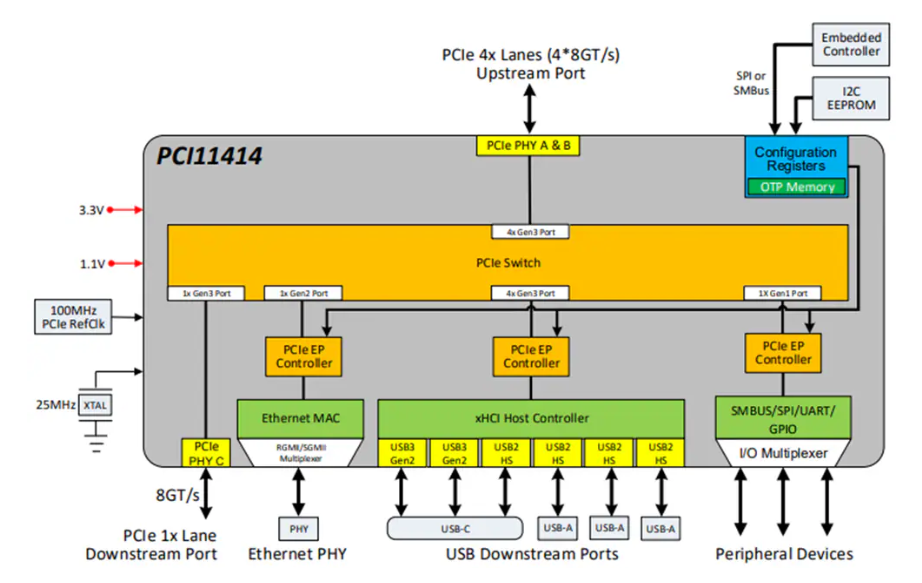

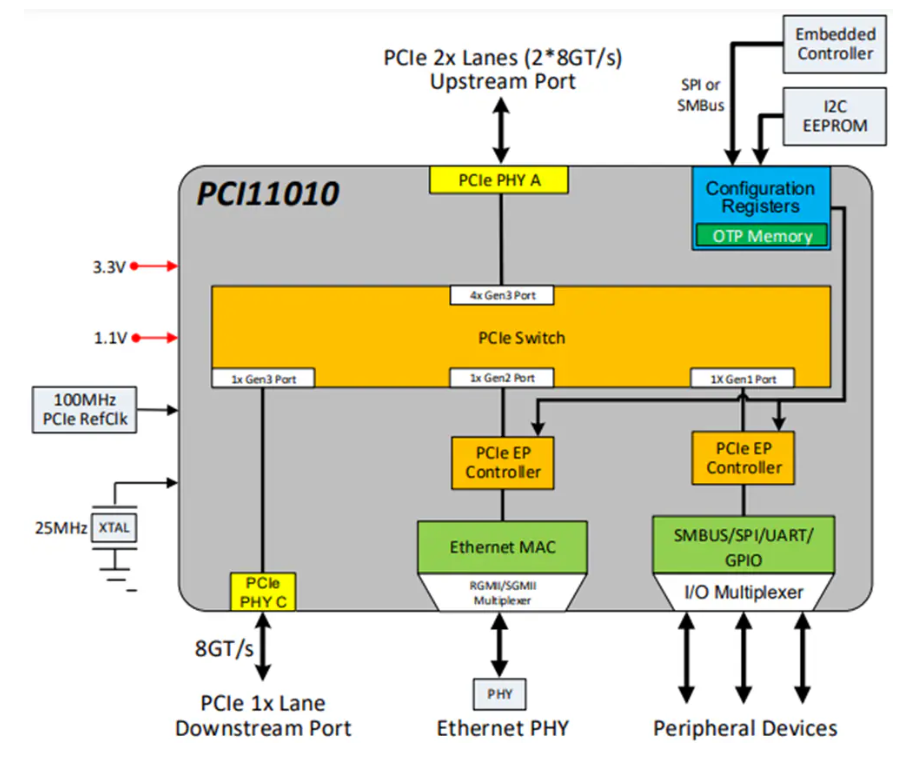

PCI11414 PCIe交换机技术解析与应用设计指南

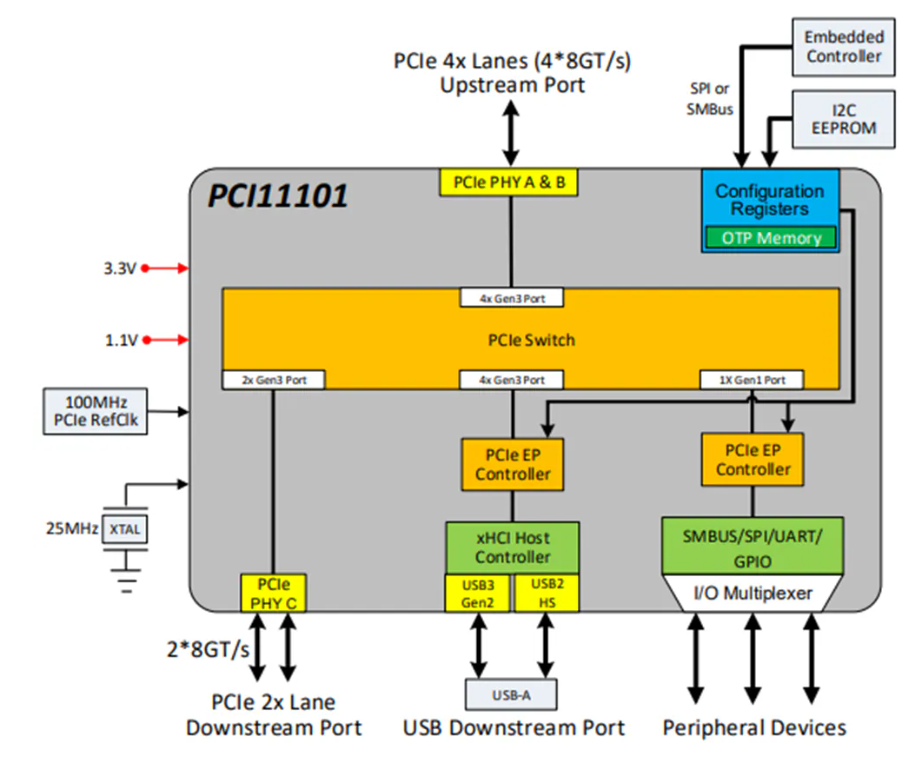

PCI11101 PCIe交换机集成USB3.2主机控制器技术解析

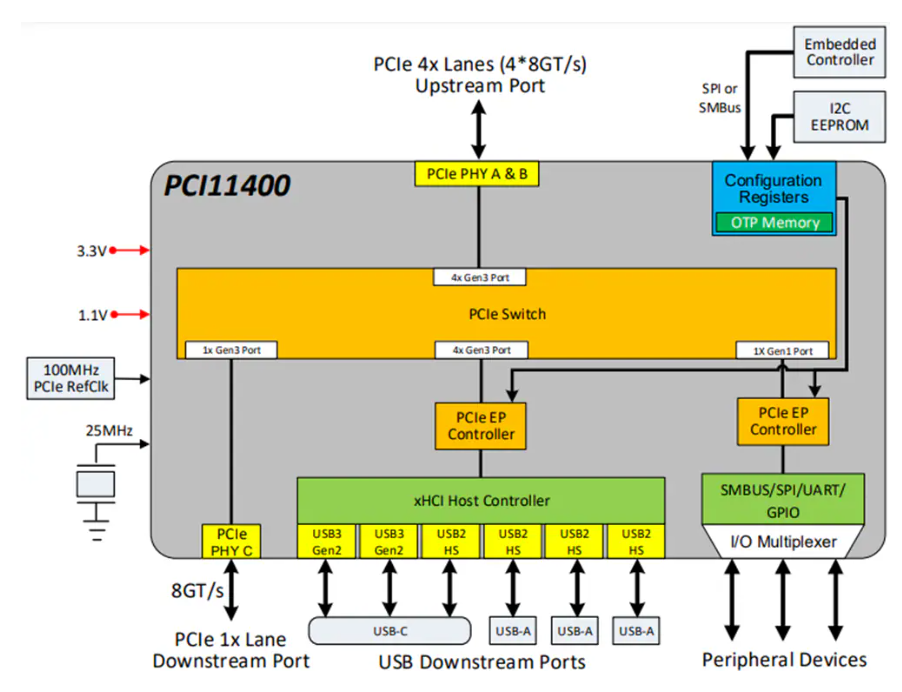

Microchip PCI11400 PCIe交换机技术解析与应用指南

PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

PCB插损和阻抗测试方案

PCIe 6.0将于明年发布最终正式版 I/O带宽再次加倍来到64GT/s

PCIe 6.0将于明年发布最终正式版 I/O带宽再次加倍来到64GT/s

评论