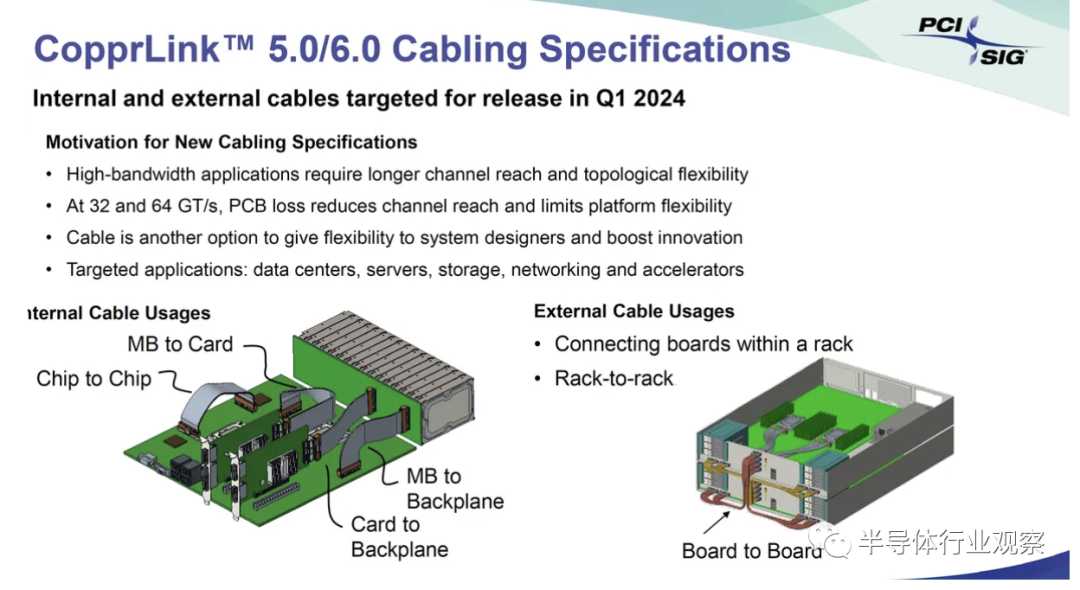

PCI SIG 本周表示,它正在开发 PCIe 5.0 和PCIe 6.0接口的布线规范,数据传输速率为 32 GT/s 和 64 GT/s。新的电缆规格将于 2024 年第一季度发布,并将命名为 CopprLink,可能是为了避免与现有OCuLink电缆混淆,并强调其铜质特性。

CopprLink 5.0 和 6.0 规范专为数据中心和服务器而设计。它们旨在连接主板到背板、卡到背板、主板到扩展卡(例如加速器)、机架到机架、机架内的板到板,甚至 PCIe 5.0 (32 GT/s) 和 PCIe 的芯片到芯片6.0 (64 GT/s) 速度。其目的是为印刷电路板上典型 PCIe 链路效率低下或由于某种原因无法建立的情况提供一些额外的灵活性。上述情况不包括长距离连接,因此我们这里讨论的可能是几十厘米。

由于噪声和信号丢失,通过电缆以 32 GT/s 或 64 GT/s 的速度运行数据是一项艰巨的任务,但在许多情况下,电缆的使用是不可避免的,这就是业界开发 CopprLink 的原因。值得注意的是,PCI SIG 仅提及数据中心级应用,并未提及客户端 PC 或汽车应用。也许,CopprLink 最终也会被这些应用采用(因为为什么不呢?),但目前 PCI SIG 还没有提及它们。

关于 CopprLink 需要注意的另一件事是,该名称暗示铜缆,而不是光纤互连,这是 PCI SIG 正在开发的另一个规范。也就是说,我们不能排除这样的可能性:如果有需要并且光学 PCIe 规范尚未准备好,那么在某些时候有人会构建具有光学互连的 CopprLink 以实现更远距离的连接。

PCIe 接口的普及需要不断的发展,不仅是标准本身,还包括其布线规范。有用于消费类应用的基于 PCIe 协议的 Thunderbolt 和 USB4 技术,还有用于服务器和工作站的内部和外部 PCIe 3.0 和 PCIe 4.0 电缆连接的 OCuLink。CopprLink 是成熟的基于 PCIe 的互连系列的自然补充。

其实关于CopprLink ,PCI-SIG并没有披露太多,但很多人认为,CopprLink 可能与带宽改进和数据传输有关,而不一定用于供电,但它确实引起了人们对 12VHPWR 电缆或连接器的潜在继任者可能是什么样子的好奇。

从相关报道我们可以看到,OCuLink 是内部/外部 PCI 电缆技术的名称,其规范涵盖电信号方法(名称的 Cu 部分,即铜)和光学版本(当然是 O 位)。它支持 PCIe 4.0,并使用多达八个通道来传输数据,但规范不包括电力传输。

尽管该公告没有直接说明这一点,但我认为可以肯定地假设 CopprLink 将仅用于 PCIe 5.0 和 6.0 布线,而最适合这些的市场是 HPC 市场。不过,我认为它还有空间用于未来的项目,例如GDP G1)和最近的OneXGPU。

该单元配有一个外部 GPU、一个 M.2 SSD 和大量 IO 端口。一次性使用所有这些功能受到我们此类系统当前选项的极大限制,例如 USB4 Gen 2 或 OCuLink。简而言之,它们无法提供足够的带宽来防止 GPU+SSD+IO 受到性能限制。

不过,具有 8 个 PCIe 5.0 通道的电缆应该具有足够的带宽,如果它还可以供电,那么这将是扩展笔记本电脑或手持设备功能的好方法。实现这一点有多容易完全是另一回事,因为 PCIe 5.0 在 PC 领域仍然相当新。

审核编辑:刘清

-

连接器

+关注

关注

105文章

16381浏览量

147894 -

加速器

+关注

关注

2文章

841浏览量

40244 -

PCIe接口

+关注

关注

0文章

128浏览量

10653

原文标题:PCIe重磅公布:用CopprLink 取代 OCuLink?

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

如何理解Linux内核中的PCIe驱动

探索TS2PCIE412:高性能PCIe开关的技术剖析

致钛tiplus7100 为什么不走pcie4.0传输模式

什么是 OCuLink 接口?

基于巨霖SIDesigner实现PCIe仿真的步骤

PCIe:用CopprLink取代OCuLink?

PCIe:用CopprLink取代OCuLink?

评论