电子发烧友网综合报道,近日,PCI-SIG宣布PCI Express 8.0规范的Version 0.3 版本已获得工作组批准,现已向PCI-SIG 会员开放。这标志着PCIe 8.0 规范完成了第一版审查草案,该规范正按照2028年正式推出的预设开发进程推进。按照 PCIe 规范此前的开发惯例,PCIe 8.0 此后还将经历 Version 0.5 / 0.7 / 0.9 等阶段方能走到最终的 1.0 版本。

PCI Express 8.0 规范开发计划于今年8月公布,该标准将继续采用PAM4脉冲幅度调制信号技术,并在PCIe 7.0的基础上实现传输速率翻倍,达到每通道256GT/s。在×16 配置下双向传输带宽可达 1TB/s,旨在满足未来高性能计算、AI对高速互联的需求。

PCIe规范自2001年正式发布以来,经历了多个版本的演进,始终围绕 “更高带宽、更低延迟、更强扩展性” 展开。

2017年PCIe 4.0推出,速率为 16GT/s。它实现了每通道 PHY 集成,功耗降低 30%,广泛应用于 NVMe SSD、AI 加速卡等。2019 年PCIe 5.0发布,速度提升到 32GT/s。此版本引入了前向纠错(FEC)、FLIT 调度算法等技术,支持 CXL(Compute Express Link)协议落地,可用于高性能计算、AI 训练集群等场景。

PCI-SIG组织于2022年1月发布PCIe 6.0标准。其双向带宽达256 GB/s(x16通道),较PCIe 5.0实现翻倍,同时采用四级PAM4信号调制与轻量级前向纠错技术,有效提升传输速率至64 GT/s并降低误码率 。该标准引入固定尺寸FLIT流量控制单元,支持动态带宽调节与完整数据加密功能,兼具高效传输与物理安全性,且向下兼容前代协议 。

核心技术革新包括通过PAM4信号调制实现单位间隔传输4级信号;采用1b1b编码及新型FLIT协议提升链路利用率;运用循环冗余校验与格雷编码增强可靠性 。电源管理方面引入L0p动态状态调节功能,可降低非活动通道功耗并优化能效比。PCIe 6.0 SSD主控预计在2028年开始量产,部分企业已推出基于PCIe 6.0的测试产品或主控芯片。

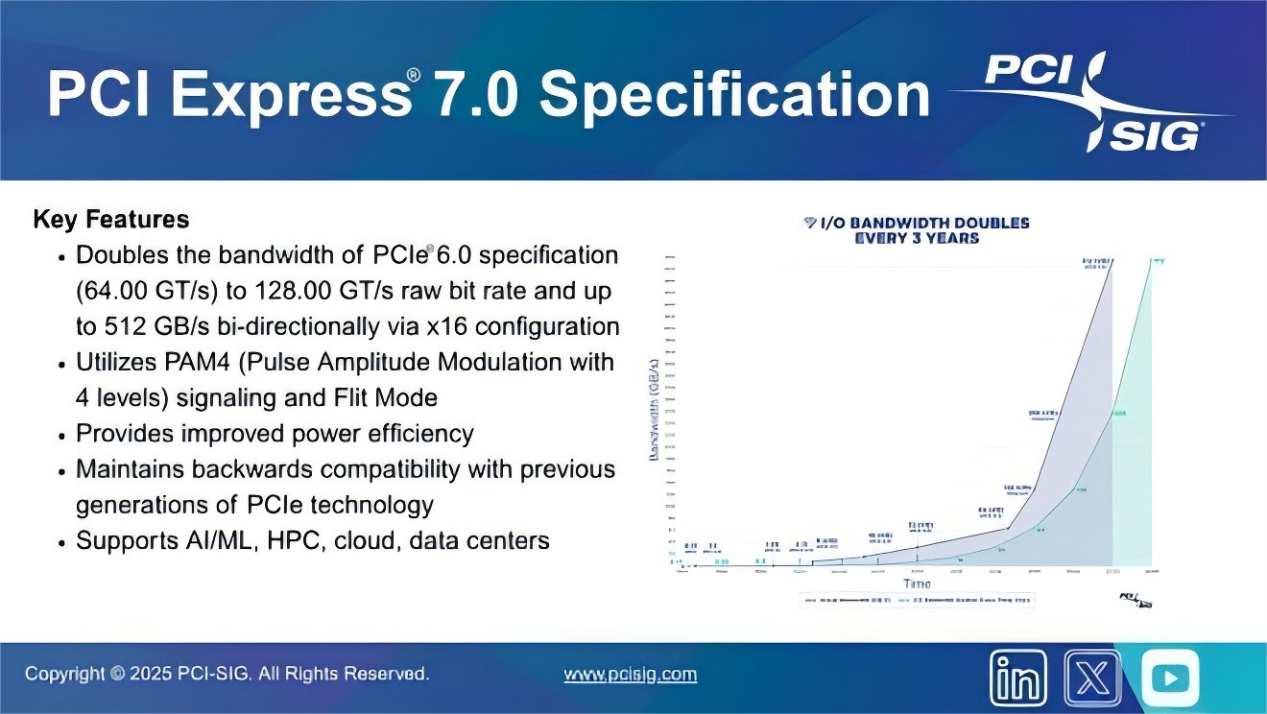

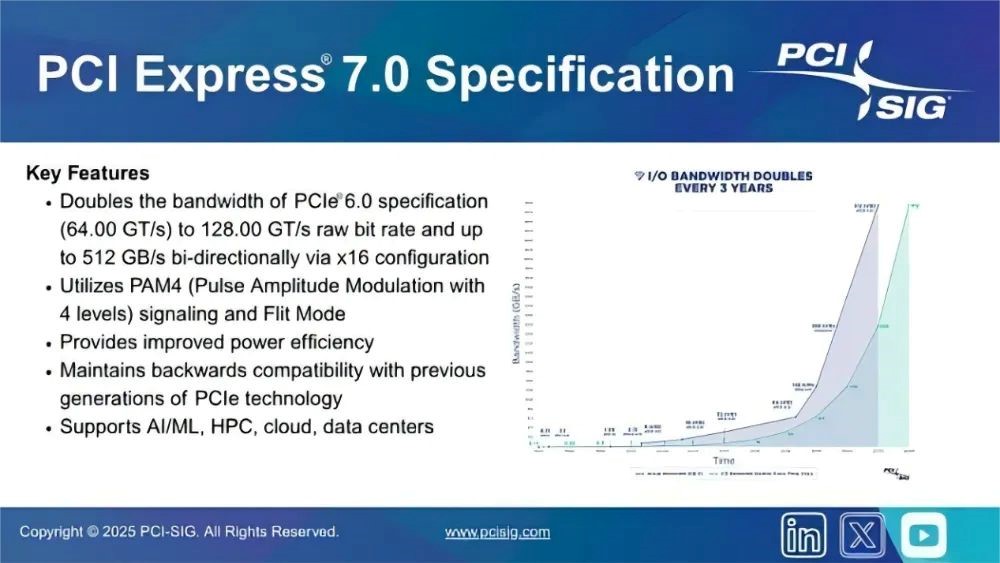

PCIe 7.0规范于2025年6月12日由PCI-SIG正式发布,最高传输速率达128GT/s,为下一代AI、机器学习、800以太网、云计算和量子计算等数据驱动型应用提供了强大的支持。PCIe 7.0规范的主要特点包括:提供128.0GT/s的原始比特率,通过x16配置可实现高达512GB/s的双向带宽。采用PAM4(4级脉冲幅度调制)信号和基于Flit的编码技术。提高了能效比。与以往的PCIe技术保持向后兼容性。预计2027年完成预测试,2028年发布首批集成商名单。

市场进程方面,据CFM闪存市场数据统计,PCIe 4.0在2023年已占据消费级SSD市场55%的出货量,2025年将攀升至71%,持续巩固主流地位。另外,有数据显示,企业级SSD需求扩张,PCIe 5.0 SSD的高效能需求将进一步推升产业成长。2025年企业级SSD市场将年增15%,PCIe 5.0 SSD渗透率将从2024年的9%提升至2026年的61%。根据 IDC 测算,2025 年 PCIe 5.0 在数据中心市场的渗透率预计将达到 78%。随着 AI 技术发展,数据中心对高速数据传输和存储需求大增,PCIe 5.0 因高带宽、低延迟等特性,正逐渐成为数据中心的主流选择。

发布评论请先 登录

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

Silicon Labs发布新版Z-Wave SDK 8.0

开发者必备,10 分钟搞定 RK3588 PCIE 拆分!

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

0.1 至 8.0 GHz SP3T 开关 skyworksinc

PCIe 4.0/5.0仍是主流!三家SSD企业抢滩高性能存储市场,新品相继亮相

PCIe 8.0规范开发更新!

PCIe 8.0规范开发更新!

评论