2022年1月11日,PCI-SIG正式发布了PCI Express(PCIe) 6.0最终版本1.0,标志着各大IP、芯片厂商可以开始着手设计、开发自己技术和产品了。从技术上来说,PCIe 6.0是PCIe问世近20年来,变化最大的一次。

根据PCI-SIG的介绍,PCIe 6.0主要有三大变化:数据传输速率从32GT/s翻倍至64GT/s;编码方式从NRZ 信令模式转向PAM4信令模式;从传输可变大小TLP到固定大小FLIT。

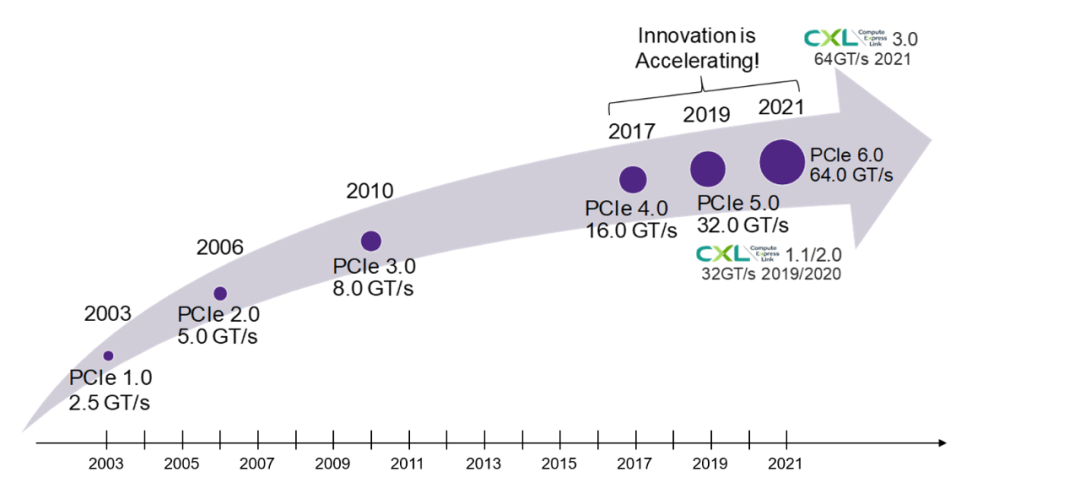

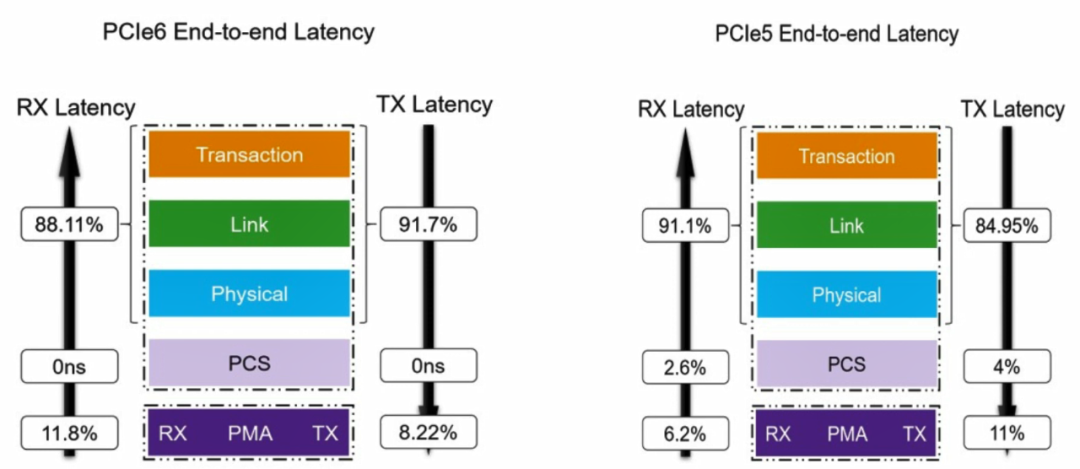

图:PCIe发展历史(来源:新思科技)

PCIe 6.0的新变化

从PCIe的发展历史可以看到,在2017年以前,发展速度相对较慢,三、四年更新一次标准,PCIe 3.0发布后甚至等了七年才推出PCIe 4.0。但是2017年之后,PCIe标准几乎每两年就更新一次,更新速度明显加快。

这是因为近年来,高性能计算和AI快速发展,高清视频和网络数据迅速膨胀,还有自动驾驶等技术的蓬勃发展。这些技术的推动,让数据中心和高性能计算机对高速率和高带宽的需求越来越大,PCI-SIG也加快了新标准的推出。

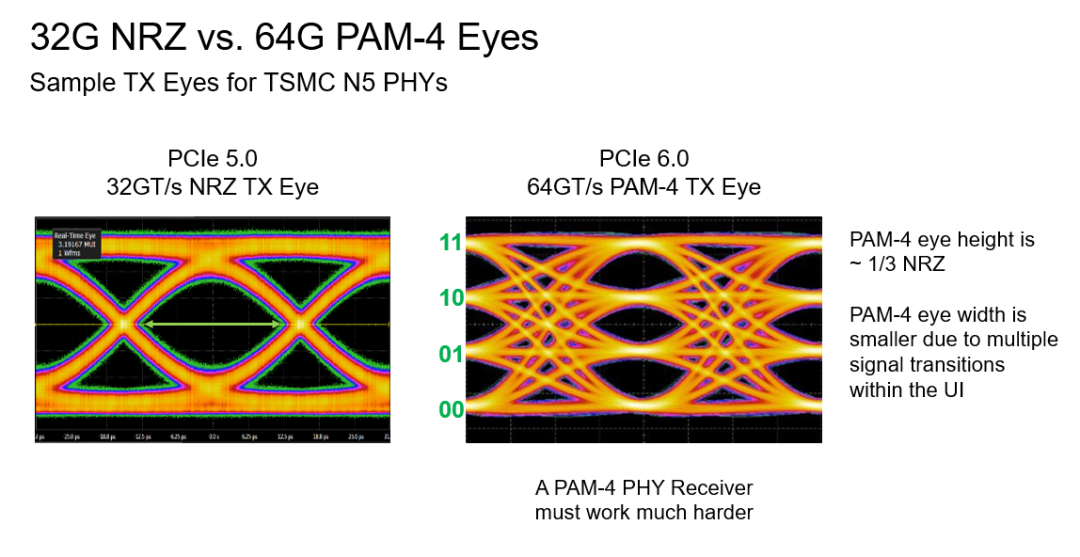

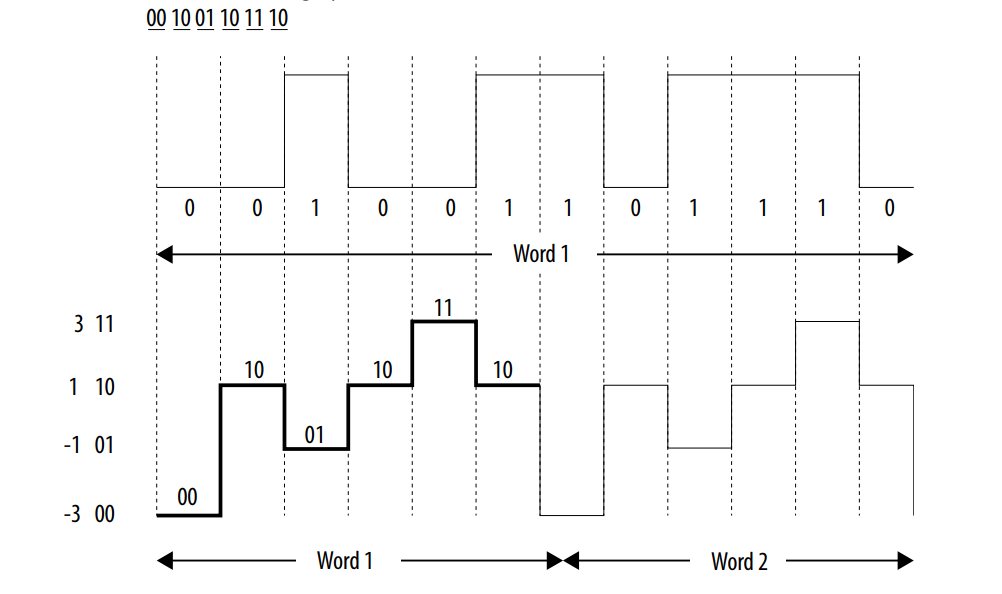

其实前面提到的三大变化当中,前两个变化是密切相关的,正是因为引入了PAM4编码方式,才让PCIe 6.0的数据传输速率再次翻倍的。采用PAM4信令后,由于使用4个信号电平,而不是传统的0/1两个电平,单个信号就能有四种编码(00/01/10/11)状态。这使得PAM4可以携带两倍于NRZ信令的数据。

不过,由于PAM4的电平更多,更容易受到噪声的影响,出现误码,因此,如果想让信号更加可靠的话,就需要辅以轻量级前向纠错(FEC)和循环冗余校验(CRC)方案,以减少误码率的增长。

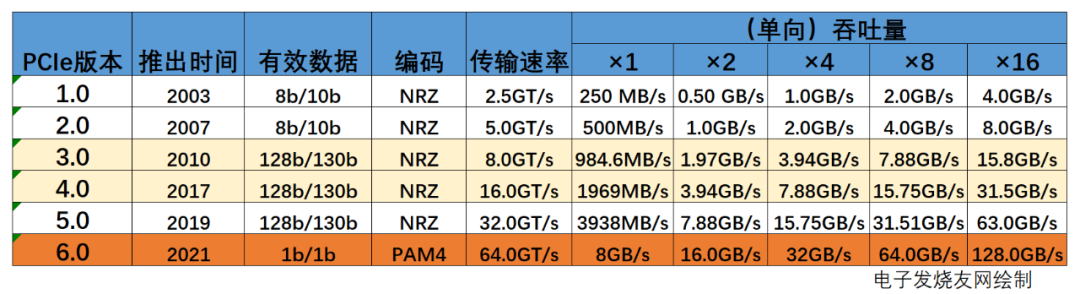

表:历代PCIe参数对比(数据来源:PCI-SIG)

标准每更新一次,传输速率就翻倍一次,PCIe6.0原始的传输速率为64GT/s,转换成吞吐量的话,单向吞吐量单条通道(Lane)为:64/8=8GB/s,这里除以8是为了将bit转换为Byte,也就是说PCIe 6.0 x16的单向吞吐量为128GB/s,双向为256GB/s。

当然,对于吞吐量其实是有一个计算公式的,以PCIe 3.0协议支持8.0GT/s为例,即每一条通道上支持每秒钟内传输8G个bit,PCIe 3.0的物理层协议中使用的是128b/130b的编码方案,即每传输128个bit,需要发送130个bit。因此,PCIe 3.0协议的每一条Lane支持的吞吐量就是8×128/130=7,877Gbps=984.6MB/s

流量控制单元(FLIT)编码方式,也是PCIe 6.0标准最大的变化之一,与物理层的PAM4不同,FLIT编码用于逻辑层,将数据分解为固定大小的数据包。

PCI-SIG认为 FLIT 编码在某种意义上也被向后移植以降低链路速率非常重要/有用。一旦在链路上启用 FLIT,链路将始终保持FLIT 模式,即使链路速率协商下降。因此,例如,如果PCIe 6.0 显卡要从64 GT/s (PCIe 6.0) 速率下降到2.5GT/s (PCIe 1.x) 速率以节省空闲时的电量,则链路本身仍将是在FLIT 模式下运行,而不是回到完整的PCIe 1.x 样式链接。这既简化了规范的设计(不必重新协商超出链路速率的连接),又允许所有链路速率受益于FLIT 的低延迟和低开销。

随着在PCIe 6.0中引入新的FLIT模式,TLP和数据层数据包(DLP)包头格式发生了变化,应用程序需要理解并正确处理这些变化。例如,对于PCIe 6.0,FLIT包含自己的CRC,因此数据链路层数据包(DLLP)和TLP不再需要像在PCIe 5.0和前几代中那样的单独CRC字节。此外,由于FLIT的大小固定,因此无需使用前几代(非FLIT模式)中的PHY层成帧令牌。与PCIe 5.0相比,这提高了带宽效率。

新特性带来的新挑战

根据PCI-SIG公布的信息,PCIe 6.0规范的主要有五大特性:

首先是传输速率,从PCIe 5.0的32GT/s扩展至64GT/s;

二是PCIe 6.0采用全新的PAM4,取代PCIe 5.0 NRZ,可以在单个通道、同样时间内封包更多数据,编码是一种1b/1b的编码方案。

三是引入了低延迟前向纠错(FEC)和相关机制,以改进带宽效率和可靠性。

四是支持FLIT模式。

五是PCIe 6.0可以兼容前面所有旧版本PCIe架构。

数据传输速率的翻倍,从32GT/s NRZ到64GT/s的PAM4信令,信噪比目标将更难达到,因为反射要差3倍。如何让设计的PCIe 6.0产品更加稳健,通道损耗更少,功耗更低,但性能却不降低,甚至更高呢?

新思科技给出了他们的解决方案,其面向PCIe 6.0的完整IP核解决方案包括了控制器、PHY核验证IP,可实现PCIe 6.0片上系统(SoC)设计的早期开发。面向PCIe 6.0的全新DesignWare IP核支持标准规范的最新功能,其中包括64GT/s PAM-4信号传输、FLIT模式和L0p功耗状态。该完整IP解决方案可满足高性能计算、AI和存储SoC在延迟、带宽和功耗效率方面不断提高的要求。

为了实现最低延迟并最大限度地提高所有传输规模的吞吐量,面向PCIe 6.0的DesignWare控制器采用MultiStream架构,可提供相当于Single-Stream设计2倍的性能。该控制器采用1024位架构,可让开发者在1GHz时序收敛的条件下实现64GT/s x 16的带宽。此外,该控制器还可在处理多个数据源以及使用多个虚拟通道时提供最佳流量。为了通过内置验证计划、序列和功能覆盖来加快测试平台的开发,面向PCIe的VC验证IP采用了本地SystemsVerilog/UVM架构,只需小量的工作即可完成集成、配置和定制。

其面向PCIe 6.0的DesignWare PHY IP可提供独特的自适应DSP算法,可优化模拟和数字均衡,从而最大限度地提高功耗效率,而不受通道影响。借助正在申请专利的诊断功能,PHY可实现接近零的链路关闭时间。面向PCIe 6.0的DesignWare PHY IP感知布局架构可最大限度地减少封装串扰,并支持针对x16链路的密集SoC集成。为基于ADC的架构采用优化数据路径可实现超低延迟。

此外,PCIe 6.0还引入了新电源状态,称为L0p 或 LOp。这是一种新的电源状态,能够以非破坏性方式为正常工作的链路节省电源。举例来讲,此电源状态下的 x4 链路可以确保只有一个通道工作,而其他三个通道进入低功率流。与任何其他低功耗状态一样,退出这种低功耗状态的延迟是一个值得关注的关键参数。

这种新的低功耗模式是对称的,这意味着TX和RX一起缩放,并且支持FLIT模式的重定时器也支持这种模式。在处于L0p期间空闲通道的PHY功耗预计与关闭通道时的功耗相近。

结语

虽然现在主流的应用还在PCIe3.0和PCIe 4.0,但我们看到在有些数据中心,以及新的GPU、CPU,或加速器开始采用PCIe 5.0了。PCIe 6.0带来的新特性,包括64GT/s的数据速率,采用具有吞吐量和延迟优势的 FLIT,以及新的低功耗状态L0p,实现了真正的带宽扩展来降低功耗,必然会给业界带来新的体验。

原文标题:解密PCle IP方案,让SoC集成更简单

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54441浏览量

469425 -

IP

+关注

关注

5文章

1885浏览量

156731 -

pcle

+关注

关注

0文章

35浏览量

6166

原文标题:解密PCle IP方案,让SoC集成更简单

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

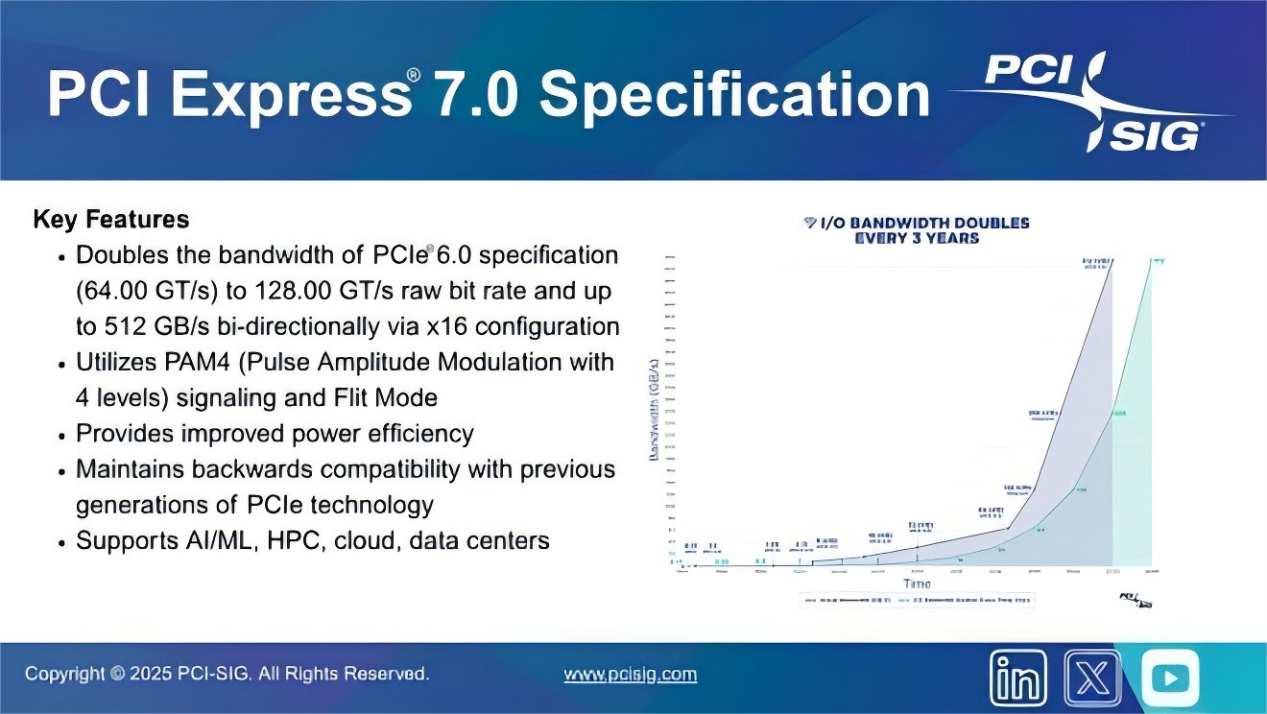

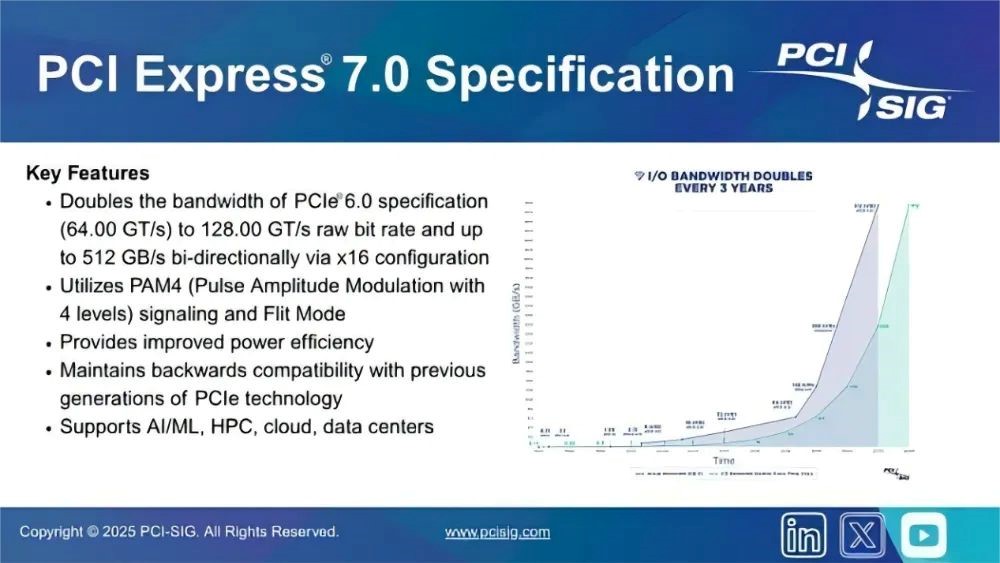

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

【PCIe 6.0 连载 · 中篇】从设计到实现:高速信号如何做到又快又稳?

【PCIe 6.0 连载 · 上篇】64GT/s 时代来临:AI与算力爆发下的高速互联新基石

CPX:借助CPC/CPO实现AI扩展与扩容| Samtec受邀参与Keysight PCIe研讨会并分享

加速PCIe 5产品设计和测试

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

曙光存储超级隧道技术助力应对PCIe 6.0时代

PCIe 4.0/5.0仍是主流!三家SSD企业抢滩高性能存储市场,新品相继亮相

PCIe 6.0的新变化与新挑战

PCIe 6.0的新变化与新挑战

评论