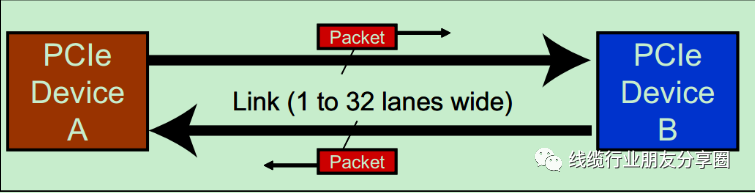

随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

如今PCIe 7.0 时代已经到来(PCIe 7.0 标准已在修订?全面普及可能要到2028年),实际商用主流PCIe4.0 ,其发展使服务器硬件间信息交互速度再次跃升,但随之而来的是不可忽视的信号衰减问题,今天我们科普下PCIe简介及引脚定义。

PCIe发展历程

2001年,非营利组织PCI-SIG召集了英特尔、AMD、博通、IBM、微软等厂商提出了PCIe(Peripheral Component Interconnect Express)新总线标准,此举是为取代旧的PCI,PCI-X和AGP总线标准。

2003年-2010年:PCIe 1.0 - PCIe 3.0

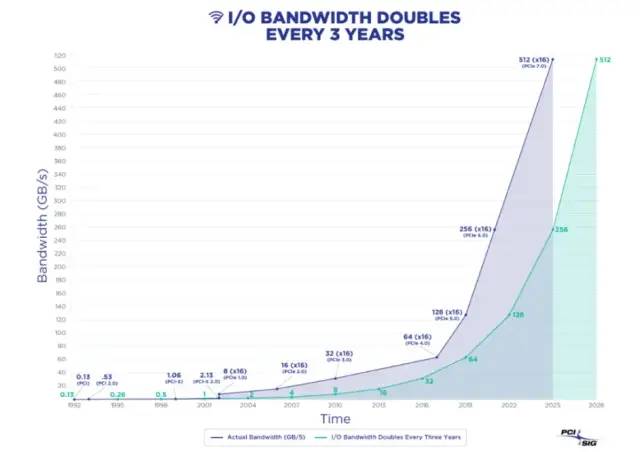

PCIe 技术始于 2003 年,PCIe 1.0数据速率为 2.5GT/s,PCIe 2.0 规范在 2006 年将数据速率翻了一番,达到 5.0 GT/s。前两代 PCIe 技术使用 8b/10b 编码,产生了 25% 的编码开销。

2010年,PCIe 3.0 将数据速率提高到了 8.0 GT/s ,并采用了新的 128b/130b 编码机制,使每个引脚的带宽比 PCIe 2.0 翻了一番。新的编码机制通过采用三个随机位翻转检测的故障模型确保了高可靠性,并具有多种创新方法来执行数据包的物理层帧,同时保留从上层发送的数据包格式。 PCIe 3.0规范还加入了一些增强信号指令,以及对数据完整性的优化,包括发送器和接收器以及拓扑结构等,再加上重新优化的PLL、数据通道等。

此外,PCIe 3.0标准的更新版本PCIe 3.1在2014年11月发布,加入了包括电源管理、性能优化和功能拓展等多项改变,当然本质的数据传输能力没有变化。2010年推出PCIE3.0,32(x16),可以看到之后几年一直处于PCIE3.0时代。直到2017年才推出PCIE4.0,64(x16),2017年10月:16.0 GT/s的PCIe 4.0 依照PCIe 1.0到PCIe 3.0的更新节奏来看,相对于2010年发布的PCIe 3.0,PCIe 4.0规范应该要在2014或2015年发布,但实际上,PCI-SIG直到2017年中才发布PCIe 4.0,较预期晚2、3年,这连带也推迟了应用的时间。

PCIe 4.0花费了7年时间将数据速率从 8.0 GT/s 翻倍到 16.0 GT/s (每条通道大约 2GB/s,或总共 64GB/s)。PCIe 4.0 保留了相同的 128b/130b 编码方案,PCIe 标准通过软件和机械接口保持与旧规范和新规范的向后和向前兼容性。也就是说,PCIe 3.0卡可以在支持PCIe 4.0的主板上工作,PCIe 4.0卡也可以在PCIe 3.0主板上工作,但受限于PCIe 3.0接口的性能。

2019年推出PCIE5.0标准,2019 年 5 月:32.0 GT/s 的 PCIe 5.0 过去几年,计算领域发生了重大变化,云计算、边缘计算以及人工智能、机器学习和分析等应用引发了对更快的数据处理和移动的需求。随着计算和内存容量呈指数级增长,我们需要以更快的节奏维持 I/O 带宽翻倍,以跟上新兴应用程序的性能。例如,400 Gb(或双 200 Gb)网络需要 32.0 GT/s 的 x16 PCIe 来维持带宽。

这就要求在PCIe 4.0架构之后不到两年的时间里发布一个完全向后兼容的PCIe 5.0——这对于一个标准来说是一个重大的成就,去年10月英特尔发布12代酷睿处理器,支持PCIe5.0标准,相信PCIE5.0消费级产品也在不久后面市。AMD抢先NVIDIA 首发支持PCIe 5.0,从 PCIe 4.0 到 PCIe 5.0 规范的演变主要是速度升级。128b/130b 编码是将带宽扩展到更高数据速率的协议支持,在PCIe 3.0和PCIe 4.0规范中已经内置了这种编码。

通道损耗扩展到 36 dB,同时对连接器进行了改进,以最大限度地减少频率范围增加所带来的损耗。PCIe 5.0 架构的增强功能之一是对备用协议的内置支持。随着 PCIe 技术发展成为带宽最高、能效最高和部署最广泛的接口,某些用途需要额外的协议,例如,某些加速器和智能网卡可以缓存系统内存并将其内存映射到系统内存空间,以便在PCIe协议之外进行高效的数据交换。

同样,系统内存正在迁移到 PCIe PHY,因为它提供了高能效的高带宽和低延迟解决方案。PCI-SIG 预计 PCIe 4.0 和 PCIe 5.0 将在一段时间内共存,PCIe 5.0 用于对吞吐量要求高的高性能需求,例如用于 AI 工作负载和网络应用程序的 GPU。因此,PCIe 5.0 将主要用于数据中心、网络和高性能计算 (HPC) 企业环境,而不那么密集的应用(如台式机应用)将适用于 PCIe 4.0。

PCIe 6.0正式发布!有史以来变化最大一次:x16带宽增至256GB/s;2022年1月11日,PCI-SIG正式发布了PCIe 6.0最终版本1.0,从技术上来说,PCIe 6.0是PCIe问世近20年来,变化最大的一次。 PCIe 6.0 规范目标要求 根据PCI-SIG的介绍,PCIe 6.0主要有三大变化:数据传输速率从32GT/s翻倍至64GT/s;编码方式从NRZ 信令模式转向PAM4信令模式;从传输可变大小TLP到固定大小FLIT.

新技术提供市场导向,市场需求反向推动新技术的发展。面对人工智能、物联网、云端数据存储以及最近火热的汽车等领域,交互时代需要更快、更高效的接口传输数据,所以我们可以看到每一代PCIE推出都带来翻倍的带宽。新技术产品的推出,都优先应用于高性能计算服务器、云端数据存储等大型服务器领域。

消费级市场推出PCIE新技术产品,需周边配套产品支持以及成本等方面考虑,所以消费领域的应用往往要慢两至三年,在实际应用方面,刚刚发布不久的PCIe 6.0目前自然还尚无具体进展,现在主流的应用还在PCIe 3.0和PCIe 4.0,不过PCIe 5.0已经进入初步的推广期,自2021年底开始,便开始有厂商推出支持PCIe 5.0的高速网卡与SSD产品,并且一些新的GPU、CPU开始采用PCIe 5.0了。

这也让当前的PCIe应用环境形成了3.0、4.0、5.0、6.0“四代同堂”的奇特现象,并且仍将持续一段时间。 整体而言,新一代PCIe 5.0与PCIe 6.0已经崛起,并陆续投入应用,PCIe 6.0带来的新特性,包括64GT/s的数据速率、PAM4编码方式、具有吞吐量和延迟优势的 FLIT等等,必然会更好地推动行业发展。

审核编辑 :李倩

-

PCI

+关注

关注

5文章

689浏览量

134505 -

总线

+关注

关注

10文章

3060浏览量

91869 -

PCIe

+关注

关注

16文章

1479浏览量

88931 -

引脚

+关注

关注

16文章

2120浏览量

56027 -

并行总线

+关注

关注

0文章

30浏览量

13898

原文标题:PCIE发展史科普篇

文章出处:【微信号:线缆行业朋友分享圈,微信公众号:线缆行业朋友分享圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

三菱伺服电机的编码器引脚的定义

探索TS2PCIE412:高性能PCIe开关的技术剖析

有源晶振引脚定义与区别

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

PCIe协议分析仪能测试哪些设备?

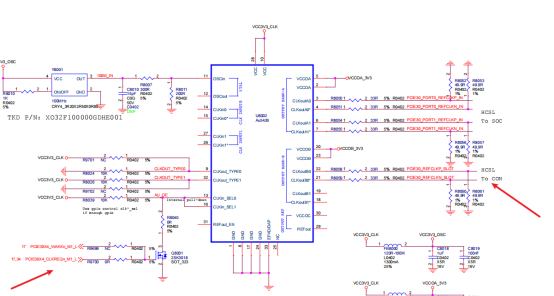

PCIe简介及引脚定义

PCIe简介及引脚定义

评论