锁相环电路

锁相环

2009-09-25 14:28:39 7723

7723

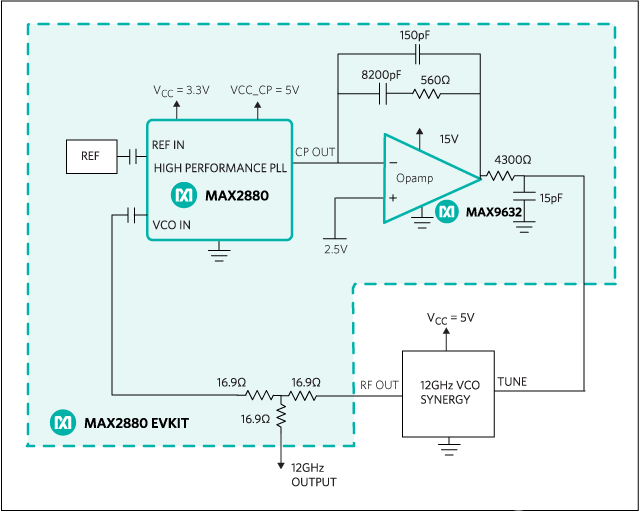

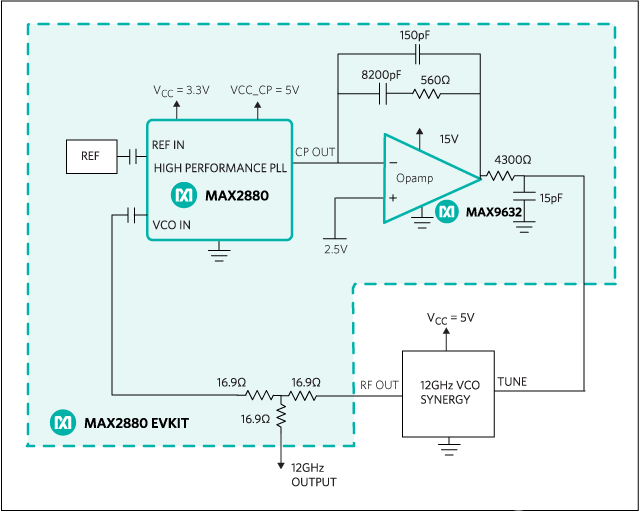

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)组成。

2018-12-10 10:02:53 1718

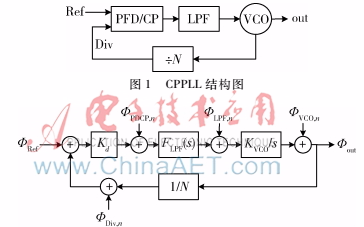

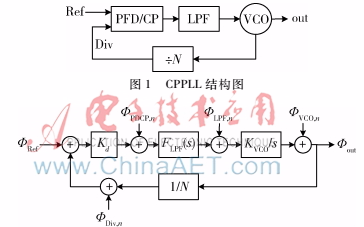

1718 数字锁相环频率合成系统的工作原理是:锁相环对高稳定度的基准频率(通常由晶体振荡器直接或经分频后提供)进行精确锁定,环内串接可编程的分频器,通过编程改变分频器的分频比,使环路总的分频比为N(可通过编程改变),从而环路稳定的输出 N倍的基准频率,而整个程序和系统的控制是要由CPU来完成的。

2020-07-23 16:47:49 2086

2086

大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 7303

7303

Controlled Oscillator:VCO)。有了这三个模块的话,最基本的锁相环就可以运行了。但我们实际使用过程中,锁相环系统还会加一些分频器、倍频器、混频器等模块。(这一点可以类比STM32的最小系统和我们实际使用STM32的开发板)

2023-09-03 12:01:12 3021

3021

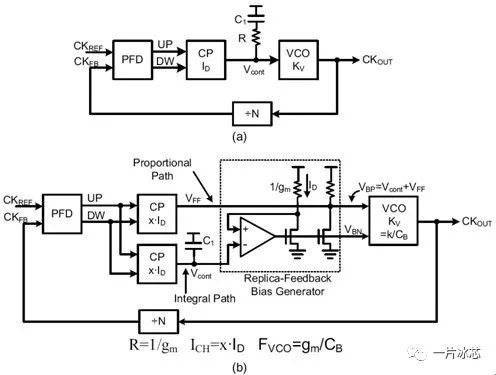

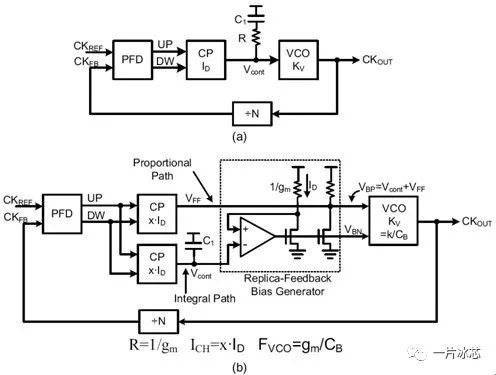

传统锁相环,环路带宽、相位裕度与电荷泵电流、滤波器RC参数、分频比、参考频率等参数相关。

2023-10-30 16:47:58 2639

2639

不仅包括整数分频,小数分频VCO外置产品,还包括集成了VCO的产品,从而大大简化您的设计,降低系统成本。 整数分频PLL小数分频PLL单环PLL双环PLL集成VCO的PLL快速锁定PLL高电压电荷泵PLL附件锁相环常见问题解答.pdf518.7 KB

2018-10-31 15:08:45

不仅包括整数分频,小数分频VCO外置产品,还包括集成了VCO的产品,从而大大简化您的设计,降低系统成本。附件锁相环常见问题解答.rar.zip492.4 KB

2018-11-06 09:03:16

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

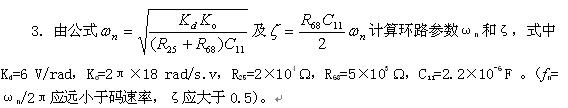

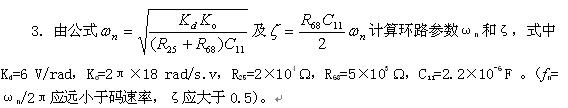

、压控振荡器(VCO) 四、环路滤波器(LPF) 五、固有频率ωn和阻尼系数x 的物 理意义 六、同步带和捕捉带 •第二部分:锁相环实验 •实验一、PLL参数测试 •一、压控灵敏度KO的测量 •二

2011-12-21 17:35:00

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

Actel FPGA PLL锁相环的最大能达到几倍频几分频?我在网上查了一下有人说是20倍频,10分频,但是我没有在芯片手册里面找到资料,想要确认一下。

2014-12-04 11:25:15

LabVIEW锁相环(PLL) 锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环

2022-05-31 19:58:27

`可编程锁相环(PLL)解决方案有多种尺寸和类型可供选择。 PLL以整数N或小数N形式提供同时根据带宽利用无源或有源环路滤波器。 可以通过3线串行接口对其进行快速编程同时提供非常低的杂散抑制和较小

2021-04-03 17:00:58

进行捕获?4常见的倍频锁相环结构,设输出时钟clk_out的频率为输入时钟clk_in的n倍;输出时钟clk_out的分频信号clk_f与输入时钟clk_in的相位差是恒定的,但能保证输出时钟

2018-09-18 11:14:35

全数字锁相环,在本文中以该芯片为参考进行设计、分析。ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。K变模计数器和脉冲加减电路的时钟分别为Mfc

2010-03-16 10:56:10

ADF4351锁相环介绍及相关硬件设计ADF4351是ADI公司推出的一款集成VCO的锁相环芯片。其输出频率范围可配置为35MHZ到4400MHZ,这取决于参考频率和寄存器配置。其内部包括整数N

2022-01-11 07:28:51

该电路是低噪声微波小数N分频PLL的完整实现方案,以 ADF4156 作为核心的小数N分频PLL器件。使用 ADF5001 外部预分频器将PLL频率范围扩展至18 GHz。采用具有适当偏置和滤波

2019-08-20 06:44:35

本帖最后由 gk320830 于 2015-3-9 20:38 编辑

最近在用adf 4001做一个锁相环,环路配置好后发现锁定不了,电荷泵cp 输出一直在扫描,检查芯片内部的配置,也没发现什么问题,分频输出也是正常的,哪位高手用过这个芯片,帮我分析分析吧,期待中。。。

2010-09-14 08:52:16

中提到的滤波。第3步提到R/2计数器而后在第4步用cnt的状态翻转lowclk来实现R分频,是为了强调输出的lowclk的展空比为50%。数字锁相环设计总思路:数字锁相环完成的功能就是利用clock从

2012-01-12 15:29:12

fpga中的用锁相环产生时钟信号相比于用计数器进行分频有哪些优点,看fpga中锁相环的结构,其前期的输入信号和后期的输出信号不也是通过计数器进行分频实现的吗

2014-10-06 10:46:05

模拟锁相环与数字锁相环的主要区别在哪里?

2023-04-24 10:48:52

本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2021-04-20 06:00:37

根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基

2008-08-15 12:36:19 101

101 一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 127

127 智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 72

72 锁相环电路的设计:

2009-07-25 17:05:36 0

0 锁相环设计举例:锁相环设计主要包括:确定所需环的类型,选择适当的带宽,指出希望的稳定度。下面将举例说明要满足这些设计要求而常用的基本方法。

2009-09-05 08:51:42 105

105 在分析锁相环工作原理的基础上,利用传递函数法建立了锁相环跟踪误差的二阶等效模型,并对锁相环的动态频相跟踪特性进行了理论分析.利用MATLAB构建了锁相环的仿真

2010-03-01 18:14:11 32

32 议程PLL介绍及小数分频锁相环的优点小数分频锁相环的错误使用小数分频锁相环详解参考杂散及如何减少杂散总结

2010-05-28 14:58:36 0

0 锁相环被广泛应用于电力系统的测量和控制中。介绍了一种新型的基于比例积分控制逻辑的全数字锁相环。通过对其数学模型的分析,阐述了该锁相环的各项性能指标与设计参数的

2010-07-02 16:54:10 30

30 锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 5484

5484 锁相环原理及图解分析

标签/分类:

2007-08-21 14:57:34 7929

7929

锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 2529

2529

实验 模拟锁相环与载波同步

一、 实验目的

1. 掌握模拟锁相环的工作原理,以及环路的锁定状

2009-04-01 08:57:32 9552

9552

实验五 数字锁相环与位同步

一、 实验目的

1. 掌握数字锁相环工作原理以及触发式数字锁

2009-04-01 09:27:45 6242

6242

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1760

1760

摘要: 从整个应用系统的角度,理解和分析PLD内部锁相环;在此基础上,深入剖析锁相环的相移结构,同时用这个技术解决系统设计难题。

关键

2009-06-20 12:40:02 1010

1010

锁相环(PLL),锁相环(PLL)是什么意思

PLL的概念

我们所说的PLL。其

2010-03-23 10:47:48 6368

6368 集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 956

956 数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 6110

6110 模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 6264

6264 采用PLL(锁相环)IC的频率N(1~10)倍增电路

电路的功能

很多电路

2010-05-12 10:51:53 2237

2237

目录: 基础理论 环路的性能 电路实解 锁相环在手机中的应用

2011-05-02 11:05:01 474

474 频率跟踪的 锁相环电路 由专用锁相芯片CD4046和分频芯片CD4040组成,以实现工频信号的锁相倍频,分频比为1/64。在工频信号恰好为50 Hz的情况下,该电路的锁相倍频频率为5064=3 200 Hz,相

2011-10-26 11:17:47 9369

9369

锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

该电路是低噪声微波小数N分频PLL的完整实现方案,以 ADF4156 作为核心的小数N分频PLL器件。使用 ADF5001 外部预分频器将PLL频率范围扩展至18 GHz。

2011-10-26 15:02:22 1852

1852

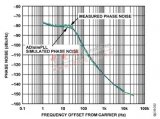

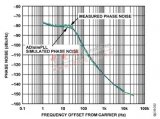

利用锁相环的等效噪声模型,重点分析电荷泵锁相环系统的相位噪声特性,得出系统噪声特性的分布特点以及与环路带宽的关系。

2012-11-22 10:44:47 23975

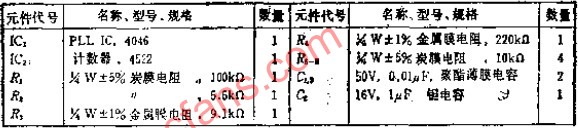

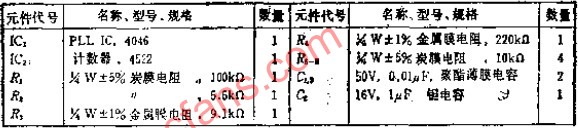

23975 本材料是基于单片机分频的锁相环测试系统电路图。

2015-10-28 13:47:49 9

9 有关锁相环的部分资料,对制作锁相环有一定的帮助。

2015-10-29 14:16:55 70

70 锁相环系统中的VCO的分析与设计。

2016-04-29 16:50:26 9

9 双向遥控钥匙(RKE)系统为用户提供安全和便利。对于设计师,一个复杂的IC阵列提供完整的收发器功能,利用未经授权的ISM频段。其中,sub-GHz收发器集成电路从模拟设备,飞思卡尔半导体和集成功能的小数N分频锁相环在先进的双向RKE系统设计更大的灵活性。

2017-07-11 09:32:07 0

0 一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 19

19 电路功能与优势 该电路是低噪声微波小数N分频PLL的完整实现方案,以 ADF4156 作为核心的小数N分频PLL器件。使用 ADF5001 外部预分频器将PLL频率范围扩展至18 GHz。采用

2017-11-25 12:37:01 498

498

直接影响到逆变器的性能。如何利用DSP等数字芯片,设计出一个可以克服各种电网畸变及故障的软件锁相环,是当今科学研究的热点问题。 本文首先论述的锁相环技术的发展历史及前景,简单阐述了传统的锁相环技术,指出了它们的缺点并

2017-12-08 11:12:07 25

25 介绍一种2.4 GHz的低噪声亚采样锁相环。环路锁定是利用亚采样鉴相器对压控振荡器的输出进行采样。不同于传统电荷泵锁相环,由于在锁定状态下没有分频器的作用,由鉴相器和电荷泵所产生的带内噪声不会被放大

2018-06-07 15:58:00 11426

11426

本文将从小数锁相环的需求,Delta-Sigma 小数锁相环的逻辑以及Delta-Sigma的特性三方面展开。

2019-01-01 08:45:00 9244

9244

EngineerIt-锁相环应用中的环路带宽

2019-04-15 06:07:00 13946

13946

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2020-11-03 14:55:49 16784

16784

UG-873:评估ADF4355-3小数/整数N锁相环频率合成器

2021-04-28 14:35:35 5

5 UG-1404:评估集成小数N锁相环和压控振荡器的ADMV4420,K波段下变频器

2021-04-29 15:58:03 5

5 一种新型的采用电流转向电荷泵的快速锁定小数分频锁相环介绍。

2021-05-08 10:55:08 5

5 UG-804:评估ADF4355-2小数/整数N锁相环频率合成器

2021-05-10 08:26:33 9

9 UG-1025:评估ADRF6821 450 MHz至2800 MHz,集成小数N锁相环和压控振荡器的DPD RFIC

2021-05-16 13:15:14 1

1 UG-485:ADF4153A小数N锁相环频率合成器评估板

2021-05-16 13:22:43 9

9 UG-742:评估集成小数N锁相环和压控振荡器的ADRF6720-27宽带正交调制器

2021-05-16 14:59:18 11

11 UG-652:评估集成小数N锁相环和压控振荡器的ADRF6820-a 695 MHz至2700 MHz正交解调器

2021-05-17 12:50:56 3

3 ADRF6720-27:集成小数N锁相环和压控振荡器的宽带正交调制器

2021-05-18 20:43:41 10

10 ADRF6655:集成小数N锁相环和压控振荡器的宽带上/下变频混频器

2021-05-24 12:59:25 2

2 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 15826

15826 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2022-05-10 14:25:19 8969

8969 锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

2022-07-03 15:23:57 2648

2648 锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和锁相环专家导航器件选择以及每种不同应用固有的权衡取舍。

2022-12-23 14:03:54 6671

6671

本应用笔记详细介绍了集成外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880)、基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)组成。

2023-01-16 11:27:08 2339

2339

锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

2023-01-31 16:31:12 4097

4097 模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 6625

6625 锁相环电路,是调频电路的重要组成之一,锁相环电路的原理的认识是DDS学习的一个重点之一。

2023-07-24 15:37:05 4645

4645

核芯互联发布射频锁相环CLF4371,CLF4371是一款低噪声宽频段的锁相环,支持整数模式和小数模式,可以工作在-40~85℃全温度范围。芯片采用3x3mm 超小型BGA封装,可以为用户节省面积

2023-08-29 21:53:50 2317

2317

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 4879

4879 锁相环频率合成器的优缺点 锁相环频率合成器,又称为PLL(Phase Locked Loop),是一种广泛应用的电路,能够将输入信号的频率合成为电路所需要的频率,并且能够实现对信号的相位和频率

2023-09-02 14:59:33 3701

3701 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 5118

5118 锁相环PLL和锁频环FLL的区别 锁相环(PLL,Phase Locked Loop)和锁频环(FLL,Frequency Locked Loop)是两种常用于信号调节和数据传输的控制回路。虽然它们

2023-09-02 15:06:39 12513

12513 基本PLL锁相环、整数型频率合成器和分数型频率合成器。下面将详细介绍这三种模式的作用和特点。 第一种:基本PLL锁相环 基本PLL锁相环是PLLf工作的最基本形式,它主要由比较器、低通滤波器、VCO和分频器组成。其基本工作原理是将输入信号和VCO输出的信号进行

2023-10-13 17:39:48 5284

5284 软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办? 锁相环(PLL)是一种用于在电路中生成稳定频率的技术。它是在1960年代开发的,并被广泛应用于通信、雷达、卫星技术等领域中。锁相环的主要作用

2023-10-13 17:39:58 3085

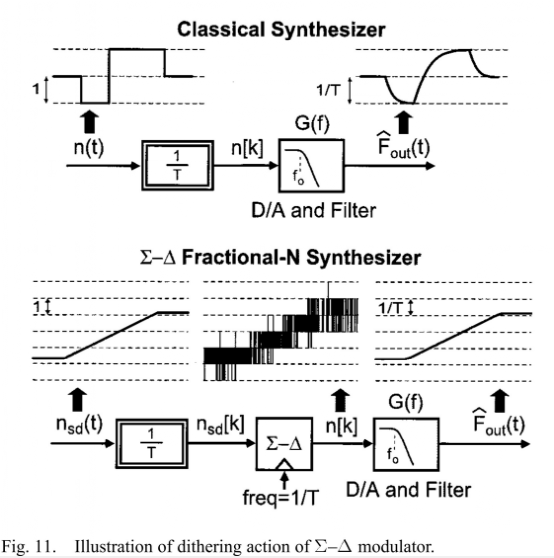

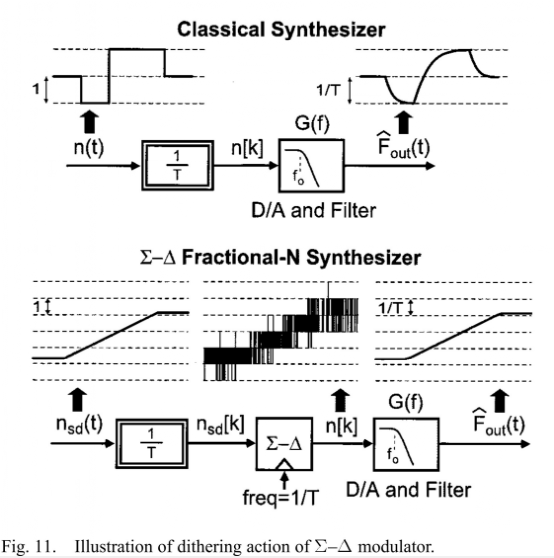

3085 为了理解Σ-Δ调制器在频率综合器中究竟引起了啥影响,图11可以比较好的说明。需要指出的是,图11中把分频比的变化看作一个连续信号

2023-10-25 14:36:37 2118

2118

锁相环在相位检测中的应用 锁相环(PLL)是一种电子技术中广泛应用的电路,用于调整一个输出信号的相位来精确匹配一个参考信号。锁相环在各种不同的应用领域都有着广泛的应用,例如通信系统、控制系统、测量

2023-10-29 11:35:19 1738

1738 当锁相环无法锁定时,该怎么处理的呢?如何解决锁相环无法锁定? 锁相环作为一种常见的电路设计,具有广泛的应用领域。然而,在一些情况下,由于种种原因,锁相环可能无法正常锁定,这时需要进行一系列的测试

2023-10-30 10:16:33 3645

3645 电子发烧友网站提供《锁相环基本结构及原理.pdf》资料免费下载

2023-11-29 11:23:37 3

3 锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分频

2024-01-31 15:24:48 5373

5373 锁相环到底锁相还是锁频? 锁相环(PLL)是一种常用的控制系统,主要用于同步时钟。它通过将被控信号的相位与稳定的参考信号进行比较,并产生相应的控制信号,使被控信号的相位保持与参考信号同步。这种控制

2024-01-31 15:25:00 4017

4017 2024年07月09日,一站式定制芯片及IP供应商——灿芯半导体(上海)股份有限公司(灿芯股份,688691)宣布成功研发出一款通用高性能小数分频锁相环(fractional-N PLL)IP,支持

2024-07-09 14:13:58 62633

62633 锁相环(Phase Locked Loop, PLL)相位噪声是评估锁相环性能的重要指标之一,它描述了输出信号相位的不稳定性。相位噪声的存在会直接影响系统的性能,如降低信号的信噪比、增加误码率、影响雷达系统的目标分辨能力等。以下将详细分析锁相环相位噪声的影响因素,并从多个方面进行归纳和总结。

2024-07-30 15:31:57 4497

4497 锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的反馈控制系统,主要用于频率合成和相位同步。本文将从锁相环的工作原理、基本组成、应用案例以及设计考虑等方面进行详细阐述,以帮助读者全面理解这一重要技术。

2025-02-03 17:48:00 2320

2320 ADF4155结合外部环路滤波器、外部压控振荡器(VCO)和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

ADF4155能够与外部VCO器件配合使用,工作频率高达8 GHz。 高分辨率可编程模块允许精确频率合成,误差为0 Hz。

2025-04-25 14:15:12 859

859

ADF4151结合外部电压控制振荡器(VCO)、环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

它能够与外部VCO器件配合使用,且与ADF4350尺寸

2025-04-25 15:15:29 933

933

Analog Devices ADF4382x小数N分频锁相环 (PLL) 是一款高性能、超低抖动、小数N分频锁相环 (PLL)。它集成了压控振荡器 (VCO),是5G或数据转换器时钟应用生成

2025-06-04 11:15:21 862

862

电子发烧友App

电子发烧友App

评论