核芯互联发布射频锁相环CLF4371,CLF4371是一款低噪声宽频段的锁相环,支持整数模式和小数模式,可以工作在-40~85℃全温度范围。芯片采用3x3mm 超小型BGA封装,可以为用户节省面积,该产品也支持提供KGD以进一步节省面积。

芯片集成了4 个VCO,能够覆盖4~8.8GHz频段。通过输出分频器(分频比2,4,8,16,32,64可配),可以支持62.5M~4GHz频段。通过2倍频电路,可以支持 8~18GHz频段,再通过2倍频电路,可以支持18~35.2GHz频段。输入频率范围 100kHz~300MHz,支持差分输入和单端输入,支持方波输入和正弦波输入。同时,输入频率可以进行2倍频,或1~1023分频等供鉴频鉴相器(PFD)工作。电荷泵(CP)电流0.3mA~4.8mA 可配, 0.3mA/step。锁相环反馈通路多模分频器(MMD)分频比支持 4~65535。

主 要 参 数

输出频率范围:62.5 MHz~35.2 GHz

输入频率范围:100kHz~300 MHz

带内归一化噪底: -230 dBc/Hz

归一化 1/f 噪底: -126 dBc/Hz

63 fs for 4 GHz output

67 fs for 8 GHz output

90 fs for 16 GHz output

120 fs for 32 GHz output

参考杂散:-80 dBc

锁定温度范围:-40~+85℃

BoM 单一工作电压:3.3 V, 无需板上低噪声 LDO,

支持差分和单端输出模式

电流:

175mA@Pout=0dBm for 4 GHz output

350mA@Pout=0dBm for 32 GHz output

封装尺寸:3mm×3mm BGA

-

射频

+关注

关注

101文章

5361浏览量

165860 -

锁相环

+关注

关注

35文章

551浏览量

87254 -

ldo

+关注

关注

34文章

1763浏览量

152030 -

核芯互联

+关注

关注

0文章

18浏览量

1644

原文标题:核芯互联发布62.5MHz ~35.2GHz小数分频锁相环CLF4371

文章出处:【微信号:gh_0dbe96735e9d,微信公众号:核芯互联】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STM32L072用内部时钟通过锁相环倍频到主频32MHz后,功耗很大怎么解决?

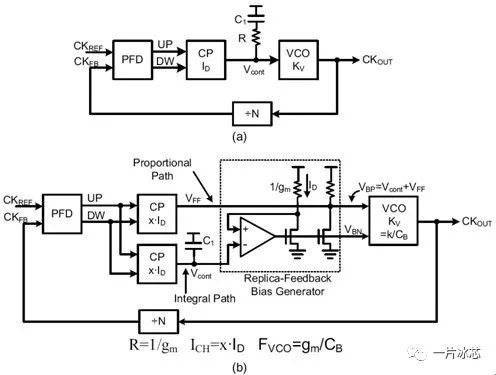

锁相环整数分频和小数分频的区别是什么?

AD9779内部锁相环无法锁定怎么解决?

PLL原理及主要技术指标

核芯互联发布62.5MHz ~35.2GHz小数分频锁相环CLF4371

核芯互联发布62.5MHz ~35.2GHz小数分频锁相环CLF4371

评论