锁相环整数分频和小数分频的区别是什么?

锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分频和小数分频两种方式。本文将详细探讨整数分频和小数分频的区别。

一、整数分频

整数分频是指将输入信号的周期或频率直接除以整数N,生成一个输出信号。整数N通常是一个大于1的正整数。整数分频的主要特点如下:

1. 简单可靠:整数分频的计算和处理都是基于整数,不需要进行复杂的计算和操作。这种简单性使整数分频的电路设计相对容易,且其性能较为稳定和可靠。

2. 效果明显:整数分频可以将输入信号的频率显著降低或提高,达到适配不同应用的要求。例如,将输入信号的频率降低后,可以用于减小电路功耗、改善噪声特性等。

3. 输出稳定:整数分频的输出信号的频率是输入信号频率的商,因此其输出频率在理论上是稳定的。这种稳定性使得整数分频在某些对频率要求较高的应用中非常实用,例如通信系统、音频处理等。

4. 频率选择受限:由于整数分频只能将频率进行整数倍的变化,因此其输出信号的频率选择性受到限制。当输入信号的频率与所需输出频率的整数倍存在较大差距时,整数分频不能满足要求。

二、小数分频

小数分频是指将输入信号的周期或频率按照一个小数分频因子进行分频,生成一个非整数倍的输出信号。小数分频的主要特点如下:

1. 精确灵活:小数分频可以实现更加精确、灵活的频率变换。分频因子中的小数部分可以实现相当精细的调整,使得输出频率能够准确地适配所需应用。

2. 高频选择范围广:小数分频可以实现更大范围的频率变化。通过合适的分频因子,输入信号的频率可以在很大的范围内进行升高或降低,提供了更多应用场景的选择。

3. 扩大倍频系数:小数分频可以将输入信号的频率扩大至更高的倍频,以满足高频应用的需求。这在一些射频通信、雷达等系统中非常重要。

4. 计算复杂度高:小数分频需要进行复杂的计算和操作,包括除法和乘法等运算。这要求设计和实现小数分频的电路存在一定的挑战,更高的计算复杂度可能导致功耗增加。

三、整数分频和小数分频的应用差异

整数分频和小数分频由于其不同的特点,适用于不同的应用场景:

1. 整数分频在一些对频率要求非常高的应用中得到广泛应用,例如通信系统、音频处理等。整数分频能够提供稳定、可靠的频率转换,且操作简单,适合于周期性精确信号的处理。

2. 小数分频则更适用于那些需要频率灵活精确调整的应用,例如射频通信系统、调频广播、音视频处理等。小数分频可以提供更大范围的频率变换和扩大倍频系数的功能,可以实现更加精细的频率调整。

综上所述,整数分频和小数分频是锁相环中常用的两种分频方式,它们在处理频率转换和信号同步的过程中具有各自的特点和应用场景。

-

锁相环

+关注

关注

36文章

637浏览量

91300 -

小数分频

+关注

关注

0文章

7浏览量

6771 -

时钟信号

+关注

关注

4文章

510浏览量

30080

发布评论请先 登录

高性能低噪声锁相环LTC6948:设计与应用全解析

PDRO还是小数分频频率合成器?聊一聊低相噪本振选型时踩过的坑和一点点心得

音响中软件分频和硬件分频区别解析以及对音质和成本的影响

LMX2487 高频双锁相环频率合成器技术文档总结

TRF3761系列整数分频锁相环(PLL)集成压控振荡器(VCO)技术文档总结

TRF3761系列整数分频锁相环(PLL)集成压控振荡器(VCO)技术文档摘要

TRF3761系列整数分频锁相环(PLL)集成压控振荡器(VCO)技术手册总结

Analog Devices Inc. ADF4382x小数N分频锁相环 (PLL)数据手册

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

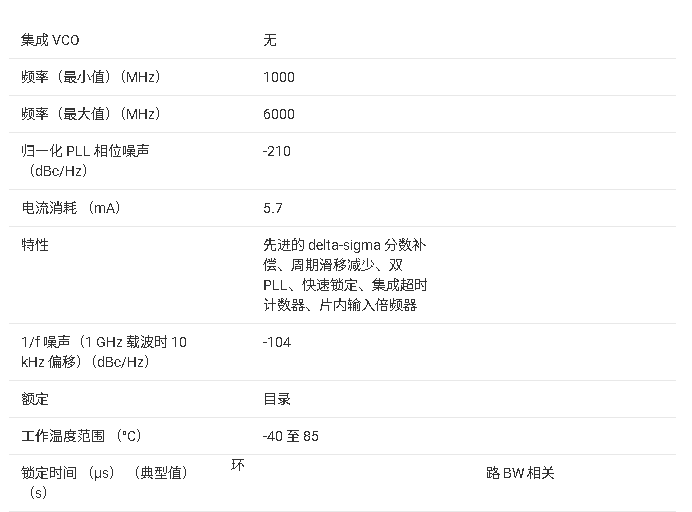

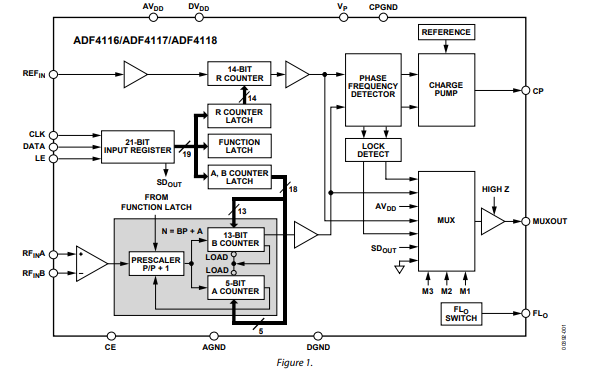

ADF4116/ADF4117/ADF4118单通道、整数N分频550MHz PLL技术手册

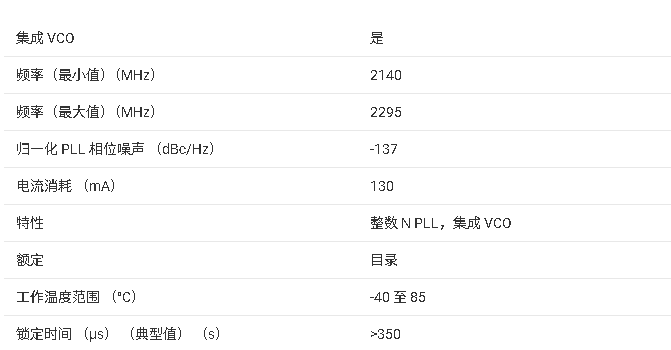

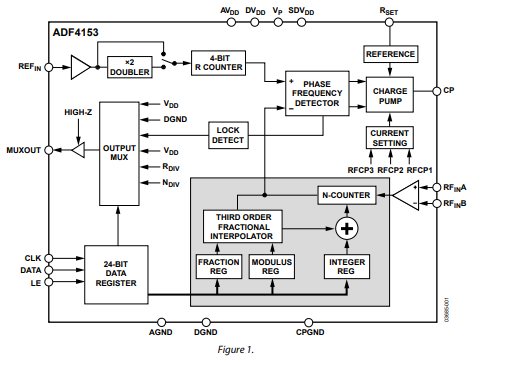

ADF4153小数N分频频率合成器技术手册

ADF4206/ADF4208双通道、整数N分频1.1GHz/2.0 GHz PLL技术手册

锁相环整数分频和小数分频的区别是什么?

锁相环整数分频和小数分频的区别是什么?

评论